Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

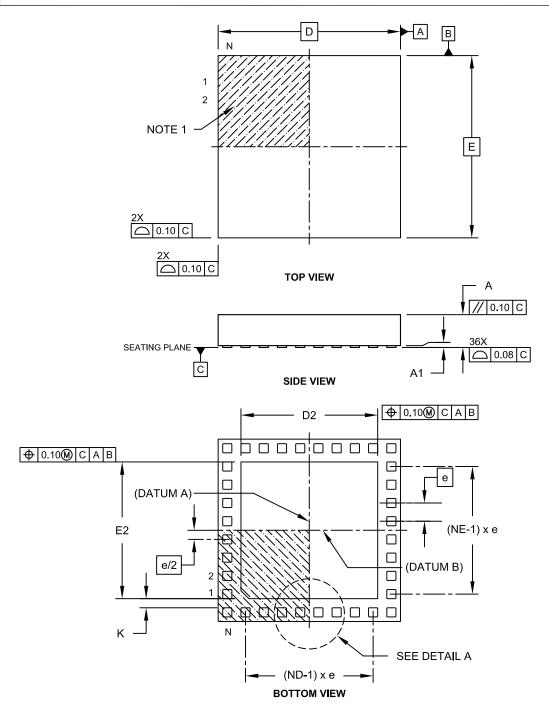

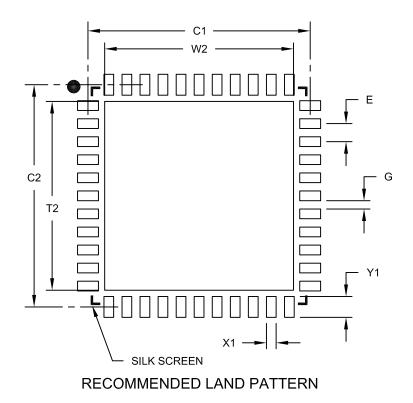

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9×9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mc506t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4         | -16:  | QEI1   | REGR                                      |          | P FOR d    | SPIC33E    | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY    | 1      |        |        | r             |

|-----------------|-------|--------|-------------------------------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14                                    | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                                         | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN                                    |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | _                                         | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                                           |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        | POSCNT<31:16> 0000                        |          |            |            |          |          |             |        |        |            |          |        |        |        |        |               |

| POS1HLD         | 01CA  |        |                                           |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC  |        |                                           |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE  |        |                                           |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0  |        |                                           |          |            |            |          |          | INTTMR<31:  | 6>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDL        | 01D2  |        | INT HMR<31:16> 0000<br>INT HLD<15:0> 0000 |          |            |            |          |          |             |        |        |            |          |        |        |        |        |               |

| INT1HLDH        | 01D4  |        |                                           |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                                           |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                                           |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                                           |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        |                                           |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                                           |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE  |        |                                           |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE  |        |                                           |          |            |            |          |          | QEIIC<31:16 | š>     |        |            |          |        |        |        |        | 0000          |

| QEI1LECL        | 01E0  |        |                                           |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2  |        |                                           |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |

|---------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |

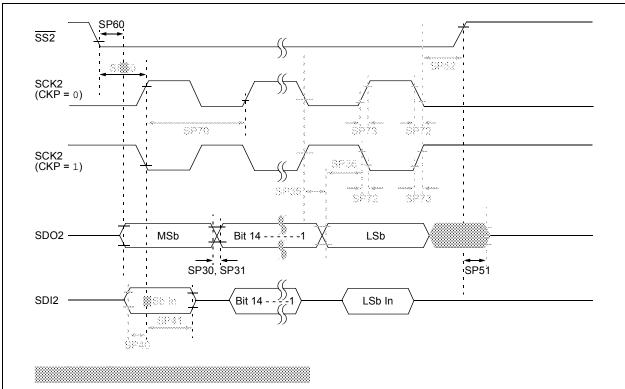

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

## REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0                                | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0      |  |  |

|------------------------------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|------------|--|--|

| _                                  |              |                                                        |               | HOME1R<6:0       | >               |                 |            |  |  |

| bit 15                             |              |                                                        |               |                  |                 |                 | bit 8      |  |  |

|                                    |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6     |  |  |

| U-0                                | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0      |  |  |

|                                    |              |                                                        |               | INDX1R<6:0>      | >               |                 |            |  |  |

| bit 7                              |              |                                                        |               |                  |                 |                 | bit C      |  |  |

| Legend:                            |              |                                                        |               |                  |                 |                 |            |  |  |

| R = Readab                         | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |            |  |  |

| -n = Value at POR '1' = Bit is set |              |                                                        |               | '0' = Bit is cle | ared            | x = Bit is unkr | is unknown |  |  |

|                                    |              | nput tied to RPI                                       |               |                  |                 |                 |            |  |  |

|                                    |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |            |  |  |

| bit 7                              |              | nted: Read as '                                        |               |                  |                 |                 |            |  |  |

| bit 6-0                            | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |            |  |  |

|                                    |              | nput tied to CM                                        |               |                  |                 |                 |            |  |  |

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0                                                                     | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|---------------------------------------------------------------------------|-------|----------------|-------|--------------|-----------------|----------|-------|

|                                                                           |       |                | VELC  | NT<15:8>     |                 |          |       |

| bit 15                                                                    |       |                |       |              |                 |          | bit 8 |

|                                                                           |       |                |       |              |                 |          |       |

| R/W-0                                                                     | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                                                           |       |                | VELC  | NT<7:0>      |                 |          |       |

| bit 7                                                                     |       |                |       |              |                 |          | bit 0 |

|                                                                           |       |                |       |              |                 |          |       |

| Legend:                                                                   |       |                |       |              |                 |          |       |

| R = Readable I                                                            | bit   | W = Writable b | oit   | U = Unimplen | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |                |       | nown         |                 |          |       |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

#### REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

#### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| <b>Legend:</b><br>R = Readable b | it    | W = Writable bit |        | U = Unimplen | nented bit, reac | l as '0' |       |

|----------------------------------|-------|------------------|--------|--------------|------------------|----------|-------|

| bit 7                            |       |                  |        |              |                  |          | bit 0 |

|                                  |       |                  | INDXC  | NT<7:0>      |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                           |       |                  |        |              |                  |          | bit 8 |

|                                  |       |                  | INDXCN | NT<15:8>     |                  |          |       |

| R/W-0                            | R/W-0 | R/W-0            | R/W-0  | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

## Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                                        | R/W-0                                                 | R/W-0                                                              | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------------------|-----------------|--------|--|--|

| —               | —                                                                                                                          | CSIDL                                                 | ABAT                                                               | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |  |  |

| bit 15          |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit 8  |  |  |

| R-1             | R-0                                                                                                                        | R-0                                                   | U-0                                                                | R/W-0                          | U-0              | U-0             | R/W-0  |  |  |

| OPMODE2         | OPMODE1                                                                                                                    | OPMODE0                                               | _                                                                  | CANCAP                         |                  |                 | WIN    |  |  |

| bit 7           |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit (  |  |  |

| Legend:         |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |  |  |

| R = Readable    | bit                                                                                                                        | W = Writable I                                        | bit                                                                | U = Unimpler                   | mented bit, read | l as '0'        |        |  |  |

| -n = Value at F | POR                                                                                                                        | '1' = Bit is set                                      |                                                                    | '0' = Bit is cle               | ared             | x = Bit is unkr | nown   |  |  |

|                 |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |  |  |

| bit 15-14       | -                                                                                                                          | ted: Read as '                                        |                                                                    |                                |                  |                 |        |  |  |

| bit 13          | 1 = Discontinu                                                                                                             | Ix Stop in Idle I<br>ues module ope<br>module opera   | eration when                                                       | device enters I                | dle mode         |                 |        |  |  |

| bit 12          |                                                                                                                            | All Pending Tra                                       |                                                                    |                                |                  |                 |        |  |  |

| Sit 12          | 1 = Signals al                                                                                                             | I transmit buffe                                      | rs to abort tra                                                    |                                | aborted          |                 |        |  |  |

| bit 11          | CANCKS: ECANx Module Clock (FCAN) Source Select bit                                                                        |                                                       |                                                                    |                                |                  |                 |        |  |  |

|                 | 1 = FCAN is ea<br>0 = FCAN is ea                                                                                           | qual to 2 * FP                                        |                                                                    |                                |                  |                 |        |  |  |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis           | ed<br>nfiguration moo<br>ten Only mode<br>opback mode | es mode<br>de                                                      | bits                           |                  |                 |        |  |  |

| bit 7-5         | OPMODE<2:(<br>111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module<br>011 = Module<br>010 = Module<br>001 = Module | <b>0&gt;</b> : Operation N<br>is in Listen All<br>ed  | Aode bits<br>Messages n<br>ation mode<br>ly mode<br>c mode<br>node |                                |                  |                 |        |  |  |

| bit 4           | Unimplemen                                                                                                                 | ted: Read as '                                        | )'                                                                 |                                |                  |                 |        |  |  |

| bit 3           |                                                                                                                            |                                                       |                                                                    | Capture Event<br>message recei |                  |                 |        |  |  |

|                 | 0 = Disables (                                                                                                             | •                                                     |                                                                    |                                |                  |                 |        |  |  |

| bit 2-1         | -                                                                                                                          | ted: Read as '0                                       |                                                                    |                                |                  |                 |        |  |  |

| bit 0           | WIN: SFR Ma                                                                                                                | p Window Sele                                         | ect bit                                                            |                                |                  |                 |        |  |  |

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       -       EXIDE       -       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                                                          |                                    |                     |                  |                  |                 |                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|------------------------------------|---------------------|------------------|------------------|-----------------|------------------|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                              | R/W-x               | R/W-x            | R/W-x            | R/W-x           | R/W-x            |  |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID       EID         bit 1-0       EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10         | SID9                                                                     | SID8                               | SID7                | SID6             | SID5             | SID4            | SID3             |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        |                                                                          |                                    |                     |                  |                  |                 | bit 8            |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                    |                     |                  |                  |                 |                  |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | W-x R/W-x R/W-x U-0 R/W-x U-0 R/W-x                                      |                                    |                     |                  |                  |                 |                  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                               | _                   | EXIDE            |                  | EID17           | EID16            |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 7         |                                                                          |                                    |                     |                  |                  |                 | bit 0            |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                    |                     |                  |                  |                 |                  |  |  |

| -n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-5SID<10:0>: Standard Identifier bits<br>1 = Message address bit, SIDx, must be '1' to match filter<br>0 = Message address bit, SIDx, must be '0' to match filterbit 4Unimplemented: Read as '0'bit 3EXIDE: Extended Identifier Enable bit<br>If MIDE = 1:<br>1 = Matches only messages with Extended Identifier addresses<br>0 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 4Unimplemented: Read as '0'bit 5I = Matches only messages with Standard Identifier addresses<br>1 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 3EIDbit 4Unimplemented: Read as '0'bit 5Unimplemented: Read as '0'bit 6II = Matches only messages with Standard Identifier addresses<br>I = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:       |                                                                          |                                    |                     |                  |                  |                 |                  |  |  |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | e bit                                                                    | W = Writable                       | bit                 | U = Unimpler     | nented bit, read | d as '0'        |                  |  |  |

| 1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                      | '1' = Bit is set                   |                     | '0' = Bit is cle | ared             | x = Bit is unkr | = Bit is unknown |  |  |

| If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 0 = Message<br>Unimplemen                                                | address bit, SI<br>Ited: Read as ' | Dx, must be '<br>o' |                  |                  |                 |                  |  |  |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | <u>If MIDE = 1:</u><br>1 = Matches<br>0 = Matches<br><u>If MIDE = 0:</u> | only messages<br>only messages     | with Extende        |                  |                  |                 |                  |  |  |

| 1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2         | Unimplemen                                                               | ted: Read as '                     | כ'                  |                  |                  |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 1-0       | EID<17:16>:                                                              | Extended Ident                     | tifier bits         |                  |                  |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | •                                                                        |                                    |                     |                  |                  |                 |                  |  |  |

| R/W-0         | R/W-0                                                                         | R/W-0                                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |  |

|---------------|-------------------------------------------------------------------------------|-------------------------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|--|

| EDG1MOD       | EDG1POL                                                                       | EDG1SEL3                                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        |                                                                               | 1                                                     |                  | 11                 |                 |                 | bit 8    |  |  |  |

|               |                                                                               |                                                       |                  |                    |                 |                 |          |  |  |  |

| R/W-0         | R/W-0                                                                         | R/W-0                                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |  |

| EDG2MOD       | DG2MOD EDG2POL EDG2SEL3 EDG2SEL2 EDG2SEL1 EDG2SEL0 —                          |                                                       |                  |                    |                 |                 |          |  |  |  |

| bit 7         |                                                                               |                                                       |                  | 1 1                |                 |                 | bit C    |  |  |  |

|               |                                                                               |                                                       |                  |                    |                 |                 |          |  |  |  |

| Legend:       |                                                                               |                                                       |                  |                    |                 |                 |          |  |  |  |

| R = Readab    | le bit                                                                        | W = Writable                                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | t POR                                                                         | '1' = Bit is set                                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |  |

|               |                                                                               |                                                       |                  |                    |                 |                 |          |  |  |  |

| bit 15        | EDG1MOD: E                                                                    | Edge 1 Edge Sa                                        | ampling Mode     | Selection bit      |                 |                 |          |  |  |  |