Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

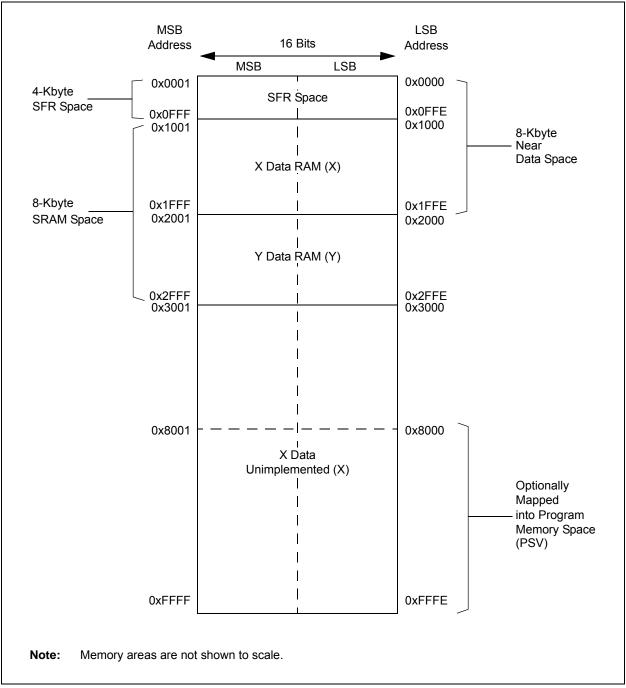

## FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

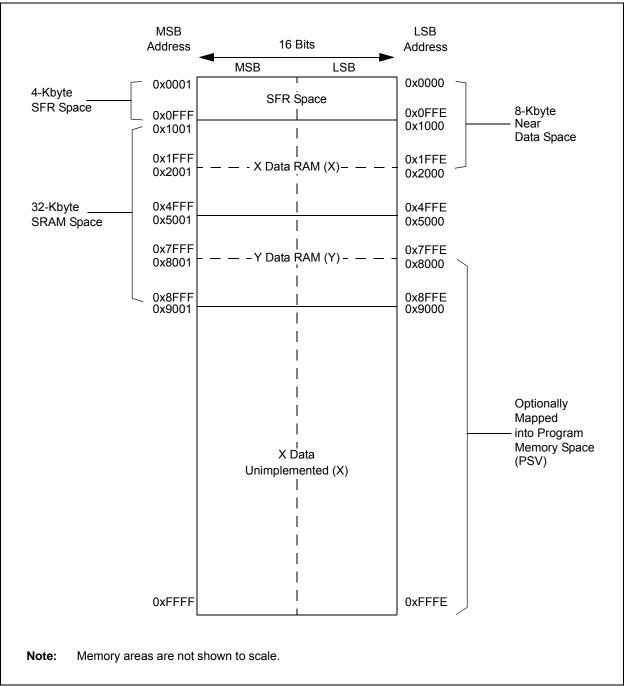

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

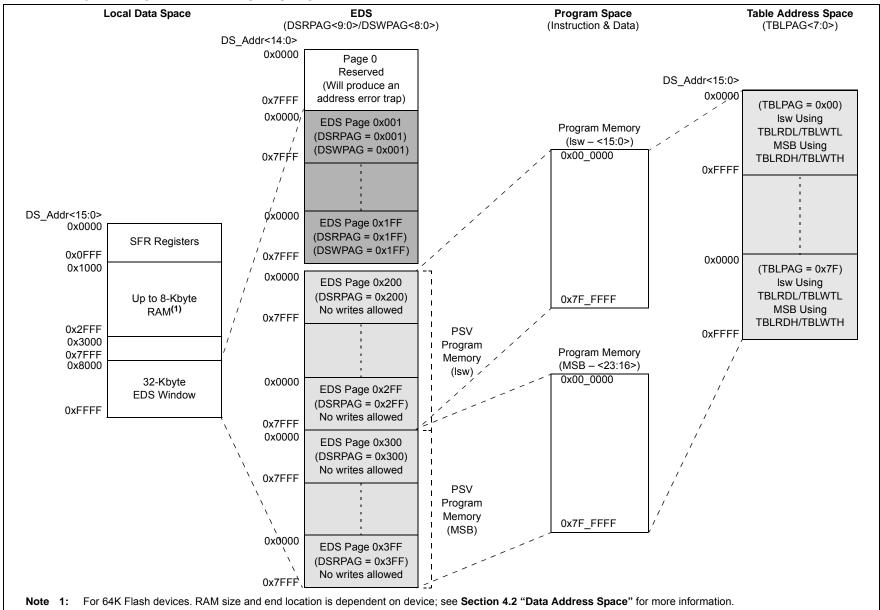

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

#### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### REGISTER 17-4: POSICNTH: POSITION COUNTER 1 HIGH WORD REGISTER

| -n = Value at POR '1' = Bit is s  |       |       |       | '0' = Bit is cleared x = Bit is unkn |       |       |       |  |  |  |

|-----------------------------------|-------|-------|-------|--------------------------------------|-------|-------|-------|--|--|--|

| R = Readable bit W = Writable bit |       |       | it    | U = Unimplemented bit, read as '0'   |       |       |       |  |  |  |

| Legend:                           |       |       |       |                                      |       |       |       |  |  |  |

|                                   |       |       |       |                                      |       |       |       |  |  |  |

| bit 7                             |       |       |       |                                      |       |       | bit 0 |  |  |  |

|                                   |       |       | POSCN | IT<23:16>                            |       |       |       |  |  |  |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0                                | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| bit 15                            |       |       |       |                                      |       |       | bit 8 |  |  |  |

|                                   |       |       | POSCN | IT<31:24>                            |       |       |       |  |  |  |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0                                | R/W-0 | R/W-0 | R/W-0 |  |  |  |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-5: POS1CNTL: POSITION COUNTER 1 LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| POSCNT<15:8> |       |       |       |       |       |       |       |  |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |  |

|              |       |       |       |       |       |       |       |  |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSCNT<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-6: POS1HLD: POSITION COUNTER 1 HOLD REGISTER

| R/W-0           | R/W-0                              | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------------------------------|----------------|-------|------------------|-----------------|-----------------|-------|

|                 |                                    |                | POSHL | _D<15:8>         |                 |                 |       |

| bit 15          |                                    |                |       |                  |                 |                 | bit 8 |

|                 |                                    |                |       |                  |                 |                 |       |

| R/W-0           | R/W-0                              | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |                                    |                | POSH  | LD<7:0>          |                 |                 |       |

| bit 7           |                                    |                |       |                  |                 |                 | bit 0 |

|                 |                                    |                |       |                  |                 |                 |       |

| Legend:         |                                    |                |       |                  |                 |                 |       |

| R = Readable    | bit                                | W = Writable I | bit   | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at P | -n = Value at POR '1' = Bit is set |                |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 **POSHLD<15:0>:** Hold Register for Reading and Writing POS1CNTH bits

### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This   | insures    | that  | the       | first | fr | ame |

|-------|--------|------------|-------|-----------|-------|----|-----|

|       | transr | nission    | after | initializ | ation | is | not |

|       | shifte | d or corru | pted. |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0               | U-0                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                    | R/W-0                              | U-0                                              | R/W-0            | R/W-0                     |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|--------------------------------------------------|------------------|---------------------------|

| UARTEN <sup>(</sup> | <sup>1)</sup>                                                       | USIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IREN <sup>(2)</sup>                                      | RTSMD                              | _                                                | UEN1             | UEN0                      |

| bit 15              |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | •                                  |                                                  |                  | bit 8                     |

|                     |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>D</b> AMA                                             | <b>D</b> 444 0                     | <b>D</b> 444 0                                   | <b>D</b> 444.0   | <b>D</b> 444 0            |

| R/W-0, H0           |                                                                     | R/W-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                    | R/W-0                              | R/W-0                                            | R/W-0            | R/W-0                     |

| WAKE                | LPBACK                                                              | ABAUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | URXINV                                                   | BRGH                               | PDSEL1                                           | PDSEL0           | STSEL                     |

| bit 7               |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                                    |                                                  |                  | bit                       |

| Legend:             |                                                                     | HC = Hardwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e Clearable b                                            | it                                 |                                                  |                  |                           |

| R = Reada           | ble bit                                                             | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oit                                                      | U = Unimplem                       | ented bit, read                                  | as '0'           |                           |

| -n = Value          | at POR                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | '0' = Bit is clea                  | ared                                             | x = Bit is unkn  | iown                      |

| bit 15              | 1 = UARTx is                                                        | ARTx Enable bit <sup>(</sup><br>s enabled; all UA<br>s disabled; all UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ARTx pins are                                            |                                    |                                                  |                  |                           |

| bit 14              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |

| bit 13              | USIDL: UAR                                                          | Tx Stop in Idle M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lode bit                                                 |                                    |                                                  |                  |                           |

|                     |                                                                     | nues module opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |                                    | le mode                                          |                  |                           |

| bit 12              | 1 = IrDA enc                                                        | Encoder and De<br>oder and decod<br>oder and decod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | er are enable                                            | d                                  |                                                  |                  |                           |

| bit 11              | $1 = \overline{\text{UxRTS}} p$                                     | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mode                                                     | t                                  |                                                  |                  |                           |

| bit 10              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |

| bit 9-8             | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                        | IARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | nd used <sup>(4)</sup><br>UxCT <u>S pin is</u> c | controlled by PC | ORT latches <sup>(4</sup> |

| bit 7               | WAKE: Wake                                                          | e-up on Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Detect During                                            | Sleep Mode Ei                      | nable bit                                        |                  |                           |

|                     | in hardwa                                                           | ontinues to sam<br>are on the follow<br>-up is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |                                    | generated on t                                   | the falling edge | ; bit is cleare           |

| bit 6               | 1 = Enables                                                         | ARTx Loopback<br>Loopback mode<br>k mode is disab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | :                                                        | bit                                |                                                  |                  |                           |

| 2:                  | Refer to the " <b>UAI</b><br>enabling the UAR<br>This feature is or | Tx module for realized and the second s | eceive or trans<br>the 16x BRG                           | mit operation.<br>mode (BRGH =     | -                                                | ce Manual" for i | nformation or             |

|                     | This feature is or                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                        | -                                  |                                                  |                  |                           |

| A-                  | This fastura is ar                                                  | ny available on l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | al nin dovicos                                           |                                    |                                                  |                  |                           |

4: This feature is only available on 64-pin devices.

#### 22.2 CTMU Control Registers

| REGISTER 2    | 22-1: CTM                    | UCON1: CTMU                                           | J CONTROL                         | REGISTER          | 1                |                        |        |  |

|---------------|------------------------------|-------------------------------------------------------|-----------------------------------|-------------------|------------------|------------------------|--------|--|

| R/W-0         | U-0                          | R/W-0                                                 | R/W-0                             | R/W-0             | R/W-0            | R/W-0                  | R/W-0  |  |

| CTMUEN        | _                            | CTMUSIDL                                              | TGEN                              | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15        |                              |                                                       |                                   |                   |                  |                        | bit 8  |  |

|               |                              |                                                       |                                   |                   |                  |                        |        |  |

| U-0           | U-0                          | U-0                                                   | U-0                               | U-0               | U-0              | U-0                    | U-0    |  |

|               |                              | —                                                     | _                                 |                   | <u> </u>         |                        | _      |  |

| bit 7         |                              |                                                       |                                   |                   |                  |                        | bit 0  |  |

|               |                              |                                                       |                                   |                   |                  |                        |        |  |

| Legend:       |                              |                                                       |                                   |                   |                  |                        |        |  |

| R = Readable  | e bit                        | W = Writable b                                        | oit                               | U = Unimplen      | nented bit, read | as '0'                 |        |  |

| -n = Value at | POR                          | '1' = Bit is set                                      |                                   | '0' = Bit is clea | ared             | x = Bit is unknown     |        |  |

| bit 15        | 1 = Module                   | TMU Enable bit<br>is enabled<br>is disabled           |                                   |                   |                  |                        |        |  |

| bit 14        | Unimpleme                    | nted: Read as '0                                      | 3                                 |                   |                  |                        |        |  |

| bit 13        | 1 = Disconti<br>0 = Continue | CTMU Stop in lo<br>nues module ope<br>es module opera | eration when a<br>tion in Idle ma |                   | lle mode         |                        |        |  |

| bit 12        | TGEN: Time                   | Generation Ena                                        | ble bit                           |                   |                  |                        |        |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

NOTES:

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                                           | R/W-0 | R/W-0          | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-------------------------------------------------|-------|----------------|-------|-------------------|-----------------|-----------------|-------|

|                                                 |       |                | PTGA  | DJ<15:8>          |                 |                 |       |

| bit 15                                          |       |                |       |                   |                 |                 | bit 8 |

|                                                 |       |                |       |                   |                 |                 |       |

| R/W-0                                           | R/W-0 | R/W-0          | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                                                 |       |                | PTGA  | DJ<7:0>           |                 |                 |       |

| bit 7                                           |       |                |       |                   |                 |                 | bit 0 |

|                                                 |       |                |       |                   |                 |                 |       |

| Legend:                                         |       |                |       |                   |                 |                 |       |

| R = Readable                                    | bit   | W = Writable b | oit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is |       |                |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

### REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PTGL0 | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PTGL  | )<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                        | U-0              | U-0                                    | U-0              | R/W-0                        | U-0              | U-0            |

|-----------------|------------------------------|------------------|----------------------------------------|------------------|------------------------------|------------------|----------------|

|                 | CVR2OE <sup>(1)</sup>        | _                | _                                      | _                | VREFSEL                      | _                | _              |

| bit 15          |                              |                  |                                        |                  |                              |                  | bit            |

| <b>D</b> 444 0  | DAALO                        | DAALO            |                                        | <b>D</b> 444 0   | DAALO                        | DANA             | <b>D</b> 444 0 |

| R/W-0           | R/W-0                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0            | R/W-0          |

| CVREN           | CVR10E <sup>(1)</sup>        | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1             | CVR0           |

| bit 7           |                              |                  |                                        |                  |                              |                  | bit            |

| Legend:         |                              |                  |                                        |                  |                              |                  |                |

| R = Readable    | bit                          | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'           |                |

| -n = Value at F | POR                          | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn  | iown           |

|                 |                              |                  |                                        |                  |                              |                  |                |

| bit 15          | Unimplement                  |                  |                                        |                  |                              |                  |                |

| bit 14          |                              | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | nected to the C<br>onnected from       |                  | nin                          |                  |                |

| bit 13-11       | Unimplement                  |                  |                                        |                  | <b>F</b>                     |                  |                |

| bit 10          | -                            |                  | age Reference                          | e Select bit     |                              |                  |                |

|                 | 1 = CVREFIN =                | -                | C                                      |                  |                              |                  |                |

|                 | 0 = CVREFIN is               | s generated by   | y the resistor ne                      | etwork           |                              |                  |                |

| bit 9-8         | Unimplement                  | ted: Read as '   | 0'                                     |                  |                              |                  |                |

| bit 7           |                              |                  | e Reference E                          |                  |                              |                  |                |

|                 |                              |                  | erence circuit is<br>erence circuit is |                  | wn                           |                  |                |

| bit 6           | CVR1OE: Co                   | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | n the CVREF1C                          |                  | n                            |                  |                |

| bit 5           | CVRR: Comp                   | arator Voltage   | Reference Ra                           | nge Selection    | n bit                        |                  |                |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3 |                  |                                        |                  |                              |                  |                |

| bit 4           | CVRSS: Com                   | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                  |                |

|                 |                              | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                  |                |

| bit 3-0         | CVR<3:0> Co                  | mparator Volt    | age Reference                          | Value Select     | ion $0 \leq CVR < 3$ :       | $0> \le 15$ bits |                |

|                 | When CVRR = CVREFIN = (CV    |                  | (CVRSRC)                               |                  |                              |                  |                |

|                 | When CVRR = CVREFIN = (CV    | = 0:             |                                        | $(\mathbf{C})$   |                              |                  |                |

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|