#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-h-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                       |  |  |  |

|------------------------------------------------|---------------------|-------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                            |  |  |  |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin funct                                                                                                                |  |  |  |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes Always associated with OSC2 pin function. |  |  |  |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                              |  |  |  |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                         |  |  |  |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                           |  |  |  |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                       |  |  |  |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                    |  |  |  |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                             |  |  |  |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.                                                                                                                                                             |  |  |  |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                |  |  |  |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                      |  |  |  |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                      |  |  |  |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                      |  |  |  |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                      |  |  |  |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                |  |  |  |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                       |  |  |  |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                       |  |  |  |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                              |  |  |  |

| U1RTS                                          | 0                   |                         | No               | 5                                                                                                                                                                                 |  |  |  |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                 |  |  |  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                     |  |  |  |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                         |  |  |  |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

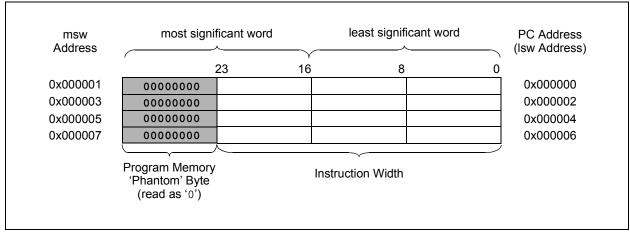

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

| TABLE 4         | -16:  | : QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |                   |          |            |            |          |          |             |        |        |            |          |        |        |        |        |               |

|-----------------|-------|--------------------------------------------------------------------------------|-------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15                                                                         | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN                                                                          | —                 | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN                                                                         | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _                                                                              | _                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |                                                                                |                   |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |                                                                                |                   |          |            |            |          | ł        | POSCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| POS1HLD         | 01CA  |                                                                                |                   |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC  |                                                                                |                   |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE  |                                                                                | INTTMR<15:0> 00   |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1TMRH        | 01D0  |                                                                                | INTTMR<31:16> 00  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1HLDL        | 01D2  |                                                                                | INTHLD<15:0> 00   |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1HLDH        | 01D4  |                                                                                |                   |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |                                                                                |                   |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |                                                                                |                   |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |                                                                                |                   |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |                                                                                |                   |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |                                                                                |                   |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE  |                                                                                | QEIGEC<31:16> 000 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1ICH         | 01DE  |                                                                                | QEIIC<31:16> 000  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1LECL        | 01E0  |                                                                                | QEILEC<15:0> 000  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| <b>QEI1LECH</b> | 01E2  |                                                                                |                   |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

## 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

## 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |                 |       |

| bit 15        |            |                  |                |                   |                  |                 | bit 8 |

|               |            |                  |                |                   |                  |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |                 |       |

| bit 7         |            |                  |                |                   |                  |                 | bit 0 |

|               |            |                  |                |                   |                  |                 |       |

| Legend:       |            |                  |                |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|               |            |                  |                |                   |                  |                 |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |                 |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits        |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP120R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                  | R/W-0                             | U-0                       | U-0              | U-0                      | U-0                | U-0                |

|--------------------|--------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|

| TON <sup>(1)</sup> | —                                    | TSIDL                             | —                         | _                | —                        | _                  | _                  |

| bit 15             |                                      |                                   |                           |                  |                          |                    | bit 8              |

|                    |                                      |                                   |                           |                  |                          |                    |                    |

| U-0                | R/W-0                                | R/W-0                             | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |

|                    | TGATE                                | TCKPS1                            | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |

| bit 7              |                                      |                                   |                           |                  |                          |                    | bit (              |

| Legend:            |                                      |                                   |                           |                  |                          |                    |                    |

| R = Readable       | e bit                                | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |

| -n = Value at      | POR                                  | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |

|                    |                                      | o                                 |                           |                  |                          |                    |                    |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16- |                                   |                           |                  |                          |                    |                    |

|                    | 0 = Stops 16-                        |                                   |                           |                  |                          |                    |                    |

| bit 14             | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

| bit 13             | TSIDL: Timer                         | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                    |                    |

|                    |                                      | ues module op                     |                           |                  | ldle mode                |                    |                    |

|                    |                                      | s module opera                    |                           | ode              |                          |                    |                    |

| bit 12-7           | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 6              |                                      | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                    |                    |

|                    | When TCS =<br>This bit is igno       |                                   |                           |                  |                          |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                    |                    |

| bit 5-4            |                                      | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                    |                    |

|                    | 11 = 1:256<br>10 = 1:64              |                                   |                           |                  |                          |                    |                    |

|                    | 01 = 1:8                             |                                   |                           |                  |                          |                    |                    |

|                    | 00 = 1:1                             |                                   |                           |                  |                          |                    |                    |

| bit 3              | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 2              |                                      | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | izes external c<br>synchronize e> |                           | nut              |                          |                    |                    |

|                    | When TCS =                           | •                                 |                           | iput             |                          |                    |                    |

|                    | This bit is igno                     |                                   |                           |                  |                          |                    |                    |

| bit 1              | TCS: Timer1                          | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                    |                    |

|                    | 1 = External c<br>0 = Internal cl    | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |

| bit 0              | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

|                    | nen Timer1 is er<br>empts by user s  |                                   |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0               | U-0        | U-0              | U-0 | U-0                                | U-0                     | U-0                     | U-0         |  |

|-------------------|------------|------------------|-----|------------------------------------|-------------------------|-------------------------|-------------|--|

| —                 | —          | —                | _   | —                                  | —                       | —                       | _           |  |

| bit 15            |            |                  |     |                                    |                         |                         | bit 8       |  |

|                   |            |                  |     |                                    |                         |                         |             |  |

| U-0               | U-0        | U-0              | U-0 | U-0                                | R/W-0                   | R/W-0                   | R/W-0       |  |

| —                 | —          | —                | _   | —                                  | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |

| bit 7             |            |                  |     |                                    |                         |                         | bit 0       |  |

|                   |            |                  |     |                                    |                         |                         |             |  |

| Legend:           |            |                  |     |                                    |                         |                         |             |  |

| R = Readable      | bit        | W = Writable     | bit | U = Unimplemented bit, read as '0' |                         |                         |             |  |

| -n = Value at POR |            | '1' = Bit is set |     | '0' = Bit is cleared               |                         | x = Bit is unknown      |             |  |

|                   |            |                  |     |                                    |                         |                         |             |  |

| bit 15-3          | Unimplemen | ted: Read as '   | י'  |                                    |                         |                         |             |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                   | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|-----------------------------------|-------|------------------|-------------------------|------------------------------------|-------|--------------------|-------|--|

| CSS15                             | CSS14 | CSS13            | CSS12                   | CSS11 CSS10                        |       | CSS9               | CSS8  |  |

| bit 15                            |       |                  |                         | ·                                  | •     | ·                  | bit 8 |  |

|                                   |       |                  |                         |                                    |       |                    |       |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                   | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

| CSS7                              | CSS6  | CSS5             | CSS4                    | CSS3                               | CSS2  | CSS1               | CSS0  |  |

| bit 7                             | -     |                  |                         |                                    | •     |                    | bit ( |  |

|                                   |       |                  |                         |                                    |       |                    |       |  |

| Legend:                           |       |                  |                         |                                    |       |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit                     | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR '1' = E         |       | '1' = Bit is set | et '0' = Bit is cleared |                                    |       | x = Bit is unknown |       |  |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

| DC CHARACTERISTICS |        |                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                |         |    |                        |  |

|--------------------|--------|---------------------------------------------------------|------------------------------------------------------|--------------------------------|---------|----|------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                          | Min.                                                 | Min. Typ. Max. Units Condition |         |    |                        |  |

|                    | VIL    | Input Low Voltage                                       |                                                      |                                |         |    |                        |  |

| DI10               |        | Any I/O Pin and MCLR                                    | Vss                                                  | —                              | 0.2 VDD | V  |                        |  |

| DI18               |        | I/O Pins with SDAx, SCLx                                | Vss                                                  | —                              | 0.3 VDD | V  | SMBus disabled         |  |

| DI19               |        | I/O Pins with SDAx, SCLx                                | Vss                                                  | —                              | 0.8     | V  | SMBus enabled          |  |

|                    | Vih    | Input High Voltage                                      |                                                      |                                |         |    |                        |  |

| DI20               |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD                                              | —                              | Vdd     | V  | (Note 3)               |  |

|                    |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD                                              | —                              | 5.5     | V  | (Note 3)               |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD                                              | —                              | 5.5     | V  | SMBus disabled         |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 2.1                                                  | _                              | 5.5     | V  | SMBus enabled          |  |

|                    | ICNPU  | Change Notification Pull-up Current                     |                                                      |                                |         |    |                        |  |

| DI30               |        |                                                         | 150                                                  | 250                            | 550     | μA | VDD = 3.3V, VPIN = VSS |  |

|                    | ICNPD  | Change Notification<br>Pull-Down Current <sup>(4)</sup> |                                                      |                                |         |    |                        |  |

| DI31               |        |                                                         | 20                                                   | 50                             | 100     | μA | Vdd = 3.3V, Vpin = Vdd |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

**5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| DC CHARACTERISTICS |        |                                                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                                                |  |

|--------------------|--------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                      | Min.                                                                                                                                                                                                 | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                                |                                                                                                                                                                                                      |                     |      |       |                                                                |  |

| D130               | Eр     | Cell Endurance                                      | 10,000                                                                                                                                                                                               | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention                            | 20                                                                                                                                                                                                   | _                   |      | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                                                                                                                                                    | 10                  |      | mA    |                                                                |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                                                                                                                                                                                                    | —                   | 150  | mA    |                                                                |  |

| D137a              | TPE    | Page Erase Time                                     | 17.7                                                                                                                                                                                                 | —                   | 22.9 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |

| D137b              | Тре    | Page Erase Time                                     | 17.5                                                                                                                                                                                                 | —                   | 23.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |

| D138a              | Tww    | Word Write Cycle Time                               | 41.7                                                                                                                                                                                                 | —                   | 53.8 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |

| D138b              | Tww    | Word Write Cycle Time                               | 41.2                                                                                                                                                                                                 | —                   | 54.4 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

| AC CHARACTERISTICS |           |                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                             |  |  |

|--------------------|-----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |  |

| SY00               | Τρυ       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                       | 400                 | 600  | μS    |                                                                                                             |  |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                                                         | 1024 Tosc           |      |       | Tosc = OSC1 period                                                                                          |  |  |

| SY12               | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                    | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |

|                    |           |                                                                | 3.26                                                                                                                                                                                                                                                                                    | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                                                                                                             |  |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                       | _                   | _    | μS    |                                                                                                             |  |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |  |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _                                                                                                                                                                                                                                                                                       | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |  |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | _                                                                                                                                                                                                                                                                                       | —                   | 30   | μS    |                                                                                                             |  |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | 46                                                                                                                                                                                                                                                                                      | 48                  | 54   | μS    |                                                                                                             |  |  |

| SY38               | Toscdlprc | LPRC Oscillator Start-up<br>Delay                              |                                                                                                                                                                                                                                                                                         | —                   | 70   | μS    |                                                                                                             |  |  |

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

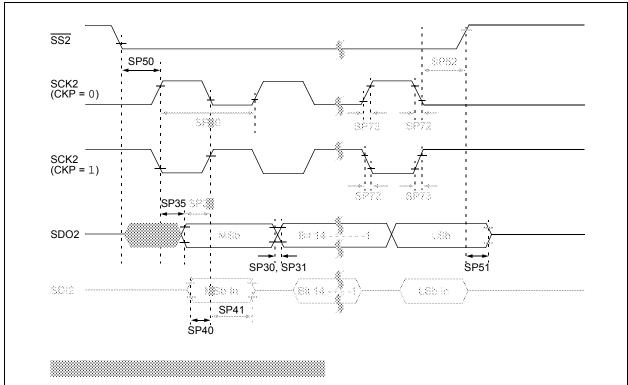

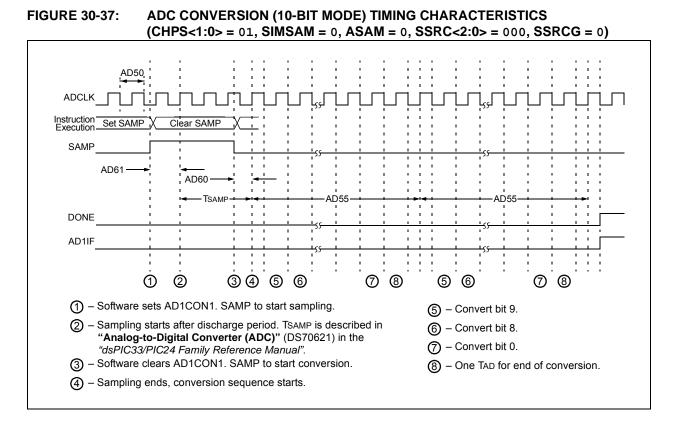

#### FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

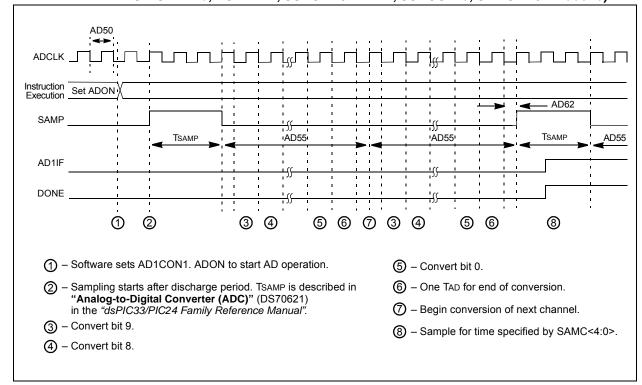

#### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

## 33.1 Package Marking Information (Continued)

48-Lead UQFN (6x6x0.5 mm)

Example 33EP64GP 504-I/MV (3) 1310017

64-Lead QFN (9x9x0.9 mm)

Example dsPIC33EP 64GP506 -I/MR® 1310017

64-Lead TQFP (10x10x1 mm)

Example

© 2011-2013 Microchip Technology Inc.

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |      |           |      |  |  |  |

|------------------------|-------------|------|-----------|------|--|--|--|

| Dimension              | Limits      | MIN  | NOM       | MAX  |  |  |  |

| Number of Pins         | N           |      | 48        |      |  |  |  |

| Pitch                  | е           |      | 0.40 BSC  |      |  |  |  |

| Overall Height         | Α           | 0.45 | 0.50      | 0.55 |  |  |  |

| Standoff               | A1          | 0.00 | 0.02      | 0.05 |  |  |  |

| Contact Thickness      | A3          |      | 0.127 REF |      |  |  |  |

| Overall Width          | E           |      | 6.00 BSC  |      |  |  |  |

| Exposed Pad Width      | E2          | 4.45 | 4.60      | 4.75 |  |  |  |