Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\cdot \mathbf{X} =$

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K × 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-h-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

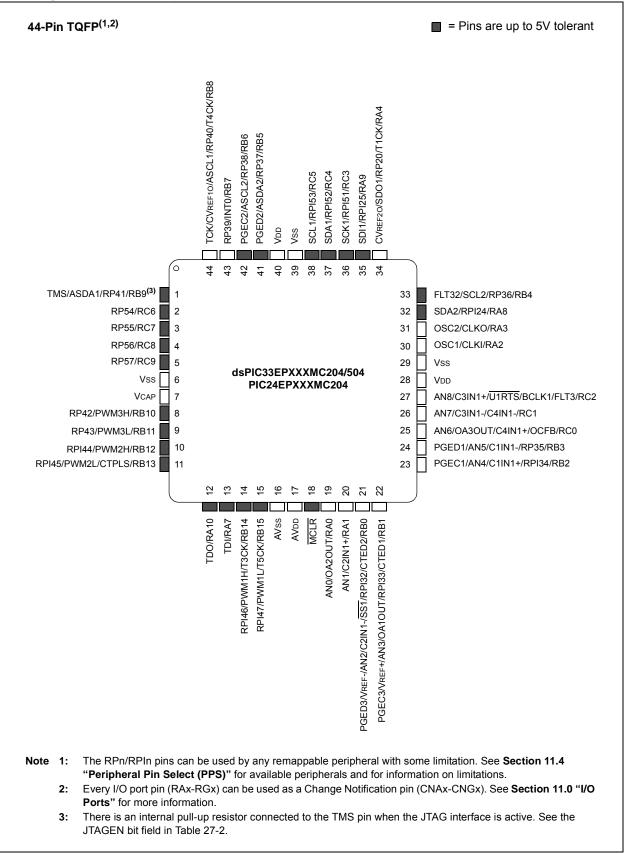

# Pin Diagrams (Continued)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4   | 4-9:  | INPUT  |                                                       | JRE 1 T                    | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|-------------------------------------------------------|----------------------------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                | Bit 13                     | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —                                                     | ICSIDL                     | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _      | _                                                     |                            | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |                                                       |                            |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        |                                                       | Input Capture 1 Timer 0000 |        |           |        |       |              |              |          |       |       |       |          |          |       |               |

| IC2CON1   | 0148  |        | - ICSIDL ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> 000 |                            |        |           |        |       |              |              |          | 0000  |       |       |          |          |       |               |

| IC2CON2   | 014A  |        | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> 0                 |                            |        |           |        |       |              |              |          | 000D  |       |       |          |          |       |               |

| IC2BUF    | 014C  |        |                                                       |                            |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |                                                       |                            |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _                                                     | ICSIDL                     | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _                                                     |                            |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |                                                       |                            |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |                                                       |                            |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _                                                     | ICSIDL                     | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _                                                     |                            | _      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        | Input Capture 4 Buffer Register                       |                            |        |           |        |       |              |              |          |       | xxxx  |       |          |          |       |               |

| IC4TMR    | 015E  |        | Input Capture 4 Timer 0000                            |                            |        |           |        |       |              |              |          | 0000  |       |       |          |          |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                 |       |        |                  |         |         |         |            |         |          |                                                     |        |       |       |        |          |       |        | All    |

|-----------------|-------|--------|------------------|---------|---------|---------|------------|---------|----------|-----------------------------------------------------|--------|-------|-------|--------|----------|-------|--------|--------|

| File Name       | Addr. | Bit 15 | Bit 14           | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7                                               | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1 | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN  | —                | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT                                             | PTGWTO | _     | _     | —      | —        | PTGIT | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F      | PTGCLK<2         | :0>     |         | F       | PTGDIV<4:0 | >       |          | PTGPWD<3:0> — PTGWDT<2:0>                           |        |       |       |        | 0>       | 0000  |        |        |

| PTGBTE          | 0AC4  |        | ADC              | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS OC3CS OC2CS OC1CS OC4TSS OC3TSS OC2TSS OC1TSS |        |       |       |        |          | 0000  |        |        |

| PTGHOLD         | 0AC6  |        |                  |         |         |         |            |         | PTGHOLD  | <15:0>                                              |        |       |       |        |          |       |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |        |                  |         |         |         |            |         | PTGT0LIM | <15:0>                                              |        |       |       |        |          |       |        | 0000   |

| PTGT1LIM        | 0ACA  |        | PTGT1LIM<15:0> 0 |         |         |         |            |         |          |                                                     |        | 0000  |       |        |          |       |        |        |

| PTGSDLIM        | 0ACC  |        | PTGSDLIM<15:0> 0 |         |         |         |            |         |          |                                                     |        | 0000  |       |        |          |       |        |        |

| <b>PTGC0LIM</b> | 0ACE  |        | PTGC0LIM<15:0>   |         |         |         |            |         |          |                                                     |        | 0000  |       |        |          |       |        |        |

| PTGC1LIM        | 0AD0  |        |                  |         |         |         |            |         | PTGC1LIN | <15:0>                                              |        |       |       |        |          |       |        | 0000   |

| PTGADJ          | 0AD2  |        |                  |         |         |         |            |         | PTGADJ<  | :15:0>                                              |        |       |       |        |          |       |        | 0000   |

| PTGL0           | 0AD4  |        |                  |         |         |         |            |         | PTGL0<   | 15:0>                                               |        |       |       |        |          |       |        | 0000   |

| PTGQPTR         | 0AD6  | —      | —                | —       | —       | _       | —          | —       | _        | —                                                   | —      | -     |       | P      | TGQPTR<4 | 4:0>  |        | 0000   |

| PTGQUE0         | 0AD8  |        |                  |         | STEP    | 1<7:0>  |            |         |          |                                                     |        |       | STEPO | )<7:0> |          |       |        | 0000   |

| PTGQUE1         | 0ADA  |        |                  |         | STEP    | '3<7:0> |            |         |          |                                                     |        |       | STEP2 | 2<7:0> |          |       |        | 0000   |

| PTGQUE2         | 0ADC  |        |                  |         | STEP    | 25<7:0> |            |         |          |                                                     |        |       | STEP4 | <7:0>  |          |       |        | 0000   |

| PTGQUE3         | 0ADE  |        |                  |         | STEP    | 7<7:0>  |            |         |          |                                                     |        |       | STEP6 | 6<7:0> |          |       |        | 0000   |

| PTGQUE4         | 0AE0  |        |                  |         | STEP    | 9<7:0>  |            |         |          |                                                     |        |       | STEP8 | 8<7:0> |          |       |        | 0000   |

| PTGQUE5         | 0AE2  |        | STEP11<7:0>      |         |         |         |            |         |          |                                                     |        |       | STEP1 | 0<7:0> |          |       |        | 0000   |

| PTGQUE6         | 0AE4  |        | STEP13<7:0>      |         |         |         |            |         |          | STEP12<7:0>                                         |        |       |       |        |          | 0000  |        |        |

| PTGQUE7         | 0AE6  |        |                  |         | STEP    | 15<7:0> |            |         |          |                                                     |        |       | STEP1 | 4<7:0> |          |       |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

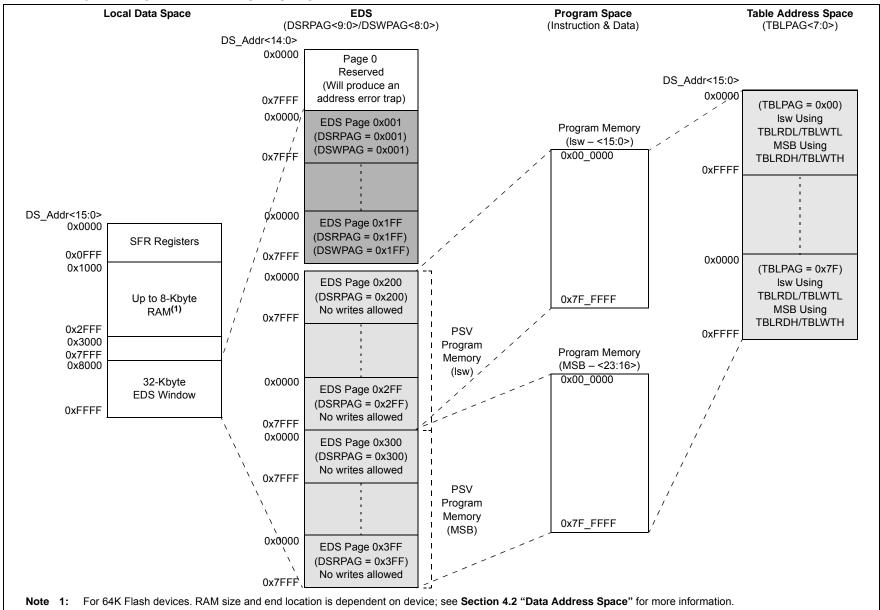

# EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |

|-------|--------------------------------------------|

|       | word-sized data (LSb of every EA is always |

|       | clear). The XBREVx value is scaled         |

|       | accordingly to generate compatible (byte)  |

|       | addresses.                                 |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

# TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |                 |       |

| bit 15        |            |                  |                |                   |                  |                 | bit 8 |

|               |            |                  |                |                   |                  |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |                 |       |

| bit 7         |            |                  |                |                   |                  |                 | bit 0 |

|               |            |                  |                |                   |                  |                 |       |

| Legend:       |            |                  |                |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|               |            |                  |                |                   |                  |                 |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |                 |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits        |       |

## REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

## REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 13.2 Timer Control Registers

| R/W-0         | U-0                                   | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |

|---------------|---------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| TON           |                                       | TSIDL                              | —              | _                |                 |                 | _     |  |  |  |  |  |

| bit 15        |                                       |                                    |                |                  |                 |                 | bit 8 |  |  |  |  |  |

|               |                                       |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |

| _             | TGATE                                 | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |

| bit 7         |                                       |                                    |                |                  |                 |                 | bit ( |  |  |  |  |  |

| <u> </u>      |                                       |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| Legend:       | - 1-:4                                |                                    |                | II II.           |                 |                 |       |  |  |  |  |  |

| R = Readable  |                                       | W = Writable                       |                | -                | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | PUR                                   | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | TON: Timerx                           | On hit                             |                |                  |                 |                 |       |  |  |  |  |  |

|               | When T32 = 2                          |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Starts 32-                        | bit Timerx/y                       |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 32-                         |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 16-                         |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 14        | Unimplemen                            | himplemented: Read as '0'          |                |                  |                 |                 |       |  |  |  |  |  |

| bit 13        | TSIDL: Timer                          | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |  |  |  |  |  |

|               |                                       | ues module op                      |                |                  | dle mode        |                 |       |  |  |  |  |  |

|               |                                       | s module opera                     |                | ode              |                 |                 |       |  |  |  |  |  |

| bit 12-7      | -                                     | ted: Read as '                     |                |                  |                 |                 |       |  |  |  |  |  |

| bit 6         |                                       | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |  |  |  |  |  |

|               | When TCS =<br>This bit is igno        |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | When TCS =                            |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Gated tim                         | e accumulatior                     |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                       | e accumulation                     |                |                  |                 |                 |       |  |  |  |  |  |

| bit 5-4       |                                       | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64               |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 01 = 1:8                              |                                    |                |                  |                 |                 |       |  |  |  |  |  |

|               | 00 = 1:1                              |                                    |                |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                        | mer Mode Sele                      | ect bit        |                  |                 |                 |       |  |  |  |  |  |

|               |                                       | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |  |  |  |  |  |

| bit 2         | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 1         | TCS: Timerx                           | Clock Source S                     | elect bit      |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl     | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |

| bit 0         | Unimplomon                            | ted: Read as '                     | ı'             |                  |                 |                 |       |  |  |  |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

NOTES:

# 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This                  | insures | that  | the       | first | fr | ame |

|-------|-----------------------|---------|-------|-----------|-------|----|-----|

|       | transr                | nission | after | initializ | ation | is | not |

|       | shifted or corrupted. |         |       |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

# 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

# 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x    SID10  SID9  SID8  SID7  SID6  SID5  SID4  SID3    bit 15  bit 15  bit 8  bit 8  bit 8  bit 8  bit 8    R/W-x  R/W-x  R/W-x  U-0  R/W-x  U-0  R/W-x  R/W-x    SID2  SID1  SID0  -  EXIDE  -  EID17  EID16    bit 7  bit 0  -  EXIDE  -  EID17  EID16    bit 7  bit 0  -  -  EXIDE  -  bit 0    Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                          |                                      |                     |                  |                  |                 |                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------------------------|---------------------|------------------|------------------|-----------------|--------------------|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                                | R/W-x               | R/W-x            | R/W-x            | R/W-x           | R/W-x              |  |  |

| R/W-x  R/W-x  U-0  R/W-x  U-0  R/W-x  R/W-x    SID2  SID1  SID0  -  EXIDE  -  EID17  EID16    bit 7  bit 0    Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'  bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses  0 = Matches only messages with Standard Identifier addresses    0 = Matches only messages with Standard Identifier addresses  Ignores EXIDE bit.  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'  bit 1-0  EID  EID    bit 1-0  EID  Extended Identifier bits  1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SID10         | SID9                                                                     | SID8                                 | SID7                | SID6             | SID5             | SID4            | SID3               |  |  |

| SID2  SID1  SID0  —  EXIDE  —  EID17  EID16    bit 7  bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15        |                                                                          |                                      |                     |                  |                  |                 | bit 8              |  |  |

| SID2  SID1  SID0  —  EXIDE  —  EID17  EID16    bit 7  bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                          |                                      |                     |                  |                  |                 |                    |  |  |

| bit 7  bit 0    Legend:  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  x = Bit is unknown    bit 4  Unimplemented: Read as '0'  bit 3  EXIDE: Extended Identifier Enable bit  If MIDE = 1:    1 = Matches only messages with Extended Identifier addresses  0 = Matches only messages with Standard Identifier addresses    0 = Matches only messages with Standard Identifier addresses  If MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'  bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter  1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                    | R/W-x                                | U-0                 | R/W-x            | U-0              | R/W-x           | R/W-x              |  |  |

| Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses    If MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SID2          | SID1                                                                     | SID0                                 | _                   | EXIDE            |                  | EID17           | EID16              |  |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses  0 = Matches only messages with Standard Identifier addresses    1f MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                                                          |                                      |                     |                  |                  |                 | bit 0              |  |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses  0 = Matches only messages with Standard Identifier addresses    1f MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                                                                          |                                      |                     |                  |                  |                 |                    |  |  |

| -n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-5SID<10:0>: Standard Identifier bits<br>1 = Message address bit, SIDx, must be '1' to match filter<br>0 = Message address bit, SIDx, must be '0' to match filterbit 4Unimplemented: Read as '0'bit 3EXIDE: Extended Identifier Enable bit<br>If MIDE = 1:<br>1 = Matches only messages with Extended Identifier addresses<br>0 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 4Unimplemented: Read as '0'bit 5I = Matches only messages with Standard Identifier addresses<br>1 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 3EIDbit 4Unimplemented: Read as '0'bit 5Unimplemented: Read as '0'bit 6II = Matches only messages with Standard Identifier addresses<br>I = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:       |                                                                          |                                      |                     |                  |                  |                 |                    |  |  |

| bit 15-5  SID<10:0>: Standard Identifier bits    1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses    0 = Matches only messages with Standard Identifier addresses    1 f MIDE = 0:    Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R = Readable  | e bit                                                                    | W = Writable                         | bit                 | U = Unimpler     | nented bit, read | d as '0'        |                    |  |  |

| 1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses  0 = Matches only messages with Standard Identifier addresses    If MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID    I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                      | '1' = Bit is set                     |                     | '0' = Bit is cle | ared             | x = Bit is unkr | x = Bit is unknown |  |  |

| If MIDE = 1:    1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses    If MIDE = 0:    Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | 0 = Message<br>Unimplemen                                                | address bit, SI<br>Ited: Read as '   | Dx, must be '<br>o' |                  |                  |                 |                    |  |  |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | <u>If MIDE = 1:</u><br>1 = Matches<br>0 = Matches<br><u>If MIDE = 0:</u> | only messages<br>only messages       | with Extende        |                  |                  |                 |                    |  |  |