Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

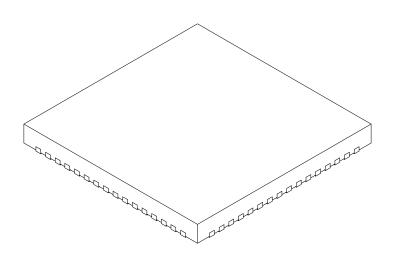

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6       | Bit 5      | Bit 4   | Bit 3         | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|-------------|------------|---------|---------------|--------|---------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —           | —          | _       | —             | _      | -       |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P           | TGSTEPIP<2 | :0>     | —             | —      |         |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        | PTG2IP<2:0> |            | _       | - PTG1IP<2:0> |        | 0444    |        |               |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR     | DMACERR    | MATHERR | ADDRERR       | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _           | —          | —       | _             | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _           | DAE        | DOOVR   | _             | —      |         |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _           | —          | —       | —             | —      | _       | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |             |            | VECNU   | M<7:0>        |        |         |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12        | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6  | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|---------------|--------|--------|----------------|--------|-------|--------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF        | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF  | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF          | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _      | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _             |        |        |                | _      | _     | IC4IF  | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _             |        | QEI1IF | PSEMIF         | _      | _     | _      | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |               |        |        | -              | _      | _     | C1TXIF | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _             | _      |        |                | _      | _     | PTG3IF | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | <b>U1TXIE</b> | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE  | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE          | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _      | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _             | _      |        | _              | _      | _     | IC4IE  | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _             | _      | QEI1IE | PSEMIE         | _      | _     | _      | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _             |        |        | _              | _      | _     | C1TXIE | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _             | _      |        | _              | _      | _     | PTG3IE | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |               | _      |        | OC1IP<2:0      | >      | _     |        | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |               | _      |        | OC2IP<2:0      | >      | _     |        | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >             | _      |        | SPI1IP<2:0     | )>     | _     |        | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _             | _      | C      | MA1IP<2:       | 0>     | _     |        | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |               | _      |        | CMIP<2:0       | >      | _     |        | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |               | _      |        | OC4IP<2:0      | >      | _     |        | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >             | _      | ι      | J2RXIP<2:      | 0>     | _     |        | INT2IP<2:0>     |               |        |          | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |               | _      | C      | 2:<br>2:<br>2: | 0>     | _     |        | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _             | _      |        | IC4IP<2:0      | >      | _     |        | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _             | _      | N      | 112C2IP<2:     | 0>     | _     |        | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _             | _      | (      | QEI1IP<2:(     | )>     | _     |        | PSEMIP<2:0      | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >             | _      |        | U2EIP<2:0      |        | _     |        | U1EIP<2:0>      |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _             | _      |        | C1TXIP<2:      |        | _     | _      | _               | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            |               | _      |        |                |        |       |        | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

## TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

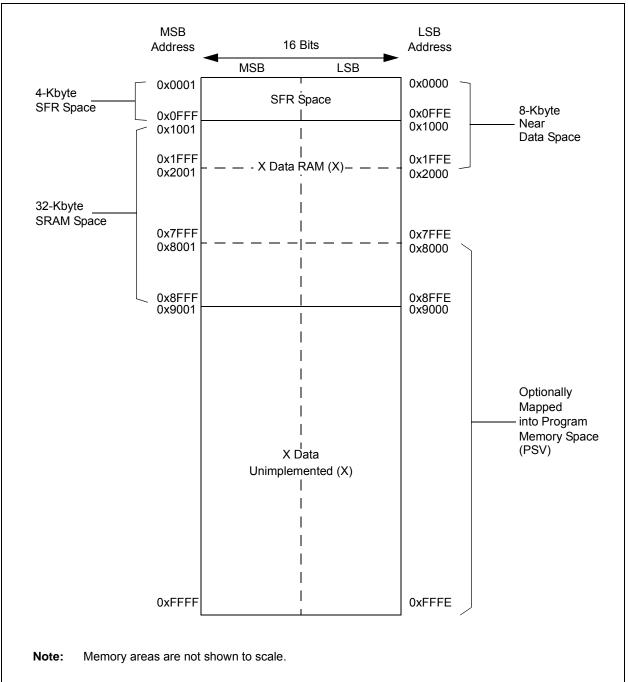

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                  | U-0              | U-0   | U-0              | U-0   | U-0             | U-0   |  |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|-------|------------------|-------|-----------------|-------|--|--|--|--|

| —               | —                                                                    | —                | —     | —                | —     | _               | —     |  |  |  |  |

| bit 15          |                                                                      |                  |       |                  | •     |                 | bit 8 |  |  |  |  |

|                 |                                                                      |                  |       |                  |       |                 |       |  |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|                 |                                                                      |                  | STB<  | 23:16>           |       |                 |       |  |  |  |  |

| bit 7           |                                                                      |                  |       |                  |       |                 | bit 0 |  |  |  |  |

|                 |                                                                      |                  |       |                  |       |                 |       |  |  |  |  |

| Legend:         |                                                                      |                  |       |                  |       |                 |       |  |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                  |       |                 |       |  |  |  |  |

| -n = Value at P | POR                                                                  | '1' = Bit is set |       | '0' = Bit is cle | eared | x = Bit is unkr | nown  |  |  |  |  |

|                 |                                                                      |                  |       |                  |       |                 |       |  |  |  |  |

### REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

### REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

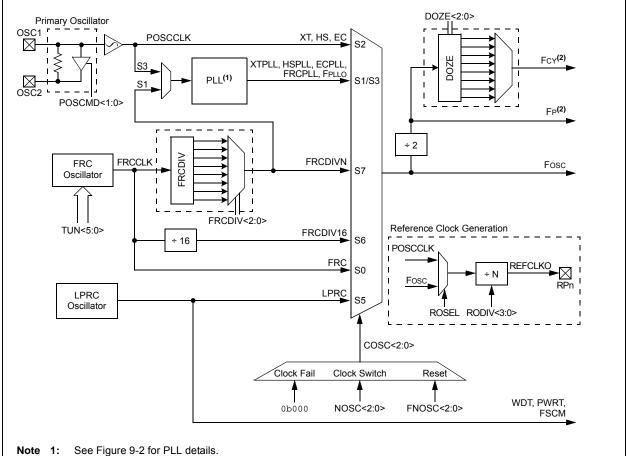

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

## 13.2 Timer Control Registers

| R/W-0         | U-0                                 | R/W-0                                                                                                                           | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |  |  |

|---------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|--|

| TON           |                                     | TSIDL                                                                                                                           | —              | _                |                 |                 | _     |  |  |  |  |  |  |  |

| bit 15        |                                     |                                                                                                                                 |                |                  |                 |                 | bit 8 |  |  |  |  |  |  |  |

|               |                                     |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| U-0           | R/W-0                               | R/W-0                                                                                                                           | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |  |  |

| _             | TGATE                               | TCKPS1                                                                                                                          | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |  |  |

| bit 7         |                                     |                                                                                                                                 |                |                  |                 |                 | bit ( |  |  |  |  |  |  |  |

| <u> </u>      |                                     |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| Legend:       | - 1-:4                              |                                                                                                                                 |                | II II.           |                 |                 |       |  |  |  |  |  |  |  |

| R = Readable  |                                     | W = Writable                                                                                                                    |                | -                | nented bit, rea |                 |       |  |  |  |  |  |  |  |

| -n = Value at | PUR                                 | '1' = Bit is set                                                                                                                |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |  |  |

| bit 15        | TON: Timerx                         | On hit                                                                                                                          |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | When T32 = 2                        |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = Starts 32-                      | bit Timerx/y                                                                                                                    |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 0 = Stops 32-                       |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                     | <u>When T32 = 0:</u><br>1 = Starts 16-bit Timerx                                                                                |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 0 = Stops 16-                       |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 14        | Unimplemen                          | Unimplemented: Read as '0'                                                                                                      |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 13        | TSIDL: Timerx Stop in Idle Mode bit |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                     | <ol> <li>Discontinues module operation when device enters Idle mode</li> <li>Continues module operation in Idle mode</li> </ol> |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                     | -                                                                                                                               |                | ode              |                 |                 |       |  |  |  |  |  |  |  |

| bit 12-7      | -                                   | ted: Read as '                                                                                                                  |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 6         |                                     | erx Gated Time                                                                                                                  | Accumulation   | Enable bit       |                 |                 |       |  |  |  |  |  |  |  |

|               | When TCS =<br>This bit is igno      |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | When TCS =                          |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = Gated tim                       | e accumulatior                                                                                                                  |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                     | e accumulation                                                                                                                  |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 5-4       |                                     | : Timerx Input                                                                                                                  | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64             |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 01 = 1:8                            |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 00 = 1:1                            |                                                                                                                                 |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                      | mer Mode Sele                                                                                                                   | ect bit        |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                     | nd Timery form<br>nd Timery act as                                                                                              |                |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 2         | Unimplemen                          | ted: Read as '                                                                                                                  | )'             |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                         | Clock Source S                                                                                                                  | elect bit      |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl   | clock is from pir<br>lock (FP)                                                                                                  | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |  |  |

| bit 0         | Unimplomon                          | ted: Read as '                                                                                                                  | ı'             |                  |                 |                 |       |  |  |  |  |  |  |  |

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

## 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x         | R/W-x                     | R/W-x                | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |  |  |

|---------------|---------------------------|----------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|--|

| EID5          | EID4                      | EID3                 | EID2          | EID1             | EID0             | RTR             | RB1   |  |  |  |  |

| bit 15        |                           |                      |               |                  |                  |                 | bit 8 |  |  |  |  |

|               |                           |                      |               |                  |                  |                 |       |  |  |  |  |

| U-x           | U-x                       | U-x                  | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |  |  |

| —             | —                         | —                    | RB0           | DLC3             | DLC2             | DLC1            | DLC0  |  |  |  |  |

| bit 7         |                           |                      |               |                  |                  |                 | bit 0 |  |  |  |  |

| Lonondi       |                           |                      |               |                  |                  |                 |       |  |  |  |  |

| Legend:       | l. h.:.                   |                      | L.11          |                  |                  | -l (O)          |       |  |  |  |  |

| R = Readab    |                           | W = Writable         |               | •                | mented bit, read |                 |       |  |  |  |  |

| -n = Value a  | t POR                     | '1' = Bit is set     |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |  |  |  |  |

|               |                           |                      |               |                  |                  |                 |       |  |  |  |  |

| bit 15-10     | EID<5:0>: E               | xtended Identifi     | er bits       |                  |                  |                 |       |  |  |  |  |

| bit 9         | RTR: Remot                | e Transmission       | Request bit   |                  |                  |                 |       |  |  |  |  |

|               | When IDE =                | 1:                   |               |                  |                  |                 |       |  |  |  |  |

|               | •                         | e will request re    | mote transmis | ssion            |                  |                 |       |  |  |  |  |

|               | 0 = Normal n              | 0                    |               |                  |                  |                 |       |  |  |  |  |

|               | When IDE =<br>The RTR bit |                      |               |                  |                  |                 |       |  |  |  |  |

| <b>h</b> :+ 0 | RB1: Reserv               | -                    |               |                  |                  |                 |       |  |  |  |  |

| bit 8         |                           |                      | or CAN proto  |                  |                  |                 |       |  |  |  |  |

|               |                           | et this bit to '0' p | -             | 0001.            |                  |                 |       |  |  |  |  |

| bit 7-5       | •                         | nted: Read as '      | 0             |                  |                  |                 |       |  |  |  |  |

| bit 4         | RB0: Reserved Bit 0       |                      |               |                  |                  |                 |       |  |  |  |  |

|               | User must se              | et this bit to '0' p | per CAN proto | ocol.            |                  |                 |       |  |  |  |  |

| hit 2 0       |                           | Jota Longth Co.      | da hita       |                  |                  |                 |       |  |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

## BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                  | R/W-x           | R/W-x    | R/W-x |  |

|-----------------|-------|------------------|-------|----------------------------------------|-----------------|----------|-------|--|

|                 |       |                  | Ву    | /te 1                                  |                 |          |       |  |

| bit 15          |       |                  |       |                                        |                 |          | bit 8 |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                  | R/W-x           | R/W-x    | R/W-x |  |

|                 |       |                  | Ву    | rte 0                                  |                 |          |       |  |

| bit 7           |       |                  |       |                                        |                 |          | bit 0 |  |

| Legend:         |       |                  |       |                                        |                 |          |       |  |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen                           | nented bit, rea | d as '0' |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |                 |          |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|--------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PTGT0L | _IM<15:8>         |                 |                 |       |

| bit 15          |       |                  |        |                   |                 |                 | bit 8 |

|                 |       |                  |        |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PTGT0  | LIM<7:0>          |                 |                 |       |

| bit 7           |       |                  |        |                   |                 |                 | bit 0 |

|                 |       |                  |        |                   |                 |                 |       |

| Legend:         |       |                  |        |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit    | U = Unimplem      | ented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |        | '0' = Bit is clea | red             | x = Bit is unkr | nown  |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|---------|-------|-------|-------|

|        |       |       | PTGT1LI | M<15:8> |       |       |       |

| bit 15 |       |       |         |         |       |       | bit 8 |

|        |       |       |         |         |       |       |       |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| PTGT1LIM<7:0> |       |       |       |       |       |       |       |

| bit 7         |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

| File<br>Name | Address           | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8 | Bit 7                   | Bit 6                  | Bit 5      | Bit 4                   | Bit 3                   | Bit 2 | Bit 1     | Bit 0   |

|--------------|-------------------|--------------------------------------|-----------|-------------------------|------------------------|------------|-------------------------|-------------------------|-------|-----------|---------|

| Reserved     | 0057EC            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFEC            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157EC            | 128                                  | _         | _                       | _                      | _          | _                       | _                       | _     | _         | _       |

|              | 02AFEC            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557EC            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| Reserved     | 0057EE            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFEE            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157EE            | 128                                  |           | _                       | _                      | _          | _                       | _                       | _     | _         | _       |

|              | 02AFEE            | 256                                  | -         |                         |                        |            |                         |                         |       |           |         |

|              | 0557EE            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| FICD         | 0057F0            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

| TIOD         | 00AFF0            | 64                                   | -         |                         |                        |            |                         |                         |       |           |         |

|              | 0157F0            | 128                                  | -         | Reserved <sup>(3)</sup> |                        | JTAGEN     | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> |       |           | 1.0>    |

|              | 01371 0<br>02AFF0 | 256                                  | _         | Reserveu.               | _                      | JIAGEN     | Keselveu.               | Reserved                | _     | ICS<1:    | 1.0>    |

|              | 02AFF0<br>0557F0  | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| 5000         |                   |                                      |           |                         |                        |            |                         |                         |       |           |         |

| FPOR         | 0057F2            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFF2            | 64                                   | -         |                         |                        |            |                         | - ·(3)                  |       |           |         |

|              | 0157F2            | 128                                  |           | WDTV                    | VIN<1:0>               | ALTI2C2    | ALTI2C1                 | Reserved <sup>(3)</sup> | _     | _         | _       |

|              | 02AFF2            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557F2            | 512                                  |           |                         | 1                      |            |                         |                         |       |           |         |

| FWDT         | 0057F4            | 32                                   | -         |                         |                        |            |                         |                         |       |           |         |

|              | 00AFF4            | 64                                   |           |                         | WINDIS                 | PLLKEN     | WDTPRE                  | WDTPOST<3:0>            |       |           |         |

|              | 0157F4            | 128                                  | —         | FWDTEN                  |                        |            |                         |                         |       |           |         |

|              | 02AFF4            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557F4            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| FOSC         | 0057F6            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFF6            | 64                                   |           |                         | SM<1:0>                |            |                         |                         |       |           |         |

|              | 0157F6            | 128                                  | _         | FCKS                    |                        | /<1:0> IOL | IOL1WAY                 | —                       | _     | OSCIOFNC  | POSCMD< |

|              | 02AFF6            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557F6            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| FOSCSEL      | 0057F8            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFF8            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157F8            | 128                                  | _         | IESO                    | PWMLOCK <sup>(1)</sup> | _          | _                       | _                       | F     | NOSC<2:0> |         |

|              | 02AFF8            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557F8            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| FGS          | 0057FA            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFFA            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157FA            | 128                                  |           | _                       | _                      | _          |                         | _                       | _     | GCP       | GWRP    |

|              | 02AFFA            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557FA            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| Reserved     | 0057FC            | 312                                  |           |                         |                        |            |                         |                         |       |           |         |

| 1 10301 1000 | 0037FC            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              |                   |                                      |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157FC<br>02AFFC  | 128                                  |           |                         |                        | _          | _                       |                         | _     | _         | _       |

|              |                   | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557FC            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

| Reserved     | 057FFE            | 32                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 00AFFE            | 64                                   |           |                         |                        |            |                         |                         |       |           |         |

|              | 0157FE            | 128                                  | —         | —                       | —                      | —          | —                       | —                       | —     | —         | —       |

|              | 02AFFE            | 256                                  |           |                         |                        |            |                         |                         |       |           |         |

|              | 0557FE            | 512                                  |           |                         |                        |            |                         |                         |       |           |         |

#### TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

**2:** This bit is reserved and must be programmed as '0'.

3: These bits are reserved and must be programmed as '1'.

| DC CHARACTERISTICS |                               |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                       |                 |  |  |  |

|--------------------|-------------------------------|---------------|-------------------------------------------------------|-----------------------|-----------------|--|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                 | Conditions            |                 |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                       | 32MC20X/50X and PIC2  | 4EP32GP/MC20X   |  |  |  |

| DC60d              | 30                            | 100           | μA                                                    | -40°C                 |                 |  |  |  |

| DC60a              | 35                            | 100           | μA                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b              | 150                           | 200           | μA                                                    | +85°C                 | 3.3V            |  |  |  |

| DC60c              | 250                           | 500           | μA                                                    | +125°C                |                 |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                       | 64MC20X/50X and PIC2  | 4EP64GP/MC20X   |  |  |  |

| DC60d              | 25                            | 100           | μA                                                    | -40°C                 |                 |  |  |  |

| DC60a              | 30                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 3.3V            |  |  |  |

| DC60c              | 350                           | 800           | μΑ                                                    | +125°C                |                 |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                        | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |  |

| DC60d              | 30                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |

| DC60a              | 35                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b              | 150                           | 350           | μΑ                                                    | +85°C                 | 5.5 V           |  |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                    | +125°C                |                 |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                        | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |  |

| DC60d              | 35                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |

| DC60a              | 40                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b              | 250                           | 450           | μΑ                                                    | +85°C                 | 0.0 V           |  |  |  |

| DC60c              | 1000                          | 1200          | μΑ                                                    | +125°C                |                 |  |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                        | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |  |

| DC60d              | 40                            | 100           | μΑ                                                    | -40°C                 |                 |  |  |  |

| DC60a              | 45                            | 100           | μΑ                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b              | 350                           | 800           | μΑ                                                    | +85°C                 | 0.0 V           |  |  |  |

| DC60c              | 1100                          | 1500          | μA                                                    | +125°C                |                 |  |  |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

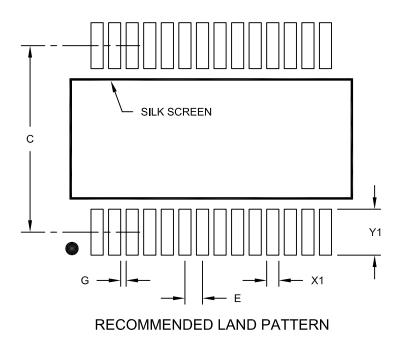

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimensior                | MIN         | NOM  | MAX      |      |

| Contact Pitch E          |             |      | 0.65 BSC |      |

| Contact Pad Spacing      |             |      | 7.20     |      |

| Contact Pad Width (X28)  | X1          |      |          | 0.45 |

| Contact Pad Length (X28) | Y1          |      |          | 1.75 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

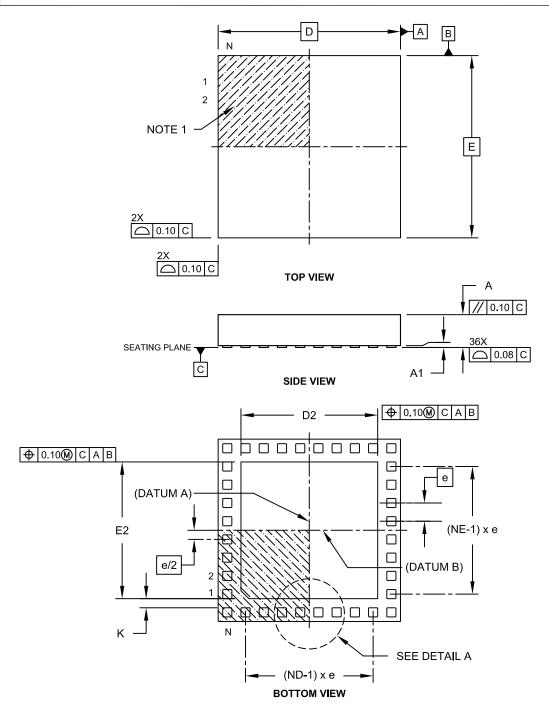

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | N      | MILLIMETERS |          |      |  |

|------------------------|--------|-------------|----------|------|--|

| Dimension              | Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | N      |             | 64       |      |  |

| Pitch                  | е      |             | 0.50 BSC |      |  |

| Overall Height         | A      | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3     |             | 0.20 REF |      |  |

| Overall Width          | E      |             | 9.00 BSC |      |  |

| Exposed Pad Width      | E2     | 5.30        | 5.40     | 5.50 |  |

| Overall Length         | D      |             | 9.00 BSC |      |  |

| Exposed Pad Length     | D2     | 5.30        | 5.40     | 5.50 |  |

| Contact Width          | b      | 0.20        | 0.25     | 0.30 |  |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K      | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

## TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                 | Update Description                                                                                                                                                       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |

## **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                                                                                |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                       |

| Section 30.0 "Electrical<br>Characteristics"                                                                                                                            | Updated the VBOR specifications and/or its related note in the following electrical<br>characteristics tables:<br>• Table 30-1<br>• Table 30-4<br>• Table 30-12<br>• Table 30-14<br>• Table 30-15<br>• Table 30-16<br>• Table 30-56<br>• Table 30-57<br>• Table 30-58<br>• Table 30-59<br>• Table 30-60 |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support