Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

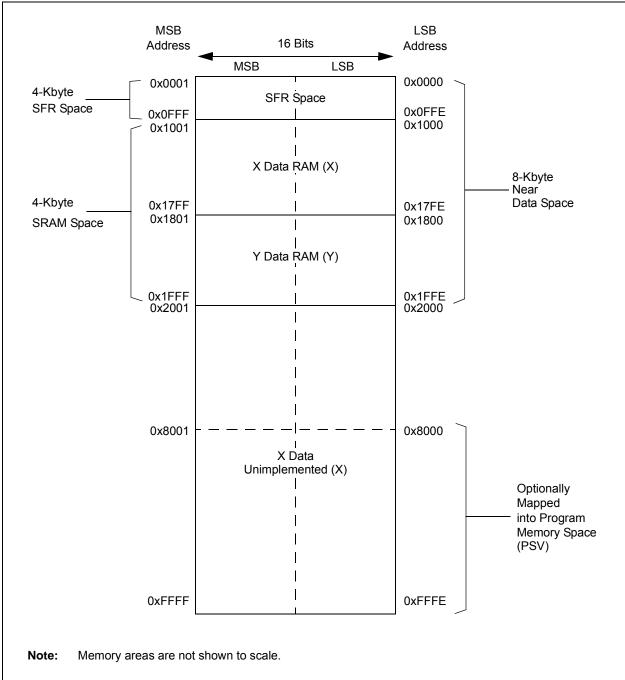

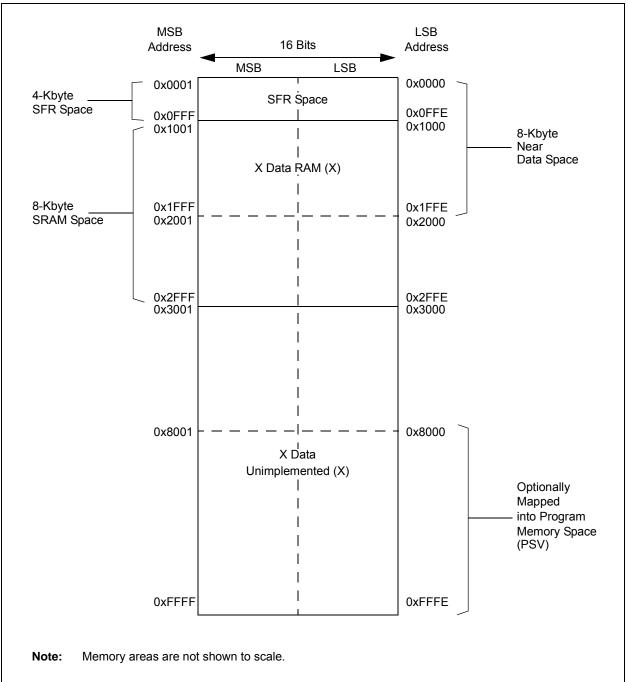

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

#### 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:( | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | —           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | —      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

#### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

#### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

#### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0                                                                | R/W-0     | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------------------------------------------------------------|-----------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|--|

|                                                                      |           |                  | PDC   | <15:8>                                  |       |       |       |  |  |  |

| bit 15                                                               |           |                  |       |                                         |       |       | bit 8 |  |  |  |

|                                                                      |           |                  |       |                                         |       |       |       |  |  |  |

| R/W-0                                                                | R/W-0     | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                                                                      | PDCx<7:0> |                  |       |                                         |       |       |       |  |  |  |

| bit 7                                                                |           |                  |       |                                         |       |       | bit 0 |  |  |  |

|                                                                      |           |                  |       |                                         |       |       |       |  |  |  |

| Legend:                                                              |           |                  |       |                                         |       |       |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |           |                  |       |                                         |       |       |       |  |  |  |

| -n = Value at P                                                      | POR       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

#### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | PHAS  | Ex<15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | PHAS  | SEx<7:0>                                |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

#### REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       5ID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       -       -       EID17       EID16       bit 0       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                                          |                                |               |                  |                  |                 |                  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------------------|---------------|------------------|------------------|-----------------|------------------|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                          | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x            |  |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       Ignores Extinct bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10         | SID9                                                                     | SID8                           | SID7          | SID6             | SID5             | SID4            | SID3             |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        | ÷                                                                        |                                |               |                  |                  |                 | bit 8            |  |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                |               |                  |                  |                 |                  |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0         EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-x         | R/W-x                                                                    | R/W-x                          | U-0           | R/W-x            | U-0              | R/W-x           | R/W-x            |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                           | _             | EXIDE            |                  | EID17           | EID16            |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Matches bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7         |                                                                          |                                |               |                  |                  |                 | bit 0            |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Message Sit, SIDE       5         bit 2       Unimplemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 4       Unimplemented: Read as '0'         bit 1-0       EID         if MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                          |                                |               |                  |                  |                 |                  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         o = Message address bit, SIDx, must be '1' to match filter       0' = Bit is cleared       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:       |                                                                          |                                |               |                  |                  |                 |                  |  |  |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | e bit                                                                    | W = Writable                   | bit           | U = Unimpler     | nented bit, read | d as '0'        |                  |  |  |

| 1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                      | '1' = Bit is set               |               | '0' = Bit is cle | ared             | x = Bit is unkr | = Bit is unknown |  |  |

| If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 4         | 0 = Message                                                              | address bit, SI                | Dx, must be ' |                  |                  |                 |                  |  |  |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | <u>If MIDE = 1:</u><br>1 = Matches<br>0 = Matches<br><u>If MIDE = 0:</u> | only messages<br>only messages | with Extende  |                  |                  |                 |                  |  |  |

| 1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2         | Unimplemen                                                               | ted: Read as '                 | כ'            |                  |                  |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 1-0       | EID<17:16>:                                                              | Extended Iden                  | tifier bits   |                  |                  |                 |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | •                                                                        |                                |               |                  |                  |                 |                  |  |  |

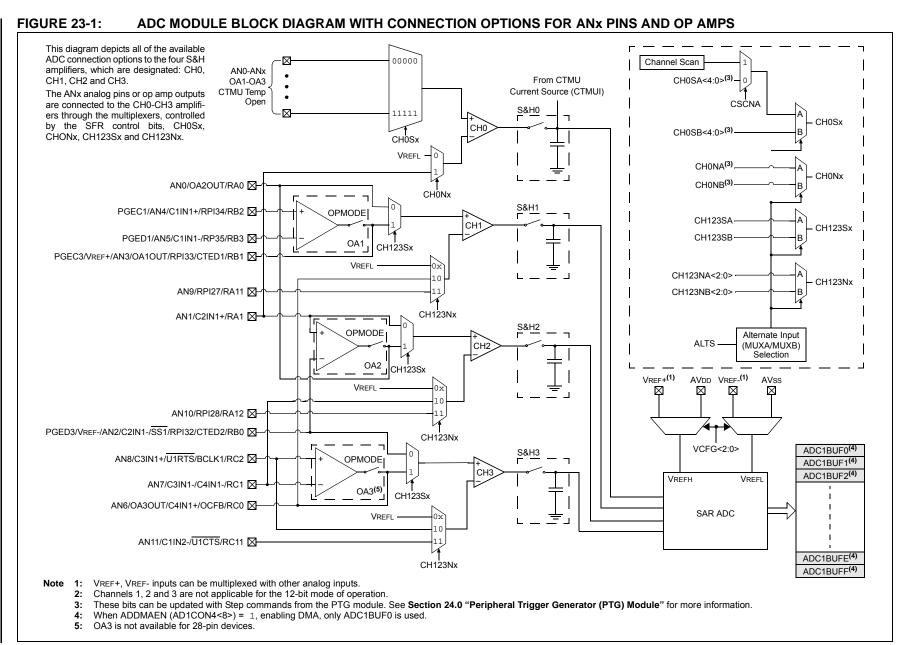

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)