#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

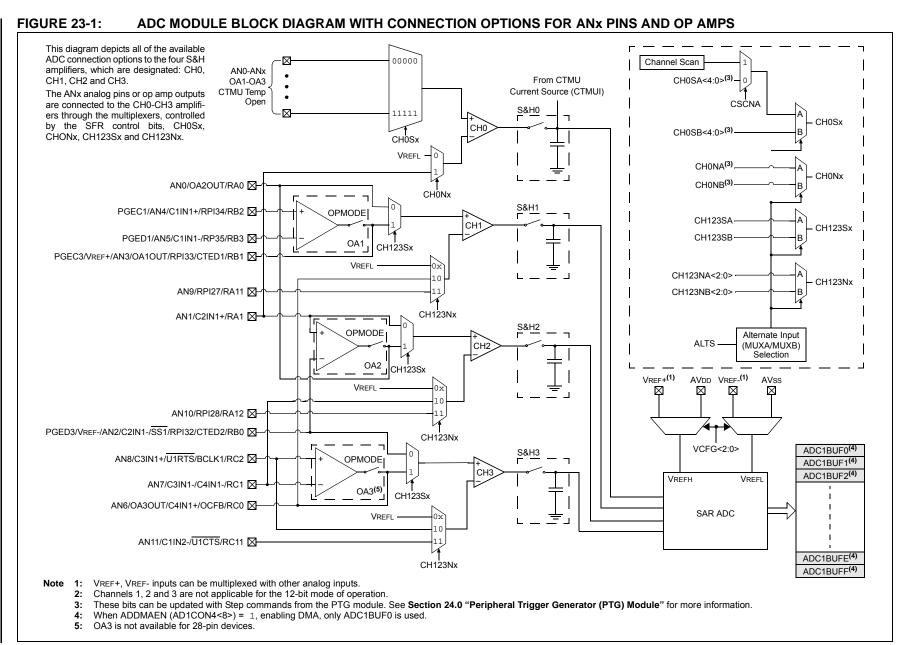

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

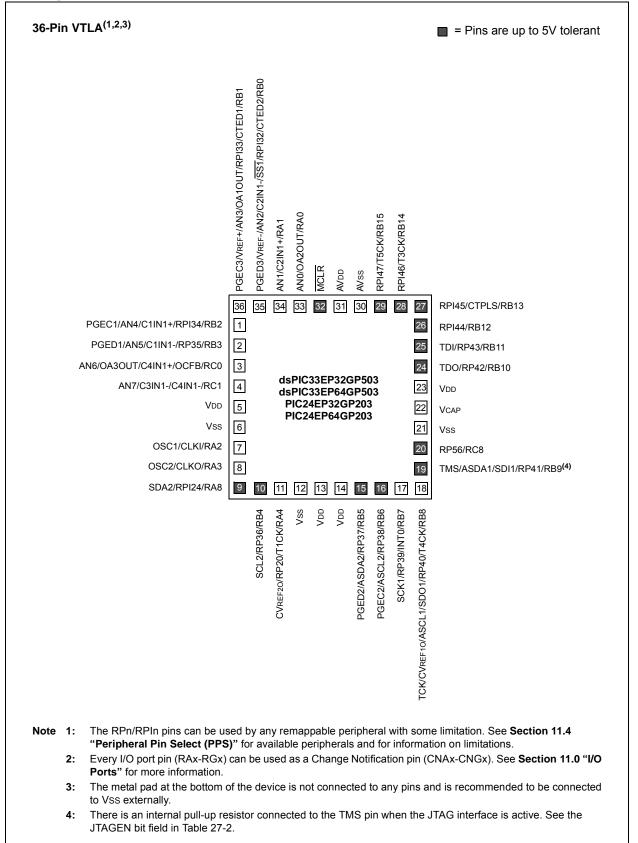

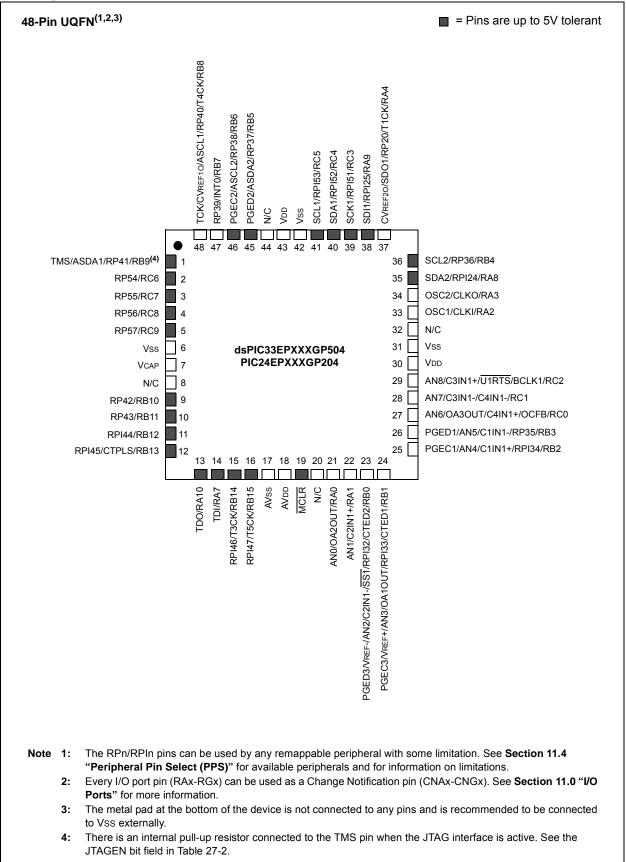

### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

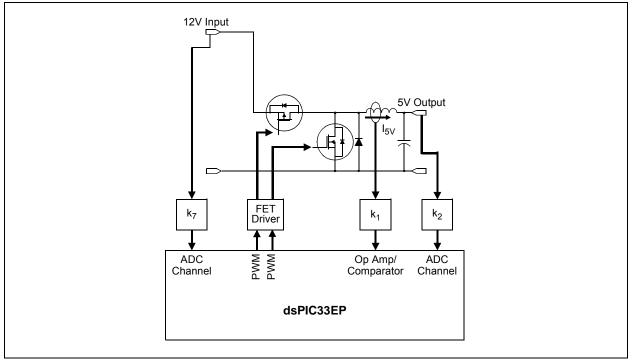

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

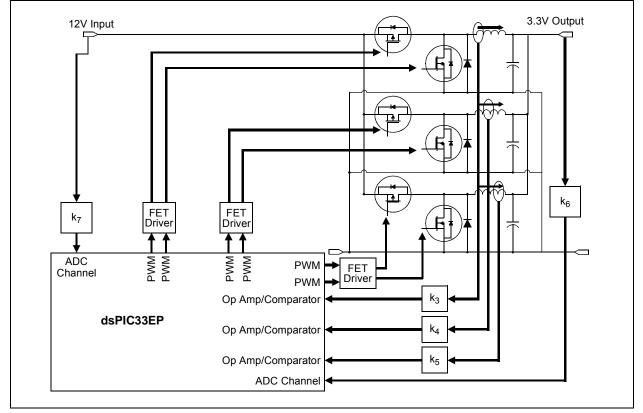

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7       | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|-------------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _           | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _           | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _           |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR    | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —           | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —           | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _           | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       | VECNUM<7:0> |         |             |         | 0000    |        |             |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

### 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

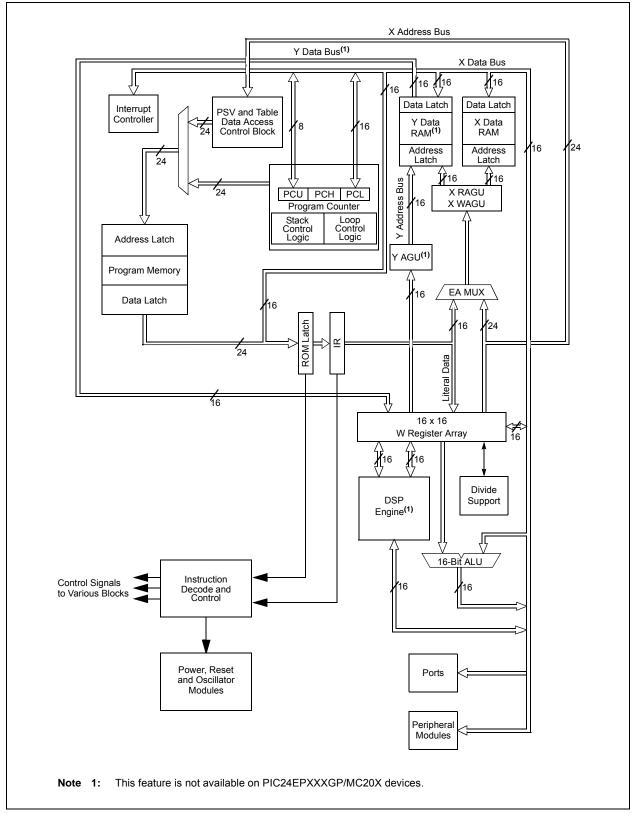

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

### © 2011-2013 Microchip Technology Inc.

## FIGURE 9-2: PLL BLOCK DIAGRAM

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                    |                                   |  |  |  |  |  |

|--------------|------------------------|-------------------------------------------------------------------------------|------------------------------------|-----------------------------------|--|--|--|--|--|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit, read as '0' |                                   |  |  |  |  |  |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared               | x = Bit is unknown                |  |  |  |  |  |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                    |                                   |  |  |  |  |  |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                    |                                   |  |  |  |  |  |

| bit 14       | •                      | mented: Read as '0'                                                           |                                    |                                   |  |  |  |  |  |

| bit 13       | -                      | TSIDL: Timery Stop in Idle Mode bit <sup>(2)</sup>                            |                                    |                                   |  |  |  |  |  |

|              | 1 = Disco              |                                                                               | hen device enters Idle mode        |                                   |  |  |  |  |  |

| bit 12-7     | Unimple                | Unimplemented: Read as '0'                                                    |                                    |                                   |  |  |  |  |  |

| bit 6        | TGATE:                 | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup>        |                                    |                                   |  |  |  |  |  |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                    |                                   |  |  |  |  |  |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                    |                                   |  |  |  |  |  |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>  |                                   |  |  |  |  |  |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                    |                                   |  |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                    |                                   |  |  |  |  |  |

|              | 01 = 1.8               |                                                                               |                                    |                                   |  |  |  |  |  |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                    |                                   |  |  |  |  |  |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                              |                                   |  |  |  |  |  |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)               |                                   |  |  |  |  |  |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                    |                                   |  |  |  |  |  |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e     | ffect on Timery operation; all ti |  |  |  |  |  |

|              |                        |                                                                               |                                    |                                   |  |  |  |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>MxL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

## REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| R/W-0         | R/W-0                                                                                                  | R/W-0                                  | U-0        | U-0                  | U-0             | U-0                | U-0    |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|----------------------------------------|------------|----------------------|-----------------|--------------------|--------|--|--|--|

| FRMEN         | SPIFSD                                                                                                 | FRMPOL                                 | —          | —                    | _               | —                  | —      |  |  |  |

| bit 15        |                                                                                                        |                                        |            |                      |                 |                    | bit 8  |  |  |  |

|               |                                                                                                        |                                        |            |                      |                 |                    |        |  |  |  |

| U-0           | U-0                                                                                                    | U-0                                    | U-0        | U-0                  | U-0             | R/W-0              | R/W-0  |  |  |  |

| —             | —                                                                                                      | —                                      | —          | —                    | _               | FRMDLY             | SPIBEN |  |  |  |

| bit 7         |                                                                                                        |                                        |            |                      |                 |                    | bit 0  |  |  |  |

|               |                                                                                                        |                                        |            |                      |                 |                    |        |  |  |  |

| Legend:       |                                                                                                        |                                        |            |                      |                 |                    |        |  |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable b                         | pit        | U = Unimpler         | nented bit, rea | ad as '0'          |        |  |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set                       |            | '0' = Bit is cleared |                 | x = Bit is unknown |        |  |  |  |

|               |                                                                                                        |                                        |            |                      |                 |                    |        |  |  |  |

| bit 15        |                                                                                                        | med SPIx Suppo                         |            |                      |                 |                    |        |  |  |  |

|               |                                                                                                        | SPIx support is e<br>SPIx support is d |            | sx pin is used as    | Frame Sync      | pulse input/outpu  | ıt)    |  |  |  |

| bit 14        |                                                                                                        | me Sync Pulse I                        |            | ontrol bit           |                 |                    |        |  |  |  |

|               | 1 = Frame S                                                                                            | ync pulse input (                      | slave)     |                      |                 |                    |        |  |  |  |

|               |                                                                                                        | ync pulse output                       | . ,        |                      |                 |                    |        |  |  |  |

| bit 13        |                                                                                                        | FRMPOL: Frame Sync Pulse Polarity bit  |            |                      |                 |                    |        |  |  |  |

|               | 1 = Frame Sync pulse is active-high<br>0 = Frame Sync pulse is active-low                              |                                        |            |                      |                 |                    |        |  |  |  |

| bit 12-2      | •                                                                                                      | nted: Read as '0                       |            |                      |                 |                    |        |  |  |  |

| bit 1         | -                                                                                                      |                                        |            | et hit               |                 |                    |        |  |  |  |

|               | <b>FRMDLY:</b> Frame Sync Pulse Edge Select bit<br>1 = Frame Sync pulse coincides with first bit clock |                                        |            |                      |                 |                    |        |  |  |  |

|               |                                                                                                        | ync pulse preced                       |            |                      |                 |                    |        |  |  |  |

| bit 0         | SPIBEN: Enhanced Buffer Enable bit                                                                     |                                        |            |                      |                 |                    |        |  |  |  |

|               | 1 = Enhance                                                                                            | d buffer is enabl                      | ed         |                      |                 |                    |        |  |  |  |

|               | 0 = Enhance                                                                                            | d buffer is disabl                     | ed (Standa | rd mode)             |                 |                    |        |  |  |  |

|               |                                                                                                        |                                        |            |                      |                 |                    |        |  |  |  |

### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |

|----------------|-------------------------------------|

|                | CONTROL REGISTER                    |

| R/W-0           |                                                                                             |                                                                                        |                                                                          |                  |                   |                   |              |

|-----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|-------------------|--------------|

|                 | U-0                                                                                         | R/W-0                                                                                  | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |

| HLMS            | —                                                                                           | OCEN                                                                                   | OCNEN                                                                    | OBEN             | OBNEN             | OAEN              | OANEN        |

| bit 15          |                                                                                             |                                                                                        |                                                                          |                  |                   |                   | bit          |

| R/W-0           | R/W-0                                                                                       | R/W-0                                                                                  | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |

| NAGS            | PAGS                                                                                        | ACEN                                                                                   | ACNEN                                                                    | ABEN             | ABNEN             | AAEN              | AANEN        |

| bit 7           |                                                                                             |                                                                                        |                                                                          | 1                |                   |                   | bit          |

| Legend:         |                                                                                             |                                                                                        |                                                                          |                  |                   |                   |              |

| R = Readable I  | bit                                                                                         | W = Writable                                                                           | bit                                                                      | U = Unimple      | mented bit, read  | l as '0'          |              |

| -n = Value at P | OR                                                                                          | '1' = Bit is set                                                                       |                                                                          | '0' = Bit is cle |                   | x = Bit is unki   | nown         |

|                 |                                                                                             |                                                                                        |                                                                          |                  |                   |                   |              |

| bit 15          | HLMS: High                                                                                  | or Low-Level N                                                                         | lasking Select                                                           | bits             |                   |                   |              |

|                 | •                                                                                           |                                                                                        | •                                                                        |                  | erted ('0') compa | rator signal from | n propagatin |

|                 |                                                                                             |                                                                                        |                                                                          |                  | erted ('1') compa |                   |              |

| bit 14          | Unimplemen                                                                                  | ted: Read as '                                                                         | 0'                                                                       |                  |                   |                   |              |

| bit 13          | OCEN: OR G                                                                                  | ate C Input Er                                                                         | able bit                                                                 |                  |                   |                   |              |

|                 | 1 = MCI is co                                                                               | nnected to OR                                                                          | gate                                                                     |                  |                   |                   |              |

|                 | 0 = MCI is not connected to OR gate                                                         |                                                                                        |                                                                          |                  |                   |                   |              |

| bit 12          |                                                                                             | Gate C Input I                                                                         |                                                                          | e bit            |                   |                   |              |

|                 | 1 = Inverted MCI is connected to OR gate                                                    |                                                                                        |                                                                          |                  |                   |                   |              |

|                 | 0 = Inverted MCI is not connected to OR gate                                                |                                                                                        |                                                                          |                  |                   |                   |              |

| bit 11          |                                                                                             | ate B Input En                                                                         |                                                                          |                  |                   |                   |              |

|                 |                                                                                             | nnected to OR<br>t connected to                                                        | •                                                                        |                  |                   |                   |              |

| bit 10          |                                                                                             | Gate B Input I                                                                         | •                                                                        | a hit            |                   |                   |              |

|                 |                                                                                             | VBI is connect                                                                         |                                                                          |                  |                   |                   |              |

|                 |                                                                                             | MBI is not conr                                                                        | •                                                                        | ate              |                   |                   |              |

| bit 9           |                                                                                             | ate A Input En                                                                         | -                                                                        |                  |                   |                   |              |

|                 |                                                                                             | nnected to OR                                                                          |                                                                          |                  |                   |                   |              |

|                 | 0 = MAI is no                                                                               | t connected to                                                                         | OR gate                                                                  |                  |                   |                   |              |

| bit 8           | OANEN: OR                                                                                   | Gate A Input I                                                                         | nverted Enable                                                           | e bit            |                   |                   |              |

|                 |                                                                                             | MAI is connect                                                                         |                                                                          |                  |                   |                   |              |

|                 |                                                                                             | MAI is not conr                                                                        | -                                                                        |                  |                   |                   |              |

| bit 7           |                                                                                             | Gate Output Ir                                                                         |                                                                          |                  |                   |                   |              |

|                 |                                                                                             | ANDI is conneo<br>ANDI is not cor                                                      |                                                                          |                  |                   |                   |              |

|                 |                                                                                             |                                                                                        |                                                                          | 9                |                   |                   |              |

| bit 6           | PAGS: AND Gate Output Enable bit<br>1 = ANDI is connected to OR gate                        |                                                                                        |                                                                          |                  |                   |                   |              |

| bit 6           |                                                                                             | •                                                                                      |                                                                          |                  |                   |                   |              |

| bit 6           | 1 = ANDI is c                                                                               | •                                                                                      | R gate                                                                   |                  |                   |                   |              |

| bit 6<br>bit 5  | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND                                                 | onnected to O<br>ot connected t<br>Gate C Input E                                      | R gate<br>o OR gate<br>inable bit                                        |                  |                   |                   |              |

|                 | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co                                | onnected to O<br>ot connected t<br>Gate C Input E<br>nnected to AN                     | R gate<br>o OR gate<br>inable bit<br>D gate                              |                  |                   |                   |              |

| bit 5           | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co<br>0 = MCI is no               | onnected to O<br>lot connected t<br>Gate C Input E<br>nnected to AN<br>it connected to | R gate<br>o OR gate<br>inable bit<br>D gate<br>AND gate                  |                  |                   |                   |              |

|                 | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co<br>0 = MCI is no<br>ACNEN: AND | onnected to O<br>ot connected t<br>Gate C Input E<br>nnected to AN                     | R gate<br>o OR gate<br>inable bit<br>D gate<br>AND gate<br>Inverted Enab |                  |                   |                   |              |

### 26.1 Overview

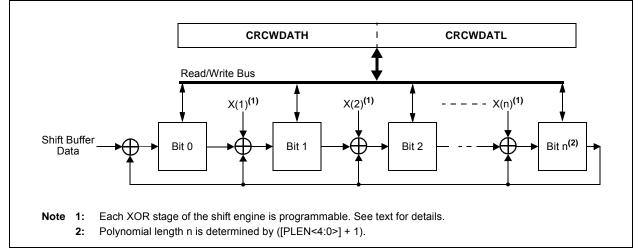

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

# TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |  |  |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |  |  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |  |  |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |  |  |  |  |

### 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

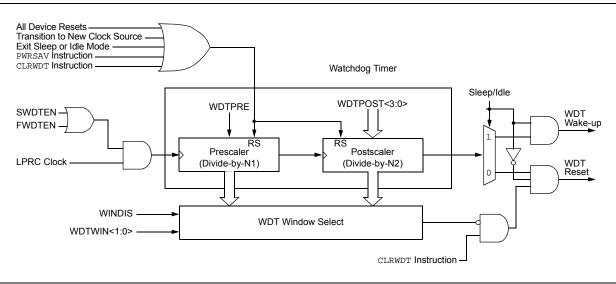

### 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 27-2: WDT BLOCK DIAGRAM

## 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

### 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

### 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

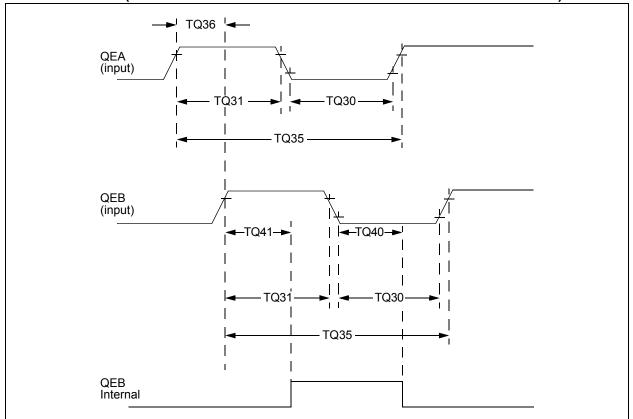

### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    |                     |      |       | tions: 3.0V to 3.6V<br>$0^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$0^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |

|--------------------|--------|----------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                                       |  |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy               |      | ns    |                                                                                                                                  |  |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy               | —    | ns    |                                                                                                                                  |  |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY              | _    | ns    |                                                                                                                                  |  |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY               | —    | ns    |                                                                                                                                  |  |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy         | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b>                                                                          |  |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy         | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b>                                                                          |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-33                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                     | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-36                                           | 1   | 0   | 0   |  |

| 11 MHz               | _                                        | —                                           | Table 30-37                                           | 1   | 1   | 0   |  |

| 15 MHz               | —                                        | —                                           | Table 30-38                                           | 0   | 1   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-39                                           | 0   | 0   | 0   |  |

### TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

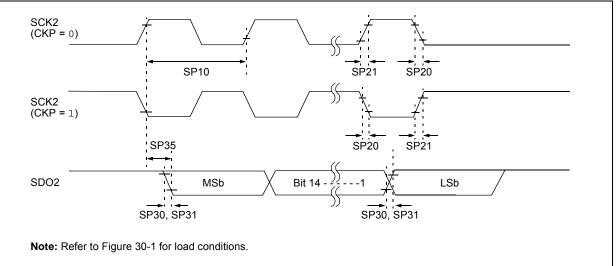

### FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS