#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡X/EI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp502-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

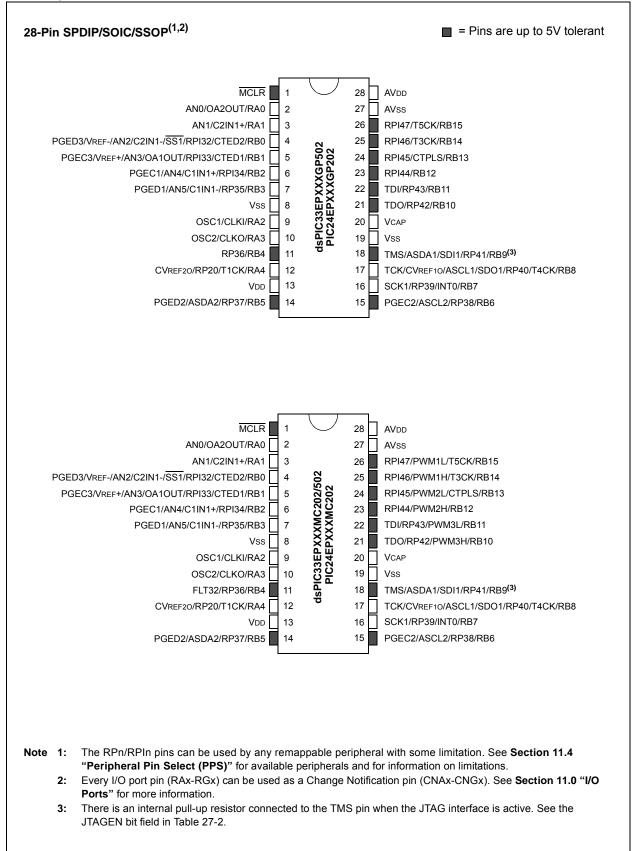

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### **Pin Diagrams**

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00             |        |        |              | 011 401    |        |       | 20/00/     |       |       |        |         |          |          | -     | r     |               |

|-----------|-------|------------------|--------|--------|--------------|------------|--------|-------|------------|-------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15           | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8      | Bit 7 | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |                  |        |        |              |            |        |       | W0 (WR     | EG)   |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |                  |        |        |              |            |        |       | W1         |       |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |                  |        |        |              |            |        |       | W2         |       |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |                  |        |        |              |            |        |       | W3         |       |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |                  | W4     |        |              |            |        |       |            |       |       | xxxx   |         |          |          |       |       |               |

| W5        | 000A  |                  |        |        |              |            |        |       | W5         |       |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |                  |        |        |              |            |        |       | W6         |       |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |                  |        |        |              |            |        |       | W7         |       |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |                  |        |        |              |            |        |       | W8         |       |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |                  |        |        |              |            |        |       | W9         |       |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |                  |        |        |              |            |        |       | W10        |       |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |                  |        |        |              |            |        |       | W11        |       |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |                  |        |        |              |            |        |       | W12        |       |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |                  |        |        |              |            |        |       | W13        |       |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |                  | W14 x  |        |              |            |        |       |            |       | xxxx  |        |         |          |          |       |       |               |

| W15       | 001E  |                  | W15    |        |              |            |        |       |            | xxxx  |       |        |         |          |          |       |       |               |

| SPLIM     | 0020  |                  |        |        |              |            |        |       | SPLI       | N     |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |                  |        |        |              |            |        |       | ACCA       | L     |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |                  |        |        |              |            |        |       | ACCA       | H     |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |                  |        | Si     | gn Extensior | n of ACCA< | 39>    |       |            |       |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |                  |        |        |              |            |        |       | ACCB       | L     |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |                  |        |        |              |            |        |       | ACCB       | Н     |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |                  |        | Si     | gn Extensior | n of ACCB< | 39>    |       |            |       |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |                  |        |        |              |            |        | F     | PCL<15:0>  |       |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _                | _      | _      | —            | _          | _      | —     | _          | _     |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _                | _      | _      | _            | _          | _      |       |            |       |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _                |        | _      | —            |            | _      | _     |            |       |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  | RCOUNT<15:0>     |        |        |              |            |        |       | 0000       |       |       |        |         |          |          |       |       |               |

| DCOUNT    | 0038  | DCOUNT<15:0>     |        |        |              |            |        |       | 0000       |       |       |        |         |          |          |       |       |               |

| DOSTARTL  | 003A  | DOSTARTL<15:1> — |        |        |              |            |        |       | 0000       |       |       |        |         |          |          |       |       |               |

| DOSTARTH  | 003C  | _                | —      | —      | _            | —          | —      | —     | _          | _     | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |                  |        |        |              |            |        | DO    | ENDL<15:1> | >     |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _                | —      | —      | —            | —          | —      | _     | —          | —     | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |                  |        |        |              |            |        |       |            |       |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | -     |       |       | -     | —     | —     | _     | _     |       | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |  |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|--|

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |  |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

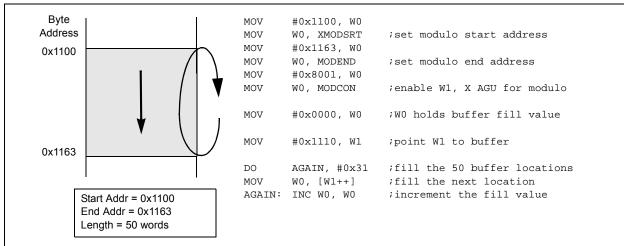

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

### FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

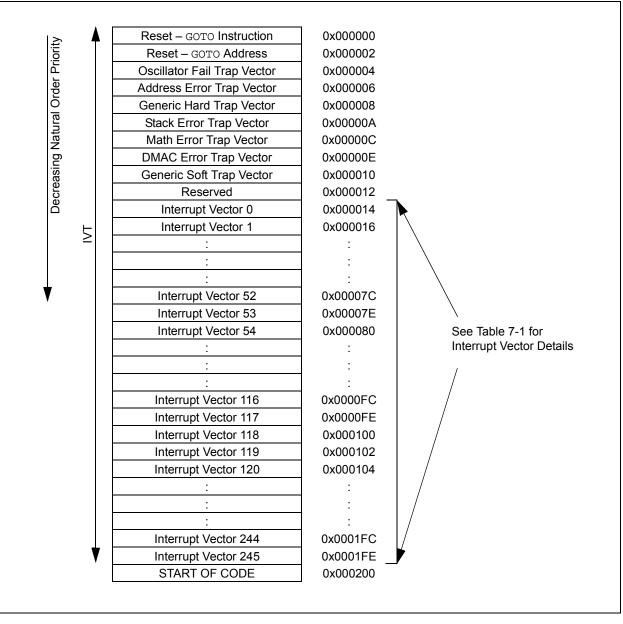

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled

- 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit<sup>(2)</sup> 1 = ECAN1 module is disabled 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit 1 = ADC1 module is disabled 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                                                   | R/W-0                                  | R/W-0                                                      | R/W-0             | R/W-0                  | U-0              | R/W-0         |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------|-------------------|------------------------|------------------|---------------|--|--|--|--|

|               | 0-0                                                                                                                                   | OCSIDL                                 | OCTSEL2                                                    | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |  |  |  |  |

| <br>bit 15    |                                                                                                                                       | COOIDE                                 |                                                            | OUTOLLI           | OUTOLLU                |                  | bit 8         |  |  |  |  |

| Sit 10        |                                                                                                                                       |                                        |                                                            |                   |                        |                  | bit 0         |  |  |  |  |

| R/W-0         | U-0                                                                                                                                   | R/W-0, HSC                             | R/W-0, HSC                                                 | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |  |  |  |  |

| ENFLT         |                                                                                                                                       | OCFLTB                                 | OCFLTA                                                     | TRIGMODE          | OCM2                   | OCM1             | OCM0          |  |  |  |  |

| bit 7         |                                                                                                                                       |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

| Legend:       |                                                                                                                                       | HSC = Hardw                            | are Settable/Cl                                            | earable bit       |                        |                  |               |  |  |  |  |

| R = Read      | able bit                                                                                                                              | W = Writable I                         | <i>N</i> = Writable bit U = Unimplemented bit, read as '0' |                   |                        |                  |               |  |  |  |  |

| -n = Value    | e at POR                                                                                                                              | '1' = Bit is set                       |                                                            | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |  |  |  |  |

|               |                                                                                                                                       |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

| bit 15-14     | Unimplemen                                                                                                                            | ted: Read as '0                        | )'                                                         |                   |                        |                  |               |  |  |  |  |

| bit 13        | OCSIDL: Out                                                                                                                           | tput Compare x                         | Stop in Idle Mo                                            | de Control bit    |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ompare x Halts                         |                                                            |                   |                        |                  |               |  |  |  |  |

|               | •                                                                                                                                     | compare x conti                        | •                                                          |                   | ode                    |                  |               |  |  |  |  |

| bit 12-10     |                                                                                                                                       | )>: Output Com                         | pare x Clock S                                             | elect bits        |                        |                  |               |  |  |  |  |

|               | 111 = Periph<br>110 = Reserv                                                                                                          | eral clock (FP)                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               | 101 = PTGO                                                                                                                            |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                        |                                                            |                   | hronous clock          | is supported)    |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ( is the clock so<br>( is the clock so |                                                            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                        |                                                            |                   |                        |                  |               |  |  |  |  |

| bit 9         | Unimplemen                                                                                                                            | ted: Read as '0                        | )'                                                         |                   |                        |                  |               |  |  |  |  |

| bit 8         | ENFLTB: Fau                                                                                                                           | ult B Input Enab                       | le bit                                                     |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | compare Fault B<br>compare Fault B     |                                                            |                   |                        |                  |               |  |  |  |  |

| bit 7         | -                                                                                                                                     | ult A Input Enab                       |                                                            |                   |                        |                  |               |  |  |  |  |

|               | 1 = Output C                                                                                                                          | ompare Fault A<br>compare Fault A      | input (OCFA)                                               |                   |                        |                  |               |  |  |  |  |

| bit 6         | •                                                                                                                                     | ted: Read as '0                        | • • •                                                      |                   |                        |                  |               |  |  |  |  |

| bit 5         | OCFLTB: PW                                                                                                                            | M Fault B Con                          | dition Status bit                                          |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ult B condition of Fault B condition   |                                                            |                   |                        |                  |               |  |  |  |  |

| bit 4         | OCFLTA: PWM Fault A Condition Status bit                                                                                              |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul> |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

| Note 1:       | OCxR and OCxF                                                                                                                         | 29 are double h                        | uffered in D\\//                                           | / mode only       |                        |                  |               |  |  |  |  |

| Note 1.<br>2: | Each Output Cor                                                                                                                       |                                        |                                                            | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |  |  |  |  |

| 2.            | Generator (PTG                                                                                                                        |                                        |                                                            |                   |                        | 5.1 2 7.0 1 611p |               |  |  |  |  |

|               | PTGO4 = OC1                                                                                                                           | -                                      |                                                            |                   |                        |                  |               |  |  |  |  |

|               | PTGO5 = OC2                                                                                                                           |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               | PTGO6 = OC3<br>PTGO7 = OC4                                                                                                            |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       |                                        |                                                            |                   |                        |                  |               |  |  |  |  |

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit ( |

| Legena.           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

## REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|---------------|-------|-------|-------|-------|-------|-------|

|        | PTGHOLD<15:8> |       |       |       |       |       |       |

| bit 15 |               |       |       |       |       |       | bit 8 |

| R/W-0   | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|--------------|-------|-------|-------|-------|-------|-------|

|         | PTGHOLD<7:0> |       |       |       |       |       |       |

| bit 7 b |              |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

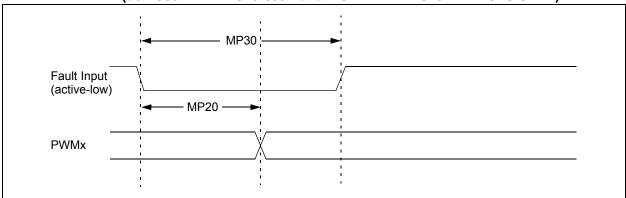

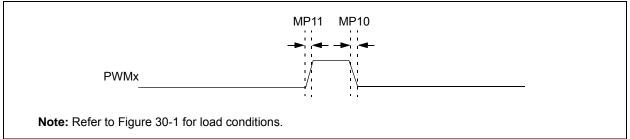

#### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                    |

|--------------------|--------|-------------------------------------|-------------------------------------------------------|------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min.                                                  | Тур. | Max. | Units | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                                       | —    | _    | ns    | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                     | —    | _    | ns    | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                     | _    | 15   | ns    |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                    | —    | _    | ns    |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

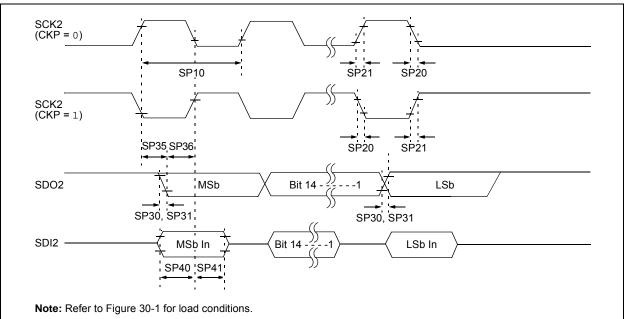

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   |      | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

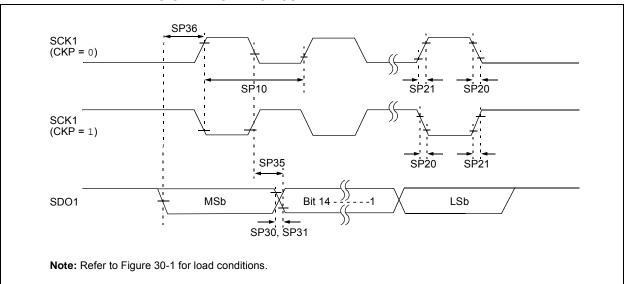

#### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

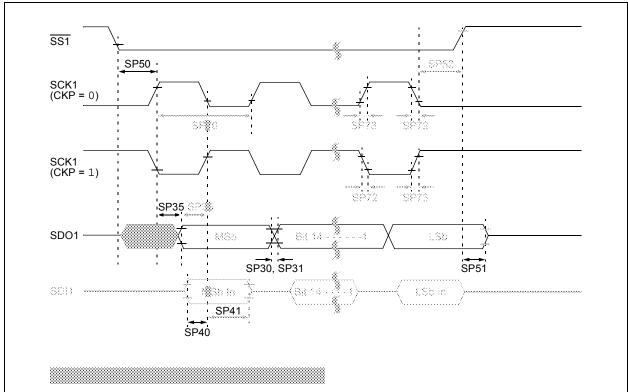

#### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP10               | FscP                  | Maximum SCK1 Frequency                       | —                                                                                                                                                                                                                                                                                       |                     | 15   | MHz   | (Note 3)                       |  |

| SP20               | TscF                  | SCK1 Output Fall Time                        | -                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP21               | TscR                  | SCK1 Output Rise Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | -                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                      |                     |      | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

#### FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### TABLE 31-11: INTERNAL RC ACCURACY

| AC CH        | ARACTERISTICS                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |       |                                           |                |  |

|--------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------------------------------------------|----------------|--|

| Param<br>No. | Characteristic                     | Min                                                                                                                                 | Тур | Max | Units | Conditions                                |                |  |

|              | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                     |     |     |       |                                           |                |  |

| HF21         | LPRC                               | -30                                                                                                                                 | _   | +30 | %     | $-40^{\circ}C \leq TA \leq +150^{\circ}C$ | VDD = 3.0-3.6V |  |

Note 1: Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TwDT). See Section 27.5 "Watchdog Timer (WDT)" for more information.

## **Revision F (November 2012)**

Removed "Preliminary" from data sheet footer.

### **Revision G (March 2013)**

This revision includes the following global changes:

- changes "FLTx" pin function to "FLTx" on all occurrences

- adds Section 31.0 "High-Temperature Electrical Characteristics" for high-temperature (+150°C) data

This revision also includes minor typographical and formatting changes throughout the text.

Other major changes are referenced by their respective section in Table A-5.

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Cover Section                                                        | <ul> <li>Changes internal oscillator specification to 1.0%</li> <li>Changes I/O sink/source values to 12 mA or 6 mA</li> <li>Corrects 44-pin VTLA pin diagram (pin 32 now shows as 5V tolerant)</li> </ul>                                                                                                                                                                           |  |  |  |  |  |

| Section 4.0 "Memory<br>Organization"                                 | <ul> <li>Deletes references to Configuration Shadow registers</li> <li>Corrects the spelling of the JTAGIP and PTGWDTIP bits throughout</li> <li>Corrects the Reset value of all IOCON registers as C000h</li> <li>Adds footnote to Table 4-42 to indicate the absence of Comparator 3 in 28-pin devices</li> </ul>                                                                  |  |  |  |  |  |

| Section 6.0 "Resets"                                                 | <ul> <li>Removes references to cold and warm Resets, and clarifies the initial configuration<br/>the device clock source on all Resets</li> </ul>                                                                                                                                                                                                                                    |  |  |  |  |  |

| Section 7.0 "Interrupt<br>Controller"                                | orrects the definition of GIE as "Global Interrupt Enable" (not "General")                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Section 9.0 "Oscillator<br>Configuration"                            | <ul> <li>Clarifies the behavior of the CF bit when cleared in software</li> <li>Removes POR behavior footnotes from all control registers</li> <li>Corrects the tuning range of the TUN&lt;5:0&gt; bits in Register 9-4 to an overall range ±1.5%</li> </ul>                                                                                                                         |  |  |  |  |  |

| Section 13.0 "Timer2/3 and Timer4/5"                                 | <ul> <li>Clarifies the presence of the ADC Trigger in 16-bit Timer3 and Timer5, as well as the<br/>32-bit timers</li> </ul>                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Section 15.0 "Output<br>Compare"                                     | <ul> <li>Corrects the first trigger source for SYNCSEL&lt;4:0&gt; (OCxCON2&lt;4:0&gt;) as OCxRS<br/>match</li> </ul>                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Section 16.0 "High-Speed<br>PWM Module"                              | <ul> <li>Clarifies the source of the PWM interrupts in Figure 16-1</li> <li>Corrects the Reset states of IOCONx&lt;15:14&gt; in Register 16-13 as '11'</li> </ul>                                                                                                                                                                                                                    |  |  |  |  |  |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI)<br>Module"       | <ul> <li>Clarifies the operation of the IMV&lt;1:0&gt; bits (QEICON&lt;9:8&gt;) with updated text and additional notes</li> <li>Corrects the first prescaler value for QFVDIV&lt;2:0&gt; (QEI10C&lt;13:11&gt;), now 1:128</li> </ul>                                                                                                                                                 |  |  |  |  |  |

| Section 23.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter<br>(ADC)" | <ul> <li>Adds note to Figure 23-1 that Op Amp 3 is not available in 28-pin devices</li> <li>Changes "sample clock" to "sample trigger" in AD1CON1 (Register 23-1)</li> <li>Clarifies footnotes on op amp usage in Registers 23-5 and 23-6</li> </ul>                                                                                                                                 |  |  |  |  |  |

| Section 25.0 "Op Amp/<br>Comparator Module"                          | <ul> <li>Adds Note text to indicate that Comparator 3 is unavailable in 28-pin devices</li> <li>Splits Figure 25-1 into two figures for clearer presentation (Figure 25-1 for Op amp/<br/>Comparators 1 through 3, Figure 25-2 for Comparator 4). Subsequent figures are<br/>renumbered accordingly.</li> <li>Corrects reference description in xxxxx (now (AVDD+AVSS)/2)</li> </ul> |  |  |  |  |  |

| Section 27.0 "Special Features"                                      | <ul> <li>Changes CMSTAT&lt;15&gt; in Register 25-1 to "PSIDL"</li> <li>Corrects the addresses of all Configuration bytes for 512 Kbyte devices</li> </ul>                                                                                                                                                                                                                            |  |  |  |  |  |

#### TABLE A-5: MAJOR SECTION UPDATES

### TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)