Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

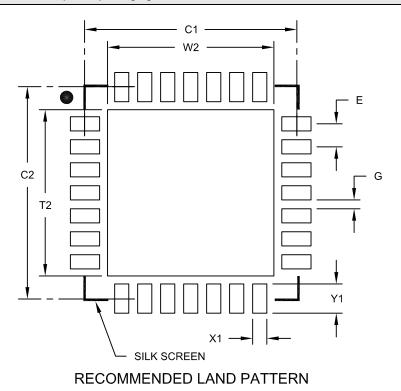

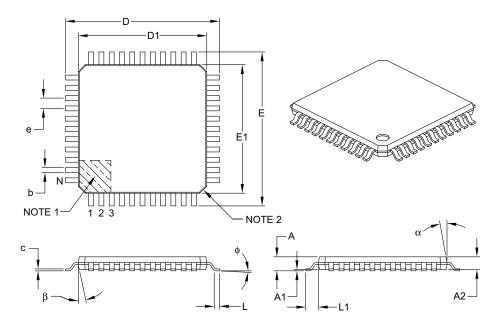

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp503-h-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |       |        |                   |        |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|--------|-------------------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |                   |        |        |        |        |              | Timer1       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        | Period Register 1 |        |        |        |        |              |              |               | FFFF         |       |        |       |       |       |       |               |

| T1CON       | 0104  | TON    | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |        |                   |        |        |        |        |              | Timer2       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |                   |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        | Timer3 Register   |        |        |        |        |              |              |               | xxxx         |       |        |       |       |       |       |               |

| PR2         | 010C  |        | Period Register 2 |        |        |        |        |              |              |               | FFFF         |       |        |       |       |       |       |               |

| PR3         | 010E  |        |                   |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | —                 | TSIDL  | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON    | -                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |        |                   | •      | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     |       | •     |       | xxxx          |

| TMR5HLD     | 0116  |        |                   |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                   |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |                   |        |        |        |        |              | Period F     | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |                   |        |        |        |        |              | Period F     | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | —                 | TSIDL  | —      | —      | —      | —            | _            | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _                 | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

### TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

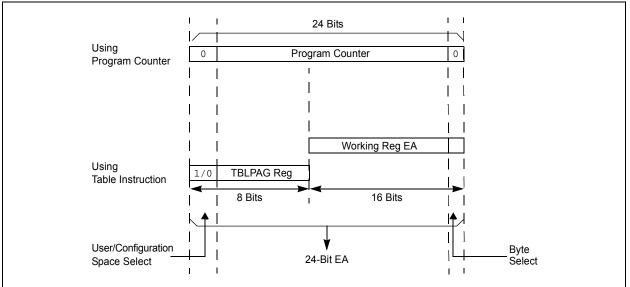

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

NOTES:

### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                        | U-0   | R/W-0          | R/W-0      | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|----------------------------------------------------------------------------|-------|----------------|------------|--------------|-----------------|----------|-------|--|--|--|

| —                                                                          | —     |                | DTRx<13:8> |              |                 |          |       |  |  |  |

| bit 15                                                                     |       |                |            |              |                 |          | bit 8 |  |  |  |

|                                                                            |       |                |            |              |                 |          |       |  |  |  |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0      | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|                                                                            |       |                | DTR        | x<7:0>       |                 |          |       |  |  |  |

| bit 7                                                                      |       |                |            |              |                 |          | bit 0 |  |  |  |

|                                                                            |       |                |            |              |                 |          |       |  |  |  |

| Legend:                                                                    |       |                |            |              |                 |          |       |  |  |  |

| R = Readable                                                               | bit   | W = Writable b | bit        | U = Unimpler | nented bit, rea | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |            |              |                 |          | nown  |  |  |  |

### REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                                                                | U-0   | R/W-0          | R/W-0         | R/W-0           | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|--------------------------------------------------------------------|-------|----------------|---------------|-----------------|-----------------|----------|-------|--|--|--|

| _                                                                  | _     |                | ALTDTRx<13:8> |                 |                 |          |       |  |  |  |

| bit 15                                                             |       |                |               |                 |                 |          | bit 8 |  |  |  |

|                                                                    |       |                |               |                 |                 |          |       |  |  |  |

| R/W-0                                                              | R/W-0 | R/W-0          | R/W-0         | R/W-0           | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|                                                                    |       |                | ALTDT         | Rx<7:0>         |                 |          |       |  |  |  |

| bit 7                                                              |       |                |               |                 |                 |          | bit 0 |  |  |  |

| Legend:                                                            |       |                |               |                 |                 |          |       |  |  |  |

| R = Readable                                                       | bit   | W = Writable t | oit           | U = Unimplem    | ented bit, read | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |       |                |               | x = Bit is unkr | nown            |          |       |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

| R-0, HSC                                    | R-0, HSC  | U-0                                                      | U-0        | U-0          | R/C-0, HS                      | R-0, HSC                              | R-0, HSC |  |  |

|---------------------------------------------|-----------|----------------------------------------------------------|------------|--------------|--------------------------------|---------------------------------------|----------|--|--|

| ACKSTAT                                     | TRSTAT    | _                                                        | _          | — BCL        |                                | GCSTAT                                | ADD10    |  |  |

| bit 15                                      |           |                                                          |            |              |                                |                                       | bit 8    |  |  |

|                                             |           |                                                          |            |              |                                |                                       |          |  |  |

| R/C-0, HS                                   | R/C-0, HS | R-0, HSC                                                 | R/C-0, HSC | R/C-0, HSC   | R-0, HSC                       | R-0, HSC                              | R-0, HSC |  |  |

| IWCOL                                       | I2COV     | D_A                                                      | Р          | S R_W        |                                | RBF                                   | TBF      |  |  |

| bit 7                                       |           |                                                          |            |              |                                |                                       | bit 0    |  |  |

|                                             |           |                                                          |            |              |                                |                                       |          |  |  |

| Legend:                                     |           | C = Clearab                                              | le bit     | HS = Hardwa  | re Settable bit                | HSC = Hardware Settable/Clearable bit |          |  |  |

| R = Readable bit W = Writable bit U = Unimp |           |                                                          |            | U = Unimplem | Unimplemented bit, read as '0' |                                       |          |  |  |

| -n = Value at                               | POR       | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |            |              |                                |                                       |          |  |  |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### 22.2 **CTMU Control Registers**

| REGISTER                                                                                                                                                            | 22-1: CTM                                  | UCON1: CTM                                  | J CONTROI     | - REGISTER                         | 1        |                        |        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------|------------------------------------|----------|------------------------|--------|--|--|--|

| R/W-0                                                                                                                                                               | U-0                                        | R/W-0                                       | R/W-0         | R/W-0                              | R/W-0    | R/W-0                  | R/W-0  |  |  |  |

| CTMUEN                                                                                                                                                              | _                                          | CTMUSIDL                                    | CTMUSIDL TGEN |                                    | EDGSEQEN | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |  |

| bit 15                                                                                                                                                              |                                            |                                             |               |                                    |          |                        | bit 8  |  |  |  |

|                                                                                                                                                                     |                                            |                                             |               |                                    |          |                        |        |  |  |  |

| U-0                                                                                                                                                                 | U-0                                        | U-0                                         | U-0           | U-0                                | U-0      | U-0                    | U-0    |  |  |  |

|                                                                                                                                                                     | _                                          |                                             | _             | <u> </u>                           | <u> </u> |                        | _      |  |  |  |

| bit 7 bit 0                                                                                                                                                         |                                            |                                             |               |                                    |          |                        |        |  |  |  |

|                                                                                                                                                                     |                                            |                                             |               |                                    |          |                        |        |  |  |  |

| Legend:                                                                                                                                                             |                                            |                                             |               |                                    |          |                        |        |  |  |  |

| R = Readable                                                                                                                                                        | e bit                                      | W = Writable b                              | bit           | U = Unimplemented bit, read as '0' |          |                        |        |  |  |  |

| -n = Value at                                                                                                                                                       | POR                                        | '1' = Bit is set                            |               | '0' = Bit is cle                   | ared     | x = Bit is unknown     |        |  |  |  |

| bit 15                                                                                                                                                              |                                            | TMU Enable bit<br>is enabled<br>is disabled |               |                                    |          |                        |        |  |  |  |

| bit 14                                                                                                                                                              | Unimpleme                                  | nted: Read as '0                            | ,             |                                    |          |                        |        |  |  |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                                            |                                             |               |                                    |          |                        |        |  |  |  |

| bit 12                                                                                                                                                              | 12 <b>TGEN:</b> Time Generation Enable bit |                                             |               |                                    |          |                        |        |  |  |  |

#### DECISTED

| bit 9 | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul> |

| bit 8 | CTTRIG: ADC Trigger Control bit                                                                                         |

|       | <ul><li>1 = CTMU triggers ADC start of conversion</li><li>0 = CTMU does not trigger ADC start of conversion</li></ul>   |

EDGSEQEN: Edge Sequence Enable bit

0 = No edge sequence is needed

1 = Enables edge delay generation 0 = Disables edge delay generation

EDGEN: Edge Enable bit

bit 7-0 Unimplemented: Read as '0'

bit 11

bit 10

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.) 0 = Software is used to trigger edges (manual set of EDGxSTAT)

1 = Edge 1 event must occur before Edge 2 event can occur

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                        | R/W-0                                                                                                                                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

|------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|--|

| ADCTS4     | ADCTS3                                                       | ADCTS2                                                                                                                                                         | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |  |

| bit 15     |                                                              |                                                                                                                                                                |                |                  |                              |                 | bit 8  |  |  |  |  |

| R/W-0      | R/W-0                                                        | R/W-0                                                                                                                                                          | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

| OC4CS      |                                                              | OC2CS                                                                                                                                                          | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |  |

| bit 7      |                                                              |                                                                                                                                                                |                |                  |                              |                 | bit (  |  |  |  |  |

| Legend:    |                                                              |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |

| R = Reada  | ble bit                                                      | W = Writable                                                                                                                                                   | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |  |

| -n = Value | at POR                                                       | '1' = Bit is set                                                                                                                                               |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |

| bit 15     | ADCTS4: Sa                                                   | mple Trigger P                                                                                                                                                 | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |  |

|            | 1 = Generates Trigger when the broadcast command is executed |                                                                                                                                                                |                |                  |                              |                 |        |  |  |  |  |

|            | 0 = Does not                                                 | generate Trigg                                                                                                                                                 | er when the b  | roadcast com     | mand is execute              | ed              |        |  |  |  |  |

| bit 14     |                                                              | mple Trigger P                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |

|            |                                                              | <ul> <li>1 = Generates Trigger when the broadcast command is executed</li> <li>0 = Does not generate Trigger when the broadcast command is executed</li> </ul> |                |                  |                              |                 |        |  |  |  |  |

| bit 13     |                                                              |                                                                                                                                                                |                |                  | mand is execute              | a               |        |  |  |  |  |

| DIE 13     |                                                              | ADCTS2: Sample Trigger PTGO13 for ADC bit<br>1 = Generates Trigger when the broadcast command is executed                                                      |                |                  |                              |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 12     |                                                              | mple Trigger P                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                 | es Trigger wher                                                                                                                                                | the broadcas   | t command is     | executed                     |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 11     | -                                                            | ger/Synchroniz                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 10     | IC3TSS: Trig                                                 | ger/Synchroniz                                                                                                                                                 | ation Source f | for IC3 bit      |                              |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 9      | IC2TSS: Trig                                                 | ger/Synchroniz                                                                                                                                                 | ation Source f | for IC2 bit      |                              |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 8      |                                                              | ger/Synchroniz                                                                                                                                                 |                |                  |                              |                 |        |  |  |  |  |

|            |                                                              |                                                                                                                                                                |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 7      |                                                              | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |

|            |                                                              | es clock pulse v<br>generate clock                                                                                                                             |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |

| bit 6      |                                                              | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |

|            |                                                              | es clock pulse v<br>aenerate clock                                                                                                                             |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |

| bit 5      |                                                              | ck Source for C                                                                                                                                                | -              |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                 | es clock pulse v                                                                                                                                               | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |  |

|            | This register is rea<br>PTGSTRT = 1).                        | -                                                                                                                                                              |                |                  |                              |                 | and    |  |  |  |  |

|            | This register is on                                          | lv used with the                                                                                                                                               | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |  |

|            |                                                              | .,                                                                                                                                                             |                |                  | c.op commune                 | •               |        |  |  |  |  |

## **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

| DC CHARACTE      | RISTICS                       |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |  |

|------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|--|

| Parameter<br>No. | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Conditions            |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |  |

| DC60d            | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |  |

| DC60c            | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |  |

| DC60d            | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |  |

| DC60c            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |  |

| DC60d            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.50            |  |  |  |

| DC60c            | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |  |

| DC60d            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 250                           | 450           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.57            |  |  |  |

| DC60c            | 1000                          | 1200          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |  |

| DC60d            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |

| DC60a            | 45                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 v           |  |  |  |

| DC60c            | 1100                          | 1500          | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |

### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

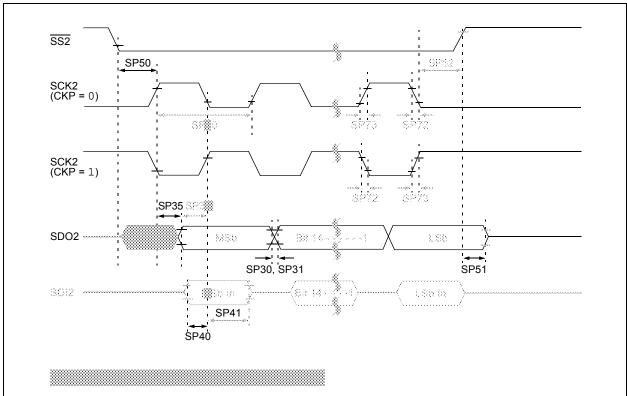

### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CH/                    | DC CHARACTERISTICS   |                                                                        |                              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                              |            |                                            |  |  |  |  |

|---------------------------|----------------------|------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|--------------------------------------------|--|--|--|--|

| Param<br>No.              | Symbol               | Characteristic Min. Typ. <sup>(2)</sup> Max.                           |                              | Max.                                                                                                                                                                                                                 | Units                        | Conditions |                                            |  |  |  |  |

| Op Amp DC Characteristics |                      |                                                                        |                              |                                                                                                                                                                                                                      |                              |            |                                            |  |  |  |  |

| CM40                      | VCMR                 | Common-Mode Input<br>Voltage Range                                     | AVss                         | _                                                                                                                                                                                                                    | AVDD                         | V          |                                            |  |  |  |  |

| CM41                      | CMRR                 | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                          | —                            | 40                                                                                                                                                                                                                   | —                            | db         | VCM = AVDD/2                               |  |  |  |  |

| CM42                      | VOFFSET              | Op Amp Offset<br>Voltage <sup>(3)</sup>                                | —                            | ±5                                                                                                                                                                                                                   | —                            | mV         |                                            |  |  |  |  |

| CM43                      | Vgain                | Open-Loop Voltage<br>Gain <sup>(3)</sup>                               | _                            | 90                                                                                                                                                                                                                   | _                            | db         |                                            |  |  |  |  |

| CM44                      | los                  | Input Offset Current                                                   | _                            | -                                                                                                                                                                                                                    | _                            | _          | See pad leakage currents in Table 30-11    |  |  |  |  |

| CM45                      | lв                   | Input Bias Current                                                     | _                            | _                                                                                                                                                                                                                    | _                            | _          | See pad leakage currents in Table 30-11    |  |  |  |  |

| CM46                      | Ιουτ                 | Output Current                                                         | _                            |                                                                                                                                                                                                                      | 420                          | μA         | With minimum value of RFEEDBACK (CM48)     |  |  |  |  |

| CM48                      | RFEEDBACK            | Feedback Resistance<br>Value                                           | 8                            | -                                                                                                                                                                                                                    | _                            | kΩ         |                                            |  |  |  |  |

| CM49a                     | VOADC                | Output Voltage                                                         | AVss + 0.077                 |                                                                                                                                                                                                                      | AVDD - 0.077                 | V          | Ιουτ = 420 μΑ                              |  |  |  |  |

|                           |                      | Measured at OAx Using ADC <sup>(3,4)</sup>                             | AVss + 0.037<br>AVss + 0.018 |                                                                                                                                                                                                                      | AVDD – 0.037<br>AVDD – 0.018 | V<br>V     | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |  |

| CM49b                     | Vout                 | Output Voltage                                                         | AVss + 0.210                 | _                                                                                                                                                                                                                    | AVDD - 0.210                 | V          | Ιουτ = 420 μΑ                              |  |  |  |  |

|                           |                      | Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                           | AVss + 0.100<br>AVss + 0.050 | _                                                                                                                                                                                                                    | AVDD – 0.100<br>AVDD – 0.050 | V<br>V     | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |  |

| CM51                      | RINT1 <sup>(6)</sup> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup> | 198                          | 264                                                                                                                                                                                                                  | 317                          | Ω          | Min = -40°C<br>Typ = +25°C<br>Max = +125°C |  |  |  |  |

### TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

| AC CHA       | RACTERIS | STICS                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |          |       |                                                 |  |

|--------------|----------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-------|-------------------------------------------------|--|

| Param<br>No. | Symbol   | Characteristic                                   | Min. Typ. Max.                                                                                                                                                                                                                                                                                |           |          | Units | Conditions                                      |  |

|              |          | ADC A                                            | Accuracy                                                                                                                                                                                                                                                                                      | (12-Bit   | Mode)    |       |                                                 |  |

| AD20a        | Nr       | Resolution                                       | 12                                                                                                                                                                                                                                                                                            | 2 Data Bi | its      | bits  |                                                 |  |

| AD21a        | INL      | Integral Nonlinearity                            | -2.5                                                                                                                                                                                                                                                                                          |           | 2.5      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2) |  |

|              |          |                                                  | -5.5                                                                                                                                                                                                                                                                                          | —         | 5.5      | LSb   | +85°C $<$ TA $\leq$ +125°C (Note 2)             |  |

| AD22a        | DNL      | Differential Nonlinearity                        | -1                                                                                                                                                                                                                                                                                            | _         | 1        | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)           |  |

|              |          |                                                  | -1                                                                                                                                                                                                                                                                                            | —         | 1        | LSb   | +85°C < TA $\leq$ +125°C (Note 2)               |  |

| AD23a        | Gerr     | Gain Error <sup>(3)</sup>                        | -10                                                                                                                                                                                                                                                                                           | _         | 10       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)           |  |

|              |          |                                                  | -10                                                                                                                                                                                                                                                                                           | _         | 10       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)               |  |

| AD24a        | EOFF     | Offset Error                                     | -5                                                                                                                                                                                                                                                                                            | —         | 5        | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2) |  |

|              |          |                                                  | -5                                                                                                                                                                                                                                                                                            | —         | 5        | LSb   | +85°C < TA $\leq$ +125°C (Note 2)               |  |

| AD25a        | —        | Monotonicity                                     | —                                                                                                                                                                                                                                                                                             |           |          |       | Guaranteed                                      |  |

|              |          | Dynamic                                          | Performa                                                                                                                                                                                                                                                                                      | ance (12- | -Bit Mod | e)    |                                                 |  |

| AD30a        | THD      | Total Harmonic Distortion <sup>(3)</sup>         | _                                                                                                                                                                                                                                                                                             | 75        |          | dB    |                                                 |  |

| AD31a        | SINAD    | Signal to Noise and<br>Distortion <sup>(3)</sup> | —                                                                                                                                                                                                                                                                                             | 68        |          | dB    |                                                 |  |

| AD32a        | SFDR     | Spurious Free Dynamic<br>Range <sup>(3)</sup>    | —                                                                                                                                                                                                                                                                                             | 80        | —        | dB    |                                                 |  |

| AD33a        | Fnyq     | Input Signal Bandwidth <sup>(3)</sup>            | —                                                                                                                                                                                                                                                                                             | 250       | —        | kHz   |                                                 |  |

| AD34a        | ENOB     | Effective Number of Bits <sup>(3)</sup>          | 11.09                                                                                                                                                                                                                                                                                         | 11.3      |          | bits  |                                                 |  |

### TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)