Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp504-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.4 Special Function Register Maps

# TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00         |                  |        |              |            |        |       | 20/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------------|------------------|--------|--------------|------------|--------|-------|-----------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15       | Bit 14           | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8     | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |              |                  |        |              |            |        |       | W0 (WR    | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |              |                  |        |              |            |        |       | W1        |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |              | W2 xx            |        |              |            |        |       |           |        |       |        |         | xxxx     |          |       |       |               |

| W3        | 0006  |              |                  |        |              |            |        |       | W3        |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |              |                  |        |              |            |        |       | W4        |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |              |                  |        |              |            |        |       | W5        |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |              |                  |        |              |            |        |       | W6        |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |              |                  |        |              |            |        |       | W7        |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |              |                  |        |              |            |        |       | W8        |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |              |                  |        |              |            |        |       | W9        |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |              |                  |        |              |            |        |       | W10       |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |              |                  |        |              |            |        |       | W11       |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |              |                  |        |              |            |        |       | W12       |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |              |                  |        |              |            |        |       | W13       |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |              |                  |        |              |            |        |       | W14       |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |              |                  |        |              |            |        |       | W15       |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |              |                  |        |              |            |        |       | SPLI      | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |              |                  |        |              |            |        |       | ACCA      | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |              |                  |        |              |            |        |       | ACCA      | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |              |                  | Si     | gn Extensior | n of ACCA< | 39>    |       |           |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |              |                  |        |              |            |        |       | ACCB      | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |              |                  |        |              |            |        |       | ACCB      | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |              |                  | Si     | gn Extensior | n of ACCB< | 39>    |       |           |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |              |                  |        |              |            |        | F     | PCL<15:0> |        |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _            | _                | _      | —            | _          | _      | —     | _         | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _            | _                | _      | _            | _          | _      |       |           |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _            |                  | _      | —            |            | _      | _     |           |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |              |                  |        |              |            |        |       | RCOUNT<   | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  | DCOUNT<15:0> |                  |        |              |            |        |       | 0000      |        |       |        |         |          |          |       |       |               |

| DOSTARTL  | 003A  |              |                  |        |              |            |        |       |           | 0000   |       |        |         |          |          |       |       |               |

| DOSTARTH  | 003C  | _            | —                | —      | _            | —          | —      | —     | _         | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |              | DOENDL<15:1> — 0 |        |              |            |        |       |           |        | 0000  |        |         |          |          |       |       |               |

| DOENDH    | 0040  | _            | —                | —      | —            | —          | —      | _     | —         | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |              |                  |        |              |            |        |       |           |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

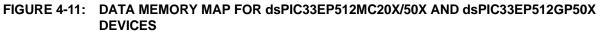

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

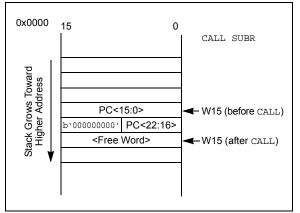

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

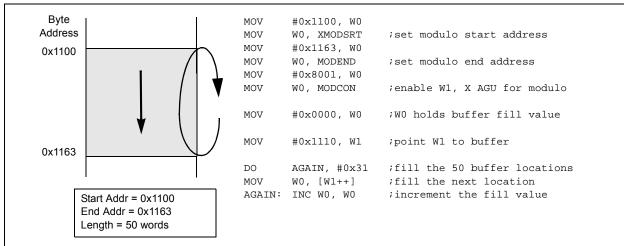

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

# 12.2 Timer1 Control Register

| R/W-0              | U-0                                                                                                                            | R/W-0                                                          | U-0                       | U-0              | U-0                      | U-0                | U-0                |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|--|--|--|--|--|--|

| TON <sup>(1)</sup> | —                                                                                                                              | TSIDL                                                          | —                         | _                | —                        | _                  | _                  |  |  |  |  |  |  |

| bit 15             |                                                                                                                                |                                                                |                           |                  |                          |                    | bit 8              |  |  |  |  |  |  |

|                    |                                                                                                                                |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| U-0                | R/W-0                                                                                                                          | R/W-0                                                          | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |  |  |  |  |  |  |

|                    | TGATE                                                                                                                          | TCKPS1                                                         | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |  |  |  |  |  |  |

| bit 7              |                                                                                                                                |                                                                |                           |                  |                          |                    | bit (              |  |  |  |  |  |  |

| Legend:            |                                                                                                                                |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| R = Readable       | e bit                                                                                                                          | W = Writable                                                   | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |  |  |  |  |  |  |

| -n = Value at      | POR                                                                                                                            | '1' = Bit is set                                               |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |  |  |  |  |  |  |

|                    |                                                                                                                                | o                                                              |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                                                                                           |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | 0 = Stops 16-                                                                                                                  |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 14             | Unimplemen                                                                                                                     | ted: Read as '                                                 | 0'                        |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 13             | TSIDL: Timer                                                                                                                   | 1 Stop in Idle N                                               | /lode bit                 |                  |                          |                    |                    |  |  |  |  |  |  |

|                    |                                                                                                                                | 1 = Discontinues module operation when device enters Idle mode |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    |                                                                                                                                | s module opera                                                 |                           | ode              |                          |                    |                    |  |  |  |  |  |  |

| bit 12-7           | -                                                                                                                              | ted: Read as '                                                 |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 6              |                                                                                                                                | r1 Gated Time                                                  | Accumulation              | h Enable bit     |                          |                    |                    |  |  |  |  |  |  |

|                    | When TCS = 1:<br>This bit is ignored.                                                                                          |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | When TCS = $0$ :                                                                                                               |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | 1 = Gated time accumulation is enabled                                                                                         |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | <ul> <li>0 = Gated time accumulation is disabled</li> <li>TCKPS&lt;1:0&gt;: Timer1 Input Clock Prescale Select bits</li> </ul> |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 5-4            |                                                                                                                                | : Timer'i Input                                                | Clock Prescal             | e Select bits    |                          |                    |                    |  |  |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                                                                                                        |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | 01 = 1:8                                                                                                                       |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | 00 = 1:1                                                                                                                       |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 3              | -                                                                                                                              | ted: Read as '                                                 |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 2              |                                                                                                                                | er1 External Clo                                               | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |  |  |  |  |  |  |

|                    | When TCS =                                                                                                                     |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

|                    |                                                                                                                                | izes external c<br>synchronize e>                              |                           | nut              |                          |                    |                    |  |  |  |  |  |  |

|                    | When TCS =                                                                                                                     | •                                                              |                           | iput             |                          |                    |                    |  |  |  |  |  |  |

|                    | This bit is igno                                                                                                               |                                                                |                           |                  |                          |                    |                    |  |  |  |  |  |  |

| bit 1              | TCS: Timer1                                                                                                                    | Clock Source S                                                 | Select bit <sup>(1)</sup> |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                                                                                              | clock is from pi<br>ock (FP)                                   | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |  |  |  |  |  |  |

| bit 0              | Unimplemen                                                                                                                     | ted: Read as '                                                 | 0'                        |                  |                          |                    |                    |  |  |  |  |  |  |

|                    | nen Timer1 is er<br>empts by user s                                                                                            |                                                                |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |  |  |  |  |  |  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                                            | R/W-0                                                                                                                                                                                                                             | R/W-0            | R/W-0            | R/W-0                              | R/W-0          | R/W-0              | R/W-0 |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------------------------|----------------|--------------------|-------|--|--|

|                                                  | F15B                                                                                                                                                                                                                              | P<3:0>           |                  | F14BP<3:0>                         |                |                    |       |  |  |

| bit 15                                           |                                                                                                                                                                                                                                   |                  |                  |                                    |                |                    | bit 8 |  |  |

| R/W-0                                            | R/W-0                                                                                                                                                                                                                             | R/W-0            | R/W-0            | R/W-0                              | R/W-0          | R/W-0              | R/W-0 |  |  |

| F13BP<3:0>                                       |                                                                                                                                                                                                                                   |                  |                  |                                    | P<3:0>         | 1010 0             |       |  |  |

| bit 7                                            |                                                                                                                                                                                                                                   |                  |                  |                                    |                |                    | bit 0 |  |  |

| Legend:                                          |                                                                                                                                                                                                                                   |                  |                  |                                    |                |                    |       |  |  |

| R = Readabl                                      | e bit                                                                                                                                                                                                                             | W = Writable     | bit              | U = Unimplemented bit, read as '0' |                |                    |       |  |  |

| -n = Value at                                    | t POR                                                                                                                                                                                                                             | '1' = Bit is set |                  | '0' = Bit is cleared               |                | x = Bit is unknown |       |  |  |

| bit 15-12                                        | F15BP<3:0>: RX Buffer Mask for Filter 1<br>1111 = Filter hits received in RX FIFO bu<br>1110 = Filter hits received in RX Buffer 1<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                  |                  | differ<br>4                        |                |                    |       |  |  |

| bit 11-8                                         | pit 11-8 F14BP<3:0>: RX Buffer Mask for Filter 14                                                                                                                                                                                 |                  |                  | 4 bits (same val                   | ues as bits<15 | :12>)              |       |  |  |

| bit 7-4 F13BP<3:0>: RX Buffer Mask for Filter 13 |                                                                                                                                                                                                                                   |                  | 3 bits (same val | ues as bits<15                     | :12>)          |                    |       |  |  |

| bit 3-0                                          | F12BP<3:0:                                                                                                                                                                                                                        | RX Buffer Ma     | sk for Filter 1  | 2 bits (same val                   | ues as bits<15 | :12>)              |       |  |  |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| R/W-0                                                                                                     | R/W-0                                                                         | R/W-0                                                                                                    | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|--|--|--|

| EDG1MOD                                                                                                   | EDG1POL                                                                       | EDG1SEL3                                                                                                 | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |  |

| bit 15                                                                                                    |                                                                               | 1                                                                                                        |                  | 11                 |                 |                 | bit 8    |  |  |  |  |  |

|                                                                                                           |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| R/W-0                                                                                                     | R/W-0                                                                         | R/W-0                                                                                                    | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |  |  |  |

| EDG2MOD                                                                                                   | EDG2POL                                                                       | EDG2SEL3                                                                                                 | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | _               | _        |  |  |  |  |  |

| bit 7                                                                                                     |                                                                               |                                                                                                          |                  | 1 1                |                 |                 | bit C    |  |  |  |  |  |

|                                                                                                           |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| Legend:                                                                                                   |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| R = Readabl                                                                                               | le bit                                                                        | W = Writable                                                                                             | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |  |  |  |

| -n = Value at                                                                                             | POR                                                                           | '1' = Bit is set                                                                                         |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |  |  |  |

|                                                                                                           |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 15                                                                                                    | EDG1MOD: E                                                                    | Edge 1 Edge Sa                                                                                           | ampling Mode     | Selection bit      |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 1 = Edge 1 is                                                                 | s edge-sensitive                                                                                         | 9                |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | •                                                                             | s level-sensitive                                                                                        |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 14                                                                                                    |                                                                               | dge 1 Polarity                                                                                           |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           |                                                                               | L = Edge 1 is programmed for a positive edge response                                                    |                  |                    |                 |                 |          |  |  |  |  |  |

| L:1 40 40                                                                                                 | •                                                                             | 0 = Edge 1 is programmed for a negative edge response                                                    |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 13-10 EDG1SEL<3:0>: Edge 1 Source Select bits                                                         |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 1xxx = Reserved<br>01xx = Reserved                                            |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0011 = CTED1 pin                                                              |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0010 = CTED2 pin                                                              |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0001 = OC1 module<br>0000 = Timer1 module                                     |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| hit 0                                                                                                     |                                                                               |                                                                                                          | :+               |                    |                 |                 |          |  |  |  |  |  |

| bit 9                                                                                                     |                                                                               | Edge 2 Status b                                                                                          |                  | writton to control | the edge cou    | ree             |          |  |  |  |  |  |

|                                                                                                           |                                                                               | Indicates the status of Edge 2 and can be written to control the edge source.<br>1 = Edge 2 has occurred |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0 = Edge 2 has not occurred                                                   |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 8                                                                                                     | EDG1STAT: E                                                                   | DG1STAT: Edge 1 Status bit                                                                               |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | Indicates the status of Edge 1 and can be written to control the edge source. |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 1 = Edge 1 has occurred<br>0 = Edge 1 has not occurred                        |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | -                                                                             |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 7                                                                                                     |                                                                               | Edge 2 Edge Sa                                                                                           |                  | Selection bit      |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 1 = Edge 2 is edge-sensitive<br>0 = Edge 2 is level-sensitive                 |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 6                                                                                                     | •                                                                             |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 6 <b>EDG2POL:</b> Edge 2 Polarity Select bit<br>1 = Edge 2 is programmed for a positive edge response |                                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           |                                                                               | s programmed f                                                                                           |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 5-2                                                                                                   | EDG2SEL<3                                                                     | :0>: Edge 2 So                                                                                           | urce Select bits | 3                  |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 1111 = Reserved                                                               |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           |                                                                               | 01xx = Reserved                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                        |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0010 = CTEE                                                                   |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0001 = OC1 module                                                             |                                                                                                          |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           | 0001 = OC1                                                                    | module                                                                                                   |                  |                    |                 |                 |          |  |  |  |  |  |

|                                                                                                           |                                                                               | module                                                                                                   |                  |                    |                 |                 |          |  |  |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

NOTES:

| Base<br>Instr<br># | str Mnemonic |       | Assembly Syntax                     | Description                                            | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|--------------|-------|-------------------------------------|--------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD          | ADD   | Acc <sup>(1)</sup>                  | Add Accumulators                                       | 1             | 1                             | OA,OB,SA,SB              |

|                    |              | ADD   | f                                   | f = f + WREG                                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADD   | f,WREG                              | WREG = f + WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADD   | #lit10,Wn                           | Wd = lit10 + Wd                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADD   | Wb,Ws,Wd                            | Wd = Wb + Ws                                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADD   | Wb,#lit5,Wd                         | Wd = Wb + lit5                                         | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADD   | Wso,#Slit4,Acc                      | 16-bit Signed Add to Accumulator                       | 1             | 1                             | OA,OB,SA,SE              |

| 2                  | ADDC         | ADDC  | f                                   | f = f + WREG + (C)                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADDC  | f,WREG                              | WREG = $f + WREG + (C)$                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADDC  | #lit10,Wn                           | Wd = lit10 + Wd + (C)                                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADDC  | Wb,Ws,Wd                            | Wd = Wb + Ws + (C)                                     | 1             | 1                             | C,DC,N,OV,Z              |

|                    |              | ADDC  | Wb,#lit5,Wd                         | Wd = Wb + lit5 + (C)                                   | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND          | AND   | f                                   | f = f .AND. WREG                                       | 1             | 1                             | N,Z                      |

|                    |              | AND   | f,WREG                              | WREG = f .AND. WREG                                    | 1             | 1                             | N,Z                      |

|                    |              | AND   | #lit10,Wn                           | Wd = lit10 .AND. Wd                                    | 1             | 1                             | N,Z                      |

|                    |              | AND   | Wb,Ws,Wd                            | Wd = Wb .AND. Ws                                       | 1             | 1                             | N,Z                      |

|                    |              | AND   | Wb,#lit5,Wd                         | Wd = Wb .AND. lit5                                     | 1             | 1                             | N,Z                      |

| 4                  | ASR          | ASR   | f                                   | f = Arithmetic Right Shift f                           | 1             | 1                             | C,N,OV,Z                 |

|                    |              | ASR   | f,WREG                              | WREG = Arithmetic Right Shift f                        | 1             | 1                             | C,N,OV,Z                 |

|                    |              | ASR   | Ws,Wd                               | Wd = Arithmetic Right Shift Ws                         | 1             | 1                             | C,N,OV,Z                 |

|                    |              | ASR   | Wb,Wns,Wnd                          | Wnd = Arithmetic Right Shift Wb by Wns                 | 1             | 1                             | N,Z                      |

|                    |              | ASR   | Wb,#lit5,Wnd                        | Wnd = Arithmetic Right Shift Wb by lit5                | 1             | 1                             | N,Z                      |