#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp504t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

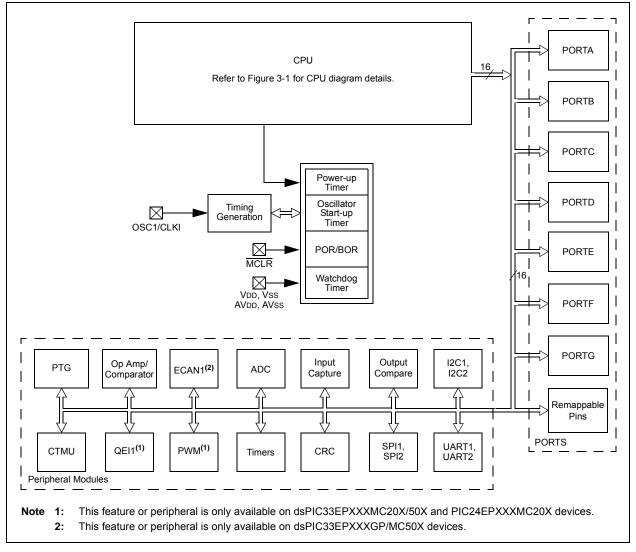

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

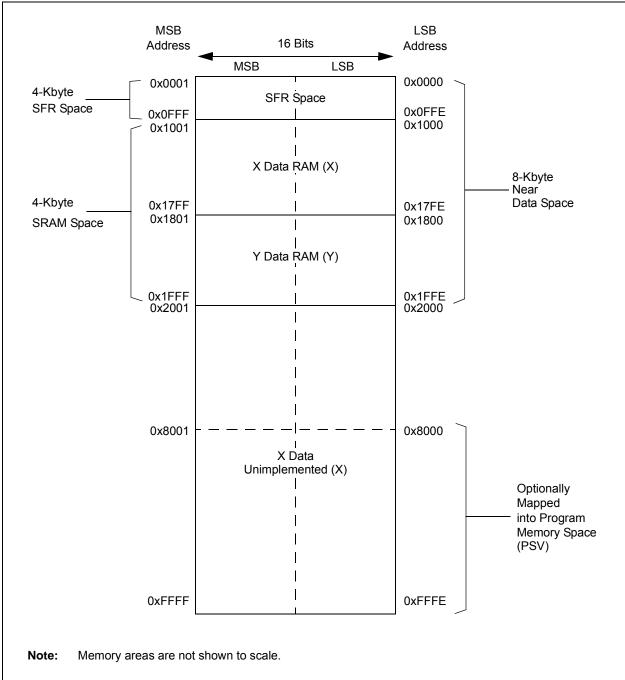

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10               | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|----------------------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |                      | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT                   | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F                    | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |                      | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |                      |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |                      |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -                    | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<3:0> VECNUM<7:0> |            |       |       | 0000    |             |         |         |        |             |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

| U-0                               | U-0                                                                                                                         | U-0                     | U-0                                | U-0              | U-0  | U-0                | U-0   |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------|------------------|------|--------------------|-------|--|--|--|

| -                                 | —                                                                                                                           | —                       | —                                  | —                | —    | —                  | —     |  |  |  |

| bit 15                            |                                                                                                                             |                         |                                    |                  |      |                    | bit 8 |  |  |  |

| U-0                               | U-0                                                                                                                         | U-0                     | U-0                                | R-1              | R-1  | R-1                | R-1   |  |  |  |

| _                                 | _                                                                                                                           | _                       | _                                  |                  | LSTC | H<3:0>             |       |  |  |  |

| bit 7                             |                                                                                                                             |                         |                                    |                  |      |                    | bit 0 |  |  |  |

| Legend:                           |                                                                                                                             |                         |                                    |                  |      |                    |       |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                             | bit                     | U = Unimplemented bit, read as '0' |                  |      |                    |       |  |  |  |

| -n = Value a                      | at POR                                                                                                                      | '1' = Bit is set        |                                    | '0' = Bit is cle | ared | x = Bit is unknown |       |  |  |  |

|                                   |                                                                                                                             |                         |                                    |                  |      |                    |       |  |  |  |

| bit 15-4                          | Unimplemen                                                                                                                  | ted: Read as '          | 0'                                 |                  |      |                    |       |  |  |  |

| bit 3-0                           | LSTCH<3:0>                                                                                                                  | : Last DMAC C           | hannel Active                      | e Status bits    |      |                    |       |  |  |  |

|                                   | 1111 = No DI<br>1110 = Rese                                                                                                 | MA transfer has<br>rved | s occurred sir                     | nce system Res   | set  |                    |       |  |  |  |

|                                   | •                                                                                                                           |                         |                                    |                  |      |                    |       |  |  |  |

|                                   | •                                                                                                                           |                         |                                    |                  |      |                    |       |  |  |  |

|                                   | •                                                                                                                           |                         |                                    |                  |      |                    |       |  |  |  |

|                                   | 0100 = Reserved<br>0011 = Last data transfer was handled by Channel 3<br>0010 = Last data transfer was handled by Channel 2 |                         |                                    |                  |      |                    |       |  |  |  |

|                                   | 0001 = Last data transfer was handled by Channel 1                                                                          |                         |                                    |                  |      |                    |       |  |  |  |

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0                                                                                             | R-0                                        | R-0                                                                                                       | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|

| _                                                                                               | COSC2                                      | COSC1                                                                                                     | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |

| bit 15                                                                                          |                                            |                                                                                                           |                                    |                                    |                                    |                      | bit 8                |  |  |  |

| R/W-0                                                                                           | R/W-0                                      | R-0                                                                                                       | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |

| CLKLOC                                                                                          | CK IOLOCK                                  | LOCK                                                                                                      |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |

| bit 7                                                                                           |                                            |                                                                                                           |                                    |                                    |                                    |                      | bit (                |  |  |  |

| Legend:                                                                                         |                                            | y = Value set                                                                                             | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |

| R = Reada                                                                                       | able bit                                   | W = Writable                                                                                              | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared                                         |                                            |                                                                                                           |                                    |                                    |                                    | x = Bit is unkr      | nown                 |  |  |  |

| hit 1 <i>5</i>                                                                                  | Unimplemen                                 | ted. Dood oo                                                                                              | 0'                                 |                                    |                                    |                      |                      |  |  |  |

| bit 15                                                                                          | -                                          | ted: Read as                                                                                              |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 14-12                                                                                       |                                            | Current Oscill                                                                                            |                                    |                                    | ()                                 |                      |                      |  |  |  |

|                                                                                                 |                                            | C Oscillator (F<br>C Oscillator (F                                                                        |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | ower RC Oscil                                                                                             |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | 00 = Reserved                                                                                             |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                            |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | y Oscillator (X                                                                                           |                                    |                                    |                                    |                      |                      |  |  |  |

| 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCF<br>000 = Fast RC Oscillator (FRC) |                                            |                                                                                                           |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 11                                                                                          |                                            | Unimplemented: Read as '0'                                                                                |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 10-8                                                                                        | NOSC<2:0>:                                 | New Oscillato                                                                                             | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |  |  |  |

|                                                                                                 | 111 = Fast R                               | C Oscillator (F                                                                                           | RC) with Divid                     | le-by-n                            |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | C Oscillator (F                                                                                           |                                    | le-by-16                           |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | ower RC Oscil                                                                                             | ator (LPRC)                        |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 | 100 = Reserv                               | /ed<br>y Oscillator (X                                                                                    |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            |                                                                                                           |                                    | IFLL                               |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | 010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | 000 = Fast RC Oscillator (FRC)                                                                            |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 7                                                                                           |                                            | Clock Lock Ena                                                                                            |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            |                                                                                                           |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |

|                                                                                                 |                                            | figurations may<br>d PLL selectio                                                                         |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |

| bit 6                                                                                           |                                            | Lock Enable b                                                                                             |                                    | -                                  | -                                  |                      |                      |  |  |  |

|                                                                                                 | 1 = I/O lock is                            | s active                                                                                                  |                                    |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 | 0 = I/O lock is                            | s not active                                                                                              |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 5                                                                                           | LOCK: PLL L                                | ock Status bit                                                                                            | (read-only)                        |                                    |                                    |                      |                      |  |  |  |

|                                                                                                 |                                            | s that PLL is in<br>s that PLL is ou                                                                      |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |

| Note 1:                                                                                         | Writes to this regis                       |                                                                                                           |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |

| 2:                                                                                              | Direct clock switch<br>This applies to clo | es between ar<br>ck switches in                                                                           | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |

| 0                                                                                               |                                            | le as a transitional clock source between the two PLL modes.                                              |                                    |                                    |                                    |                      |                      |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

# 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                        | R/W-0                                  | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |  |  |

|---------------|--------------------------------------------|----------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|--|--|

|               | 0-0                                        | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |  |  |

| <br>bit 15    |                                            | COOIDE                                 |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |  |  |

| Sit 10        |                                            |                                        |                   |                   |                        |                  | bit 0         |  |  |

| R/W-0         | U-0                                        | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |  |  |

| ENFLT         |                                            | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |  |  |

| bit 7         |                                            |                                        |                   |                   |                        |                  | bit 0         |  |  |

|               |                                            |                                        |                   |                   |                        |                  |               |  |  |

| Legend:       | end: HSC = Hardware Settable/Clearable bit |                                        |                   |                   |                        |                  |               |  |  |

| R = Read      | able bit                                   | W = Writable I                         | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |  |  |

| -n = Value    | e at POR                                   | '1' = Bit is set                       |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |  |  |

|               |                                            |                                        |                   |                   |                        |                  |               |  |  |

| bit 15-14     | Unimplemen                                 | ted: Read as '0                        | )'                |                   |                        |                  |               |  |  |

| bit 13        | OCSIDL: Out                                | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                        |                  |               |  |  |

|               |                                            | ompare x Halts                         |                   |                   |                        |                  |               |  |  |

|               | •                                          | compare x conti                        | •                 |                   | ode                    |                  |               |  |  |

| bit 12-10     |                                            | )>: Output Com                         | pare x Clock S    | elect bits        |                        |                  |               |  |  |

|               | 111 = Periph<br>110 = Reserv               | eral clock (FP)                        |                   |                   |                        |                  |               |  |  |

|               | 101 = PTGO                                 |                                        |                   |                   |                        |                  |               |  |  |

|               |                                            | is the clock so                        |                   |                   | hronous clock          | is supported)    |               |  |  |

|               |                                            | is the clock so                        |                   |                   |                        |                  |               |  |  |

|               |                                            | ( is the clock so<br>( is the clock so |                   |                   |                        |                  |               |  |  |

|               |                                            | is the clock so                        |                   |                   |                        |                  |               |  |  |

| bit 9         | Unimplemen                                 | ted: Read as '0                        | )'                |                   |                        |                  |               |  |  |

| bit 8         | ENFLTB: Fau                                | ult B Input Enab                       | le bit            |                   |                        |                  |               |  |  |

|               |                                            | compare Fault B<br>compare Fault B     |                   |                   |                        |                  |               |  |  |

| bit 7         | -                                          | ult A Input Enab                       |                   |                   |                        |                  |               |  |  |

|               | 1 = Output C                               | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                        |                  |               |  |  |

| bit 6         | •                                          | ted: Read as '0                        | • • •             |                   |                        |                  |               |  |  |

| bit 5         | OCFLTB: PW                                 | M Fault B Con                          | dition Status bit |                   |                        |                  |               |  |  |

|               |                                            | ult B condition of Fault B condition   |                   |                   |                        |                  |               |  |  |

| bit 4         |                                            | /M Fault A Cond                        | •                 |                   |                        |                  |               |  |  |

|               |                                            | ult A condition o                      |                   |                   |                        |                  |               |  |  |

| Note 1:       | OCxR and OCxF                              | 29 are double h                        | uffered in D\\//  | / mode only       |                        |                  |               |  |  |

| Note 1.<br>2: | Each Output Cor                            |                                        |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |  |  |

| 2.            | Generator (PTG                             |                                        |                   |                   |                        | 5.1 2 7.0 1 611p |               |  |  |

|               | PTGO4 = OC1                                | -                                      |                   |                   |                        |                  |               |  |  |

|               | PTGO5 = OC2                                |                                        |                   |                   |                        |                  |               |  |  |

|               | PTGO6 = OC3<br>PTGO7 = OC4                 |                                        |                   |                   |                        |                  |               |  |  |

|               |                                            |                                        |                   |                   |                        |                  |               |  |  |

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 ELTROL Fault Delarity for DWM Concrete

# bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- **2:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |  |  |  |  |  |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |  |  |  |  |  |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |  |  |  |  |  |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |  |  |  |  |  |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |  |  |  |  |  |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |  |  |  |  |  |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | - 1                                |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filte<br>00000 = Filte       |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000101-1111111 = Reserved           |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | 0001111 = RB15 buffer interrupt      |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-20: | CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER |

|-----------------|---------------------------------------------------------------|

|                 | REGISTER (n = 0-2)                                            |

|                  |               | -                                        | -             |                                                 |       |       |       |  |  |

|------------------|---------------|------------------------------------------|---------------|-------------------------------------------------|-------|-------|-------|--|--|

| R/W-x            | R/W-x         | R/W-x                                    | R/W-x         | R/W-x                                           | R/W-x | R/W-x | R/W-x |  |  |

| SID10            | SID9          | SID8                                     | SID7          | SID6                                            | SID5  | SID4  | SID3  |  |  |

| bit 15           |               |                                          |               |                                                 |       |       | bit 8 |  |  |

| R/W-x            | R/W-x         | R/W-x                                    | U-0           | R/W-x                                           | U-0   | R/W-x | R/W-x |  |  |

| SID2             | SID1          | SID0                                     | -             | MIDE                                            | _     | EID17 | EID16 |  |  |

| bit 7            |               |                                          |               |                                                 |       |       | bit C |  |  |

| <u> </u>         |               |                                          |               |                                                 |       |       |       |  |  |

| Legend:          |               |                                          |               |                                                 |       |       |       |  |  |

| R = Readable bit |               | W = Writable                             | bit           | U = Unimplemented bit, read as '0'              |       |       |       |  |  |

| -n = Value a     | at POR        | '1' = Bit is set                         | :             | '0' = Bit is cleared x = Bit is unknown         |       |       |       |  |  |

| bit 15-5         | SID<10:0>: S  | Standard Identi                          | fier bits     |                                                 |       |       |       |  |  |

|                  |               | bit, SIDx, in filte<br>is a don't care i |               |                                                 |       |       |       |  |  |

| bit 4            | Unimplemer    | nted: Read as '                          | 0'            |                                                 |       |       |       |  |  |

| bit 3            | MIDE: Identif | fier Receive Mo                          | de bit        |                                                 |       |       |       |  |  |

|                  | 0 = Matches   |                                          | or extended a | d or extended ac<br>address messag<br>SID/EID)) |       | •     |       |  |  |

| bit 2            | Unimplemer    | nted: Read as '                          | 0'            |                                                 |       |       |       |  |  |

| bit 1-0          | EID<17:16>:   | Extended Iden                            | tifier bits   |                                                 |       |       |       |  |  |

|                  |               | bit, EIDx, in fill<br>is a don't care    |               |                                                 |       |       |       |  |  |

|                  |               |                                          |               |                                                 |       |       |       |  |  |

#### REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x                             | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|-----------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

| EID15                             | EID14 | EID13 | EID12 | EID11                              | EID10 | EID9  | EID8  |  |

| bit 15                            |       |       |       | ·                                  |       |       | bit 8 |  |

|                                   |       |       |       |                                    |       |       |       |  |

| R/W-x                             | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

| EID7                              | EID6  | EID5  | EID4  | EID3                               | EID2  | EID1  | EID0  |  |

| bit 7                             |       |       |       |                                    |       | •     | bit 0 |  |

|                                   |       |       |       |                                    |       |       |       |  |

| Legend:                           |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

## TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| DC CHARACTERISTICS                 |      | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$            |      |      |      |       |                 |  |

|------------------------------------|------|---------------------------------------------------------------------|------|------|------|-------|-----------------|--|

| Param<br>No. Symbol Characteristic |      |                                                                     | Min. | Тур. | Max. | Units | Conditions      |  |

| Operating Voltage                  |      |                                                                     |      |      |      |       |                 |  |

| DC10                               | Vdd  | Supply Voltage                                                      | 3.0  |      | 3.6  | V     |                 |  |

| DC16                               | VPOR | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | -    | _    | Vss  | V     |                 |  |

| DC17                               | Svdd | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03 | _    | —    | V/ms  | 0V-1V in 100 ms |  |

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated):Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                   |     |    |  |    |                                                       |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|----|--|----|-------------------------------------------------------|--|

| Param<br>No. | Symbol Characteristics Min Typ Max Units Comments                                                                                                                                        |                                                   |     |    |  |    |                                                       |  |

|              | Cefc                                                                                                                                                                                     | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7 | 10 |  | μF | Capacitor must have a low series resistance (< 1 Ohm) |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD  $\geq$  VDDMIN.

| DC CHARACTERISTICS |        |                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |         |    |                        |  |  |  |

|--------------------|--------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----|------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic                                          | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                       |     |         |    |                        |  |  |  |

|                    | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                       |     |         |    |                        |  |  |  |

| DI10               |        | Any I/O Pin and MCLR                                    | Vss                                                                                                                                                                                                                                                                                   | —   | 0.2 VDD | V  |                        |  |  |  |

| DI18               |        | I/O Pins with SDAx, SCLx                                | Vss                                                                                                                                                                                                                                                                                   | —   | 0.3 VDD | V  | SMBus disabled         |  |  |  |

| DI19               |        | I/O Pins with SDAx, SCLx                                | Vss                                                                                                                                                                                                                                                                                   | —   | 0.8     | V  | SMBus enabled          |  |  |  |

|                    | VIH    | Input High Voltage                                      |                                                                                                                                                                                                                                                                                       |     |         |    |                        |  |  |  |

| DI20               |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD                                                                                                                                                                                                                                                                               | —   | Vdd     | V  | (Note 3)               |  |  |  |

|                    |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD                                                                                                                                                                                                                                                                               | —   | 5.5     | V  | (Note 3)               |  |  |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD                                                                                                                                                                                                                                                                               | —   | 5.5     | V  | SMBus disabled         |  |  |  |

|                    |        | I/O Pins with SDAx, SCLx                                | 2.1                                                                                                                                                                                                                                                                                   | _   | 5.5     | V  | SMBus enabled          |  |  |  |