Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

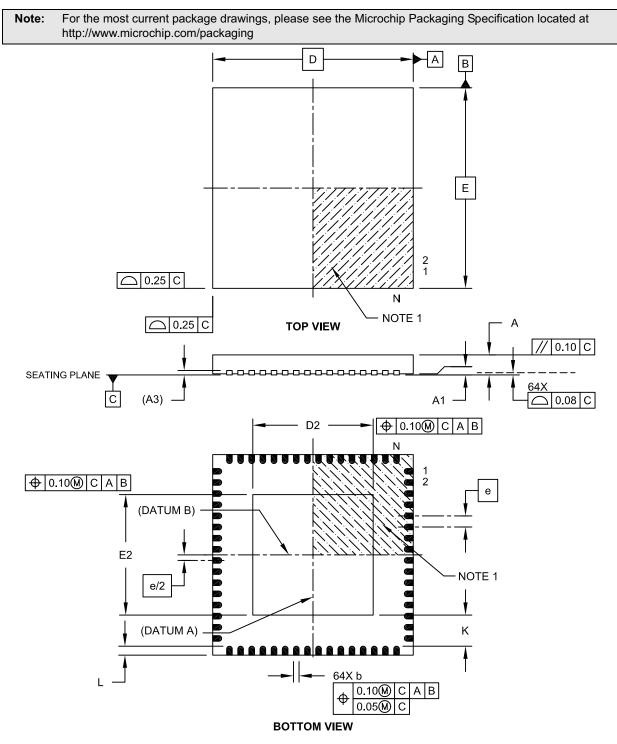

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp504t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

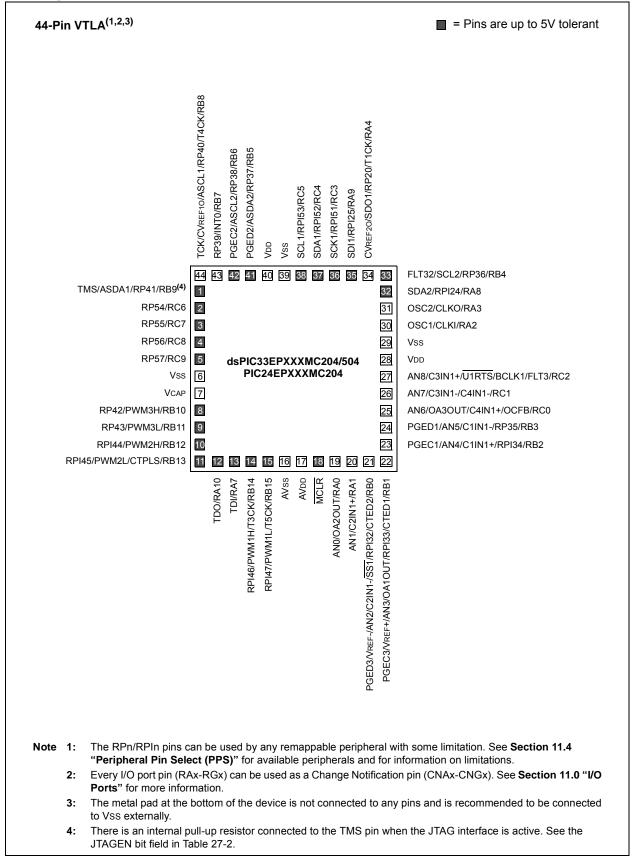

## Pin Diagrams (Continued)

| ABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |  |

|-----------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name <sup>(4)</sup>                       | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |  |

| U2CTS                                         | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |  |

| U2RTS                                         | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |  |

| U2RX                                          | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |  |

| U2TX                                          | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |  |

| BCLK2                                         | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |  |

| SCK1                                          | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |  |

| SDI1                                          | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |  |

| SDO1                                          | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |  |

| SS1                                           | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |

| SCK2                                          | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |  |

| SDI2                                          | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |  |

| SDO2                                          | 0           | _              | Yes | SPI2 data out.                                                                   |  |  |  |  |  |

| SS2                                           | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |

| SCL1                                          | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |  |

| SDA1                                          | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |  |

| ASCL1                                         | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |  |

| ASDA1                                         | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |  |

| SCL2                                          | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |  |

| SDA2                                          | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |  |

| ASCL2                                         | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |  |

| ASDA2                                         | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |  |

| TMS <sup>(5)</sup>                            | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |  |

| TCK                                           | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |  |

| TDI                                           | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |  |

| TDO                                           | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |  |

| C1RX <sup>(2)</sup>                           | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |  |

| C1TX <sup>(2)</sup>                           | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>     | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>     | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                        | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                  | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                    | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                    | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                         | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                         | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |  |

| INDX1 <sup>(1)</sup>                          | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |  |

| HOME1 <sup>(1)</sup>                          | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |  |

| QEA1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |

| QEB1 <sup>(1)</sup>                           | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |  |

|                                               | Ι           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                        | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |  |

|                                               | 0           |                | 162 |                                                                                  |  |  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | _        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       | -             |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                                                                                                                              |          |         |          |          |          |        |               |        |         |          |         |         |      |

|-----------|-------|---------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------|----------|----------|--------|---------------|--------|---------|----------|---------|---------|------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | I3         Bit 12         Bit 11         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |          |         |          |          |          |        | All<br>Resets |        |         |          |         |         |      |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                                                                                                                       | CLIEN    | TRGIEN  | ITB      | MDCS     | DTC<     | :1:0>  | DTCP          | _      | MTBS    | CAM      | XPRES   | IUE     | 0000 |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL                                                                                                                                                                         | PMOD     | <1:0>   | OVRENH   | OVRENL   | OVRDA    | T<1:0> | FLTDA         | T<1:0> | CLDA    | T<1:0>   | SWAP    | OSYNC   | C000 |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> 00                                                                                                                     |          |         |          |          |          |        |               |        | 0000    |          |         |         |      |

| PDC1      | 0C26  |         |        |         | PDC1<15:0> FFF                                                                                                                                                               |          |         |          |          |          |        |               | FFF8   |         |          |         |         |      |

| PHASE1    | 0C28  |         |        |         | PHASE1<15:0> 0                                                                                                                                                               |          |         |          |          |          |        |               | 0000   |         |          |         |         |      |

| DTR1      | 0C2A  | _       | _      |         |                                                                                                                                                                              |          |         |          |          | DTR1<13: | 0>     |               |        |         |          |         |         | 0000 |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                                                                                                                              |          |         |          | А        | LTDTR1<1 | 3:0>   |               |        |         |          |         |         | 0000 |

| TRIG1     | 0C32  |         |        |         |                                                                                                                                                                              |          |         |          | TRGCMP<1 | 5:0>     |        |               |        |         |          |         |         | 0000 |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                                                                                                                              | _        | _       | _        | _        | _        | _      |               |        | TRG     | STRT<5:0 | >       |         | 0000 |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF                                                                                                                                                                          | FLTLEBEN | CLLEBEN | _        | _        | _        | _      | BCH           | BCL    | BPHH    | BPHL     | BPLH    | BPLL    | 0000 |

| LEBDLY1   | 0C3C  | _       | _      | —       | —                                                                                                                                                                            |          |         |          |          |          | LEB<11 | :0>           |        |         |          |         |         | 0000 |

| AUXCON1   | 0C3E  | —       | —      | —       |                                                                                                                                                                              |          | BLANKS  | SEL<3:0> |          | _        | _      |               | CHOPS  | EL<3:0> |          | CHOPHEN | CHOPLEN | 0000 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER                           | TU-5: PIVID6 | . PERIPHER       |                           | DISABLE C    | UNIROL RE             | GISIER 6              |                       |

|------------------------------------|--------------|------------------|---------------------------|--------------|-----------------------|-----------------------|-----------------------|

| U-0                                | U-0          | U-0              | U-0                       | U-0          | R/W-0                 | R/W-0                 | R/W-0                 |

| —                                  | —            | —                | —                         | —            | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15                             |              |                  |                           |              |                       |                       | bit 8                 |

|                                    |              |                  |                           |              |                       |                       |                       |

| U-0                                | U-0          | U-0              | U-0                       | U-0          | U-0                   | U-0                   | U-0                   |

|                                    |              |                  |                           |              |                       |                       |                       |

| bit 7                              |              |                  |                           |              |                       |                       | bit 0                 |

|                                    |              |                  |                           |              |                       |                       |                       |

| Legend:                            |              |                  |                           |              |                       |                       |                       |

| R = Readab                         | le bit       | W = Writable     | bit                       | U = Unimplen | nented bit, read      | l as '0'              |                       |

| -n = Value at POR '1' = Bit is set |              |                  | '0' = Bit is clea         | ared         | x = Bit is unkr       | iown                  |                       |

|                                    |              |                  |                           |              |                       |                       |                       |

| bit 15-11                          | Unimplement  | ted: Read as '   | כ'                        |              |                       |                       |                       |

| bit 10                             | PWM3MD: P\   | NM3 Module D     | isable bit <sup>(1)</sup> |              |                       |                       |                       |

|                                    | 1 = PWM3 mo  | odule is disable | ed                        |              |                       |                       |                       |

|                                    | 0 = PWM3 mo  | odule is enable  | d                         |              |                       |                       |                       |

| bit 9                              | PWM2MD: P\   | NM2 Module D     | isable bit <sup>(1)</sup> |              |                       |                       |                       |

|                                    | 1 = PWM2 mo  | odule is disable | ed                        |              |                       |                       |                       |

|                                    | 0 = PWM2 mo  | odule is enable  | d                         |              |                       |                       |                       |

| bit 8                              | PWM1MD: P\   | NM1 Module D     | isable bit <sup>(1)</sup> |              |                       |                       |                       |

|                                    |              | odule is disable |                           |              |                       |                       |                       |

|                                    | 0 = PWM1 mo  | odule is enable  | d                         |              |                       |                       |                       |

| bit 7-0                            | Unimplement  | ted: Read as '   | כ'                        |              |                       |                       |                       |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0          | U-0                 | U-0                                | U-0   | U-0              | U-0              | U-0             | U-0   |

|--------------|---------------------|------------------------------------|-------|------------------|------------------|-----------------|-------|

| —            | —                   | —                                  | _     | —                | —                | —               | _     |

| bit 15       |                     |                                    |       |                  |                  |                 | bit 8 |

|              |                     |                                    |       |                  |                  |                 |       |

| U-0          | R/W-0               | R/W-0                              | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —            |                     |                                    |       | INT2R<6:0>       |                  |                 |       |

| bit 7        |                     |                                    |       |                  |                  |                 | bit 0 |

|              |                     |                                    |       |                  |                  |                 |       |

| Legend:      |                     |                                    |       |                  |                  |                 |       |

| R = Readal   | ole bit             | W = Writable                       | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | at POR              | '1' = Bit is set                   |       | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |

|              |                     |                                    |       |                  |                  |                 |       |

| bit 15-7     | Unimplemen          | ted: Read as 'd                    | )'    |                  |                  |                 |       |

| bit 6-0      |                     | Assign Externa<br>-2 for input pin |       |                  | orresponding RI  | Pn Pin bits     |       |

|              | 1111001 <b>= lr</b> | put tied to RPI                    | 121   |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              | 0000001 – Ir        | put tied to CMI                    | ⊃1    |                  |                  |                 |       |

|              |                     | put tied to Civil                  |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

|              |                     |                                    |       |                  |                  |                 |       |

## REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

## REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                                         |                  |                 |       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|-----------------------------------------|------------------|-----------------|-------|--|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0                                     | U-0              | U-0             | U-0   |  |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                                       | —                | —               | —     |  |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                                         |                  |                 | bit 8 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |  |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0           | R/W-0 |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —            |                     |                  |       | T2CKR<6:0>                              | >                |                 |       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                                         |                  |                 | bit 0 |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                                         |                  |                 |       |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                                         |                  |                 |       |  |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler                            | mented bit, read | as '0'          |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |                 |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                                         |                  |                 |       |  |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                                         |                  |                 |       |  |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     | •                |       | · · ·                                   | he Correspondir  | ng RPn pin bits | 5     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       | ,                                       |                  |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                                         |                  |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                                         |                  |                 |       |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                                         |                  |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                                         |                  |                 |       |  |  |

NOTES:

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|--|

|                                   |       |                  | TRGC  | MP<15:8>                           |       |                 |       |  |  |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|                                   |       |                  | TRGC  | MP<7:0>                            |       |                 |       |  |  |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |  |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |  |  |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

## 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

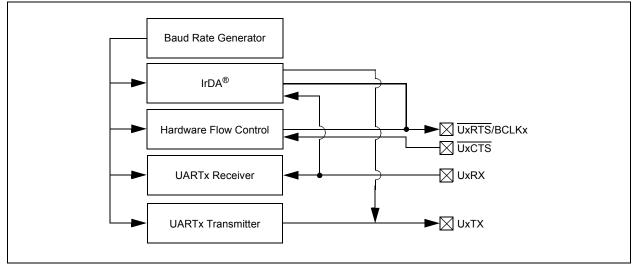

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.