Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Betans                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

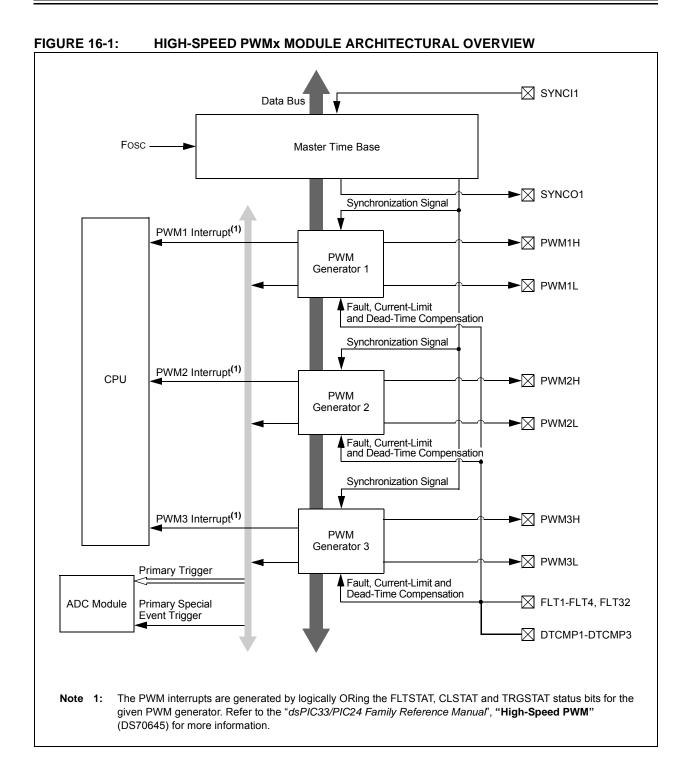

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | •                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gp504t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

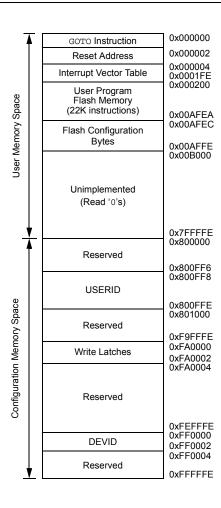

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

## TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | —      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | —      |        | _      | —      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

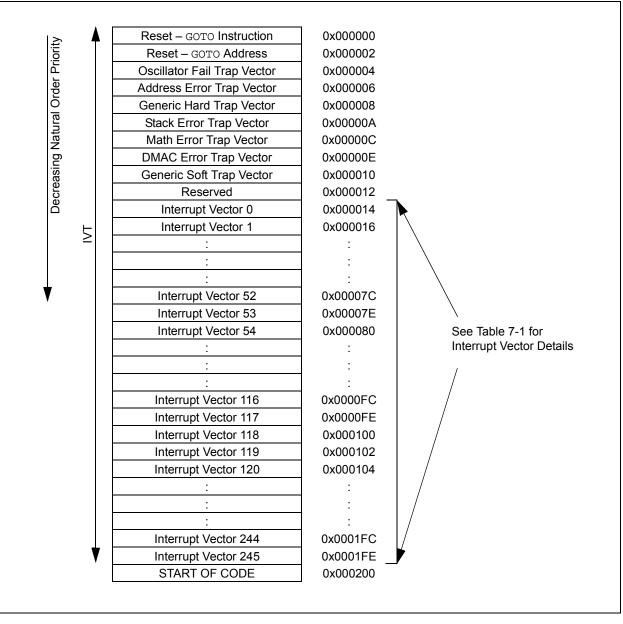

### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

| R/W-1        | R/W-0                                                                                                                            | R/W-0                                                                | U-0           | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|--|--|--|--|

| GIE          | DISI                                                                                                                             | SWTRAP                                                               |               |                  |                  | _               |        |  |  |  |  |  |  |

| bit 15       |                                                                                                                                  |                                                                      |               |                  |                  |                 | bit 8  |  |  |  |  |  |  |

|              |                                                                                                                                  |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

| U-0          | U-0                                                                                                                              | U-0                                                                  | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |

|              | —                                                                                                                                |                                                                      |               |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |  |

| bit 7        |                                                                                                                                  |                                                                      |               |                  |                  |                 | bit C  |  |  |  |  |  |  |

| Legend:      |                                                                                                                                  |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                           | W = Writable                                                         | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |  |  |

| -n = Value a |                                                                                                                                  | '1' = Bit is set                                                     |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |  |  |

|              |                                                                                                                                  |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

| bit 15       | GIE: Global                                                                                                                      | Interrupt Enable                                                     | e bit         |                  |                  |                 |        |  |  |  |  |  |  |

|              | 1 = Interrupt                                                                                                                    | s and associate                                                      | d IE bits are | enabled          |                  |                 |        |  |  |  |  |  |  |

|              |                                                                                                                                  | s are disabled, I                                                    | •             | still enabled    |                  |                 |        |  |  |  |  |  |  |

| bit 14       | DISI: DISI Instruction Status bit                                                                                                |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

|              |                                                                                                                                  | 1 = DISI instruction is active<br>0 = DISI instruction is not active |               |                  |                  |                 |        |  |  |  |  |  |  |

| bit 13       | SWTRAP: Software Trap Status bit                                                                                                 |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

|              |                                                                                                                                  | e trap is enabled<br>e trap is disabled                              |               |                  |                  |                 |        |  |  |  |  |  |  |

| bit 12-3     | Unimpleme                                                                                                                        | nted: Read as '                                                      | 0'            |                  |                  |                 |        |  |  |  |  |  |  |

| bit 2        | INT2EP: Ext                                                                                                                      | ternal Interrupt 2                                                   | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |  |

|              |                                                                                                                                  | on negative edg                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

| bit 1        | INT1EP: Ext                                                                                                                      | ternal Interrupt 1                                                   | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |  |

|              |                                                                                                                                  | on negative edg                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

| bit 0        | INTOEP: Ext                                                                                                                      | ternal Interrupt C                                                   | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |  |

|              | INTOEP: External Interrupt 0 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                                      |               |                  |                  |                 |        |  |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                                                                  | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0 |  |  |  |  |  |

|----------------------------------------------------------------------|--------------|----------------------------------------------------------|---------------|-------------------|---------------|-----------------|-------|--|--|--|--|--|

| —                                                                    |              |                                                          |               | IC4R<6:0>         |               |                 |       |  |  |  |  |  |

| bit 15                                                               |              |                                                          |               |                   |               |                 | bit 8 |  |  |  |  |  |

|                                                                      |              |                                                          |               |                   |               |                 |       |  |  |  |  |  |

| U-0                                                                  | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0 |  |  |  |  |  |

| —                                                                    |              |                                                          |               | IC3R<6:0>         |               |                 |       |  |  |  |  |  |

| bit 7                                                                |              |                                                          |               |                   |               |                 | bit C |  |  |  |  |  |

|                                                                      |              |                                                          |               |                   |               |                 |       |  |  |  |  |  |

| Legend:                                                              |              |                                                          |               |                   |               |                 |       |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |              |                                                          |               |                   |               |                 |       |  |  |  |  |  |

| -n = Value a                                                         | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown  |  |  |  |  |  |

|                                                                      | 0000001 =    | 1111001 = Input tied to RPI121                           |               |                   |               |                 |       |  |  |  |  |  |

| bit 7                                                                | Unimpleme    | nted: Read as 'o                                         | )'            |                   |               |                 |       |  |  |  |  |  |

| bit 6-0                                                              | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi | n bits          |       |  |  |  |  |  |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                                                                                                                                                                                               | R/W-1, HC                                                        | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |  |  |

|--------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|------------------|-----------------|----------------|--|--|--|--|--|--|

| I2CEN        | _                            | I2CSIDL                                                                                                                                                                                                             | SCLREL                                                           | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |  |  |  |  |  |  |

| bit 15       |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 | bit 8          |  |  |  |  |  |  |

|              |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

| R/W-0        | R/W-0                        | R/W-0                                                                                                                                                                                                               | R/W-0, HC                                                        | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |  |  |  |  |  |  |

| GCEN         | STREN                        | ACKDT                                                                                                                                                                                                               | ACKEN                                                            | RCEN                         | PEN              | RSEN            | SEN            |  |  |  |  |  |  |

| bit 7        |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 | bit 0          |  |  |  |  |  |  |

| Legend:      |                              | HC = Hardware                                                                                                                                                                                                       | Cloarable bit                                                    |                              |                  |                 |                |  |  |  |  |  |  |

| R = Readab   | le hit                       | W = Writable bi                                                                                                                                                                                                     |                                                                  | II = I Inimpler              | mented bit, rea  | d as '0'        |                |  |  |  |  |  |  |

| -n = Value a |                              | '1' = Bit is set                                                                                                                                                                                                    | L .                                                              | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |  |  |  |  |  |  |

|              |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 | nown           |  |  |  |  |  |  |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                                                                                                                                                                                                          |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | he I2Cx module                                                                                                                                                                                                      |                                                                  |                              |                  |                 | ;              |  |  |  |  |  |  |

|              | 0 = Disables                 | the I2Cx module;                                                                                                                                                                                                    | all l <sup>2</sup> C™ pins                                       | are controlled               | by port functior | ıs              |                |  |  |  |  |  |  |

| bit 14       | Unimplemen                   | ted: Read as '0'                                                                                                                                                                                                    |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

| bit 13       |                              | x Stop in Idle Mo                                                                                                                                                                                                   |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | ues module oper<br>s module operation                                                                                                                                                                               |                                                                  |                              | dle mode         |                 |                |  |  |  |  |  |  |

| bit 12       |                              | •                                                                                                                                                                                                                   |                                                                  | _                            | ( clave)         |                 |                |  |  |  |  |  |  |

|              |                              | <b>SCLREL:</b> SCLx Release Control bit (when operating as I <sup>2</sup> C slave)<br>1 = Releases SCLx clock                                                                                                       |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | 0 = Holds SCLx clock low (clock stretch)                                                                                                                                                                            |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              | If STREN = 1                 | If STREN = 1:                                                                                                                                                                                                       |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              | •                            | Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear at the beginning of every slave data byte transmission. Hardware is clear at the end of every slave |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 | t every slave  |  |  |  |  |  |  |

|              | If STREN = 0                 | -                                                                                                                                                                                                                   | Hardware is clear at the end of every slave data byte reception. |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at the beginning of every                                                                                                        |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              | -                            | te transmission.                                                                                                                                                                                                    |                                                                  |                              | -                | address byte re | eception.      |  |  |  |  |  |  |

| bit 11       |                              | ligent Peripheral                                                                                                                                                                                                   |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                                                                                                                                                                                                   | addresses are                                                    | Acknowledged                 | 1                |                 |                |  |  |  |  |  |  |

| bit 10       |                              | Slave Address b                                                                                                                                                                                                     | i+                                                               |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | is a 10-bit slave                                                                                                                                                                                                   |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | is a 7-bit slave a                                                                                                                                                                                                  |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                                                                                                                                                                                                    | Control bit                                                      |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | control is disable                                                                                                                                                                                                  |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

|              |                              | control is enable                                                                                                                                                                                                   |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

| bit 8        |                              | us Input Levels b                                                                                                                                                                                                   |                                                                  | 0145                         | <b>c</b>         |                 |                |  |  |  |  |  |  |

|              |                              | /O pin thresholds<br>SMBus input thre                                                                                                                                                                               |                                                                  | n SMBus speci                | fication         |                 |                |  |  |  |  |  |  |

| bit 7        |                              | ral Call Enable b                                                                                                                                                                                                   |                                                                  | ing as I <sup>2</sup> C slav | /e)              |                 |                |  |  |  |  |  |  |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat                                                                                                                                                                              | neral call addre                                                 | -                            |                  | dule is enabled | for reception) |  |  |  |  |  |  |

|              |                              |                                                                                                                                                                                                                     |                                                                  |                              |                  |                 |                |  |  |  |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | - 1                                |         |                  |                 |                 |         |  |  |  |  |

|                         | 00001 = Filte<br>00000 = Filte       |                                    |         |                  |                 |                 |         |  |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 1000101-1111111 = Reserved           |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 1000100 = FIFO almost full interrupt |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

## 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

| Bit Field             | Description                                                                                                                                                                                   |  |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| WDTPRE                | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                         |  |  |  |  |  |  |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         |  |  |  |  |  |  |

| WDTWIN<1:0>           | Watchdog Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period |  |  |  |  |  |  |

| ALTI2C1               | Alternate I2C1 pin<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                  |  |  |  |  |  |  |

| ALTI2C2               | Alternate I2C2 pin<br>1 = I2C2 is mapped to the SDA2/SCL2 pins<br>0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                  |  |  |  |  |  |  |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                |  |  |  |  |  |  |

| ICS<1:0>              | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use       |  |  |  |  |  |  |

## TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| АС СН        | ARACTERIS | TICS                                      |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |               |            |                                                                             |  |  |

|--------------|-----------|-------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------------|-----------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol    | cteristic <sup>(2)</sup>                  | Min.                                | Тур.                                                                                                                                                                                                                                                                                    | Max. | Units         | Conditions |                                                                             |  |  |

| TA10         | ТтхН      | T1CK High<br>Time                         | Synchronous<br>mode                 | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                    |      | _             | ns         | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |  |

|              |           |                                           | Asynchronous                        | 35                                                                                                                                                                                                                                                                                      | _    | —             | ns         |                                                                             |  |  |

| TA11         | ΤτχL      | T1CK Low<br>Time                          | Synchronous<br>mode                 | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                                                                                                                                                    | _    | _             | ns         | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |  |

|              |           |                                           | Asynchronous                        | 10                                                                                                                                                                                                                                                                                      |      | —             | ns         |                                                                             |  |  |

| TA15         | ΤτχΡ      | T1CK Input Synchronous<br>Period mode     |                                     | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                                                                                                                                                  | _    | —             | ns         | N = prescale value<br>(1, 8, 64, 256)                                       |  |  |

| OS60         | Ft1       |                                           | ange (oscillator<br>etting bit, TCS | DC                                                                                                                                                                                                                                                                                      |      | 50            | kHz        |                                                                             |  |  |

| TA20         | TCKEXTMRL | Delay from E<br>Clock Edge t<br>Increment | xternal T1CK<br>to Timer            | 0.75 Tcy + 40                                                                                                                                                                                                                                                                           | _    | 1.75 Tcy + 40 | ns         |                                                                             |  |  |

**Note 1:** Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

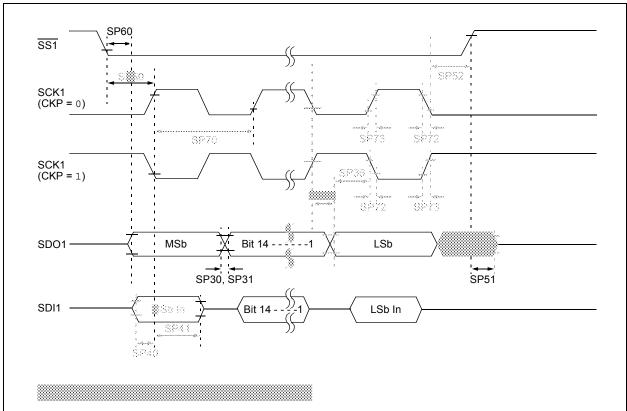

#### FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS        |                  |                                                                        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |                              |        |                                            |  |  |

|---------------------------|------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|--------|--------------------------------------------|--|--|

| Param<br>No.              | Symbol           | Characteristic                                                         | Min.                                                                                                                                                                                                                 | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |  |  |

| Op Amp DC Characteristics |                  |                                                                        |                                                                                                                                                                                                                      |                     |                              |        |                                            |  |  |

| CM40                      | VCMR             | Common-Mode Input<br>Voltage Range                                     | AVss                                                                                                                                                                                                                 | _                   | AVDD                         | V      |                                            |  |  |

| CM41                      | CMRR             | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                          | —                                                                                                                                                                                                                    | 40                  | —                            | db     | VCM = AVDD/2                               |  |  |

| CM42                      | VOFFSET          | Op Amp Offset<br>Voltage <sup>(3)</sup>                                | —                                                                                                                                                                                                                    | ±5                  | —                            | mV     |                                            |  |  |

| CM43                      | Vgain            | Open-Loop Voltage<br>Gain <sup>(3)</sup>                               | _                                                                                                                                                                                                                    | 90                  | _                            | db     |                                            |  |  |

| CM44                      | los              | Input Offset Current                                                   | _                                                                                                                                                                                                                    | -                   | _                            | _      | See pad leakage currents in Table 30-11    |  |  |

| CM45                      | lв               | Input Bias Current                                                     | —                                                                                                                                                                                                                    | _                   | —                            | _      | See pad leakage currents in Table 30-11    |  |  |

| CM46                      | Ιουτ             | Output Current                                                         | _                                                                                                                                                                                                                    |                     | 420                          | μA     | With minimum value of RFEEDBACK (CM48)     |  |  |

| CM48                      | RFEEDBACK        | Feedback Resistance<br>Value                                           | 8                                                                                                                                                                                                                    | -                   | _                            | kΩ     |                                            |  |  |

| CM49a                     | VOADC            | Output Voltage                                                         | AVss + 0.077                                                                                                                                                                                                         | —                   | AVDD - 0.077                 | V      | Ιουτ = 420 μΑ                              |  |  |

|                           |                  | Measured at OAx Using                                                  | AVss + 0.037                                                                                                                                                                                                         | —                   | AVDD - 0.037                 | V      | Ιουτ = 200 μΑ                              |  |  |

|                           |                  | ADC <sup>(3,4)</sup>                                                   | AVss + 0.018                                                                                                                                                                                                         |                     | AVDD - 0.018                 | V      | Ιουτ = 100 μΑ                              |  |  |

| CM49b                     | VOUT             | Output Voltage                                                         | AVss + 0.210                                                                                                                                                                                                         | —                   | AVDD - 0.210                 | V      | Ιουτ = 420 μΑ                              |  |  |