Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

$\mathbf{X}$

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc202-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 4         | -16:  | QEI1   | EI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY                                           |         |                    |        |        |         |                        |        |        |        |        |       |       |       |       |               |

|-----------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------|--------|---------|------------------------|--------|--------|--------|--------|-------|-------|-------|-------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14                                                                                                                | Bit 13  | Bit 12             | Bit 11 | Bit 10 | Bit 9   | Bit 8                  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                                                                                                                     | QEISIDL | QEISIDL PIMOD<2:0> |        |        | IMV     | IMV<1:0> — INTDIV<2:0> |        |        | >      | CNTPOL | GATEN | CCM   | <1:0> | 0000  |               |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN                                                                                                                |         | QFDIV<2:0>         |        | OUTFN  | NC<1:0> | SWPAB                  | HOMPOL | IDXPOL | QEBPOL | QEAPOL | HOME  | INDEX | QEB   | QEA   | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | - PCHEQIRQ PCHEQIEN PCLEQIRQ PCLEQIEN POSOVIRQ POSOVIEN PCIIRQ PCIEN VELOVIRQ VELOVIEN HOMIRQ HOMIEN IDXIRQ IDXIEN 00 |         |                    |        |        |         |                        | 0000   |        |        |        |       |       |       |       |               |

| POS1CNTL        | 01C6  |        |                                                                                                                       |         |                    |        |        |         | POSCNT<15              | :0>    |        |        |        |       |       |       |       | 0000          |

| POS1CNTH        | 01C8  |        | POSCNT<31:16> 0000                                                                                                    |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| POS1HLD         | 01CA  |        | POSHLD<15:0> 0000                                                                                                     |         |                    |        |        |         |                        |        |        |        |        |       |       |       |       |               |

| VEL1CNT         | 01CC  |        | VELCNT<15:0> 0000                                                                                                     |         |                    |        |        |         |                        |        |        |        |        |       |       |       |       |               |

| INT1TMRL        | 01CE  |        | INTTMR<15:0> 0000                                                                                                     |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| INT1TMRH        | 01D0  |        | INTTMR<31:16> 00                                                                                                      |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| INT1HLDL        | 01D2  |        |                                                                                                                       |         |                    |        |        |         | INTHLD<15:             | )>     |        |        |        |       |       |       |       | 0000          |

| INT1HLDH        | 01D4  |        |                                                                                                                       |         |                    |        |        |         | INTHLD<31:1            | 6>     |        |        |        |       |       |       |       | 0000          |

| INDX1CNTL       | 01D6  |        |                                                                                                                       |         |                    |        |        |         | INDXCNT<15             | :0>    |        |        |        |       |       |       |       | 0000          |

| INDX1CNTH       | 01D8  |        |                                                                                                                       |         |                    |        |        |         | NDXCNT<31:             | 16>    |        |        |        |       |       |       |       | 0000          |

| INDX1HLD        | 01DA  |        |                                                                                                                       |         |                    |        |        |         | INDXHLD<15             | :0>    |        |        |        |       |       |       |       | 0000          |

| QEI1GECL        | 01DC  |        |                                                                                                                       |         |                    |        |        |         | QEIGEC<15              | 0>     |        |        |        |       |       |       |       | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        | QEIIC<15:0> 000                                                                                                       |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| QEI1GECH        | 01DE  |        | QEIGEC<31:16> 000                                                                                                     |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| QEI1ICH         | 01DE  |        | QEIIC<31:16> 000                                                                                                      |         |                    |        |        |         |                        |        | 0000   |        |        |       |       |       |       |               |

| QEI1LECL        | 01E0  |        | QEILEC<15:0> 000                                                                                                      |         |                    |        |        |         |                        | 0000   |        |        |        |       |       |       |       |               |

| <b>QEI1LECH</b> | 01E2  |        | QEILEC<31:16> 0000                                                                                                    |         |                    |        |        |         |                        | 0000   |        |        |        |       |       |       |       |               |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | —      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND/        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

| R/W-0                 | R/W-0                                                                                                                                                                                                                                                                                        | R/W-0                           | R/W-0            | R/W-0            | U-0             | U-0             | U-0   |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|-----------------|-------|--|

| CHEN                  | SIZE                                                                                                                                                                                                                                                                                         | DIR                             | HALF             | NULLW            |                 |                 |       |  |

| bit 15                |                                                                                                                                                                                                                                                                                              |                                 |                  |                  |                 |                 | bit   |  |

| U-0                   | U-0                                                                                                                                                                                                                                                                                          | R/W-0                           | R/W-0            | U-0              | U-0             | R/W-0           | R/W-0 |  |

|                       | 0-0                                                                                                                                                                                                                                                                                          | AMODE1                          | AMODE0           | 0-0              | 0-0             | MODE1           | MODE0 |  |

| bit 7                 |                                                                                                                                                                                                                                                                                              | AWODET                          | 7 WIODE0         |                  |                 | MODET           | bit   |  |

| Lovende               |                                                                                                                                                                                                                                                                                              |                                 |                  |                  |                 |                 |       |  |

| Legend:<br>R = Readab | lo hit                                                                                                                                                                                                                                                                                       | M - Mritabla                    | hit.             |                  | monted bit rec  | ud aa '0'       |       |  |

|                       |                                                                                                                                                                                                                                                                                              | W = Writable                    |                  | -                | mented bit, rea |                 |       |  |

| -n = Value a          | IT POR                                                                                                                                                                                                                                                                                       | '1' = Bit is set                |                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |

| bit 15                | CHEN: DMA                                                                                                                                                                                                                                                                                    | Channel Enabl                   | e bit            |                  |                 |                 |       |  |

|                       | 1 = Channel<br>0 = Channel                                                                                                                                                                                                                                                                   |                                 |                  |                  |                 |                 |       |  |

| bit 14                |                                                                                                                                                                                                                                                                                              | ata Transfer S                  | ze hit           |                  |                 |                 |       |  |

|                       | 1 = Byte                                                                                                                                                                                                                                                                                     |                                 |                  |                  |                 |                 |       |  |

|                       | 0 = Word                                                                                                                                                                                                                                                                                     |                                 |                  |                  |                 |                 |       |  |

| bit 13                | DIR: DMA Tra                                                                                                                                                                                                                                                                                 | ansfer Directior                | n bit (source/d  | estination bus   | select)         |                 |       |  |

|                       |                                                                                                                                                                                                                                                                                              | om RAM addre<br>om peripheral a |                  |                  |                 |                 |       |  |

| bit 12                |                                                                                                                                                                                                                                                                                              | Block Transfer                  |                  |                  |                 |                 |       |  |

|                       | 1 = Initiates i                                                                                                                                                                                                                                                                              | nterrupt when                   | half of the data | a has been mo    |                 |                 |       |  |

| bit 11                |                                                                                                                                                                                                                                                                                              | Data Periphera                  |                  |                  |                 |                 |       |  |

|                       |                                                                                                                                                                                                                                                                                              | write to periph                 |                  |                  | e (DIR bit must | also be clear)  |       |  |

| bit 10-6              | Unimplemen                                                                                                                                                                                                                                                                                   | ted: Read as '                  | 0'               |                  |                 |                 |       |  |

| bit 5-4               | AMODE<1:0                                                                                                                                                                                                                                                                                    | -: DMA Chann                    | el Addressing    | Mode Select b    | oits            |                 |       |  |

|                       | AMODE<1:0>: DMA Channel Addressing Mode Select bits<br>11 = Reserved<br>10 = Peripheral Indirect Addressing mode<br>01 = Register Indirect without Post-Increment mode<br>00 = Register Indirect with Post-Increment mode                                                                    |                                 |                  |                  |                 |                 |       |  |

| bit 3-2               | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                   |                                 |                  |                  |                 |                 |       |  |

| bit 1-0               | -                                                                                                                                                                                                                                                                                            |                                 |                  | de Select bits   |                 |                 |       |  |

|                       | MODE<1:0>: DMA Channel Operating Mode Select bits<br>11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)<br>10 = Continuous, Ping-Pong modes are enabled<br>01 = One-Shot, Ping-Pong modes are disabled<br>00 = Continuous, Ping-Pong modes are disabled |                                 |                  |                  |                 |                 |       |  |

### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|------------------|-----|------------------|------|----------------------|-------------|-----------------|-------|

|                  |     |                  | DSAD | DR<15:8>             |             |                 |       |

| bit 15           |     |                  |      |                      |             |                 | bit 8 |

|                  |     |                  |      |                      |             |                 |       |

| R-0              | R-0 | R-0              | R-0  | R-0                  | R-0         | R-0             | R-0   |

|                  |     |                  | DSA  | DR<7:0>              |             |                 |       |

| bit 7            |     |                  |      |                      |             |                 | bit 0 |

|                  |     |                  |      |                      |             |                 |       |

| Legend:          |     |                  |      |                      |             |                 |       |

| R = Readable b   | it  | W = Writable bit |      | U = Unimplemen       | ted bit, re | ad as '0'       |       |

| -n = Value at PC | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d           | x = Bit is unkn | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:                                                                                    |                                                                                                                                    |                                                          |                                    |                    |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readat                                                                                 | ole bit                                                                                                                            | W = Writable bit                                         | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value a                                                                               | at POR                                                                                                                             | '1' = Bit is set                                         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-4                                                                                   | Unimplo                                                                                                                            | montod: Dood os 'o'                                      |                                    |                    |  |  |  |  |

| bit 15-4Unimplemented: Read as '0'bit 3PPST3: DMA Channel 3 Ping-Pong Mode Status Flag bit |                                                                                                                                    |                                                          |                                    |                    |  |  |  |  |

| bit 5                                                                                      | 1 = DMA                                                                                                                            | ASTB3 register is selected<br>ASTA3 register is selected | vioue Status Flag bit              |                    |  |  |  |  |

| bit 2                                                                                      | <b>PPST2:</b> DMA Channel 2 Ping-Pong Mode Status Flag bit<br>1 = DMASTB2 register is selected<br>0 = DMASTA2 register is selected |                                                          |                                    |                    |  |  |  |  |

| bit 1 PPST1:                                                                               |                                                                                                                                    | MA Channel 1 Ping-Pong Mode Status Flag bit              |                                    |                    |  |  |  |  |

|                                                                                            | 1 - DMACTD1 register is calculated                                                                                                 |                                                          |                                    |                    |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

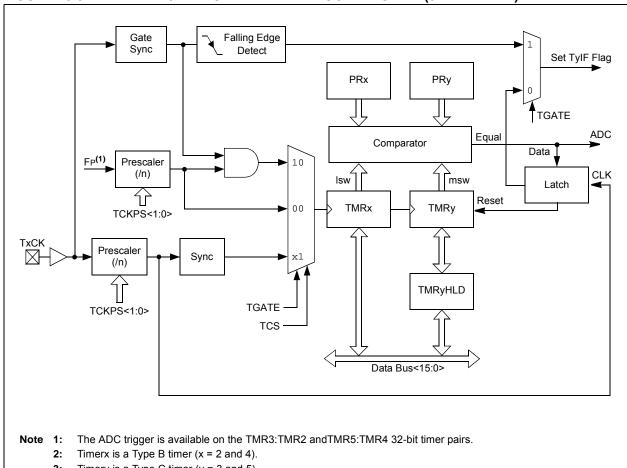

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|-------------------|-------|-----------------|-------|

|                                    |       |       | INTHL                              | D<31:24>          |       |                 |       |

| bit 15                             |       |       |                                    |                   |       |                 | bit 8 |

|                                    |       |       |                                    |                   |       |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                    |       |       | INTHL                              | D<23:16>          |       |                 |       |

| bit 7                              |       |       |                                    |                   |       |                 | bit 0 |

|                                    |       |       |                                    |                   |       |                 |       |

| Legend:                            |       |       |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at POR (1' = Bit is set |       |       |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

### REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|------------------|-------|-----------------|-------|

|                                    |       |       | INTHL                              | .D<15:8>         |       |                 |       |

| bit 15                             |       |       |                                    |                  |       |                 | bit 8 |

|                                    |       |       |                                    |                  |       |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                                    |       |       | INTH                               | _D<7:0>          |       |                 |       |

| bit 7                              |       |       |                                    |                  |       |                 | bit 0 |

|                                    |       |       |                                    |                  |       |                 |       |

| Legend:                            |       |       |                                    |                  |       |                 |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |                  |       |                 |       |

| -n = Value at POR '1' = Bit is set |       |       |                                    | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

|                                    |       |       |                                    |                  |       |                 |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

NOTES:

### 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |  |

|--------|-----|-----|-----|----------|----------|----------|----------|--|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |  |

| bit 15 |     |     |     |          |          |          | bit 8    |  |

|        |     |     |     |          |          |          |          |  |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienenteu. Reau as 0                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| DC CHARACTERISTICS |                       |                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                                                                                                                                   |  |

|--------------------|-----------------------|-----------------------------------------|-------------------------------------------------------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol Characteristic |                                         |                                                       | Тур. | Max. | Units | Conditions                                                                                                                                        |  |

|                    | liL                   | Input Leakage Current <sup>(1,2)</sup>  |                                                       |      |      |       |                                                                                                                                                   |  |

| DI50               |                       | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                    | —    | +1   | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                         |  |

| DI51               |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \mbox{ at high-impedance}, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |  |

| DI51a              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                           |  |

| DI51b              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                          |  |

| DI51c              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                          |  |

| DI55               |                       | MCLR                                    | -5                                                    | —    | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                          |  |

| DI56               |                       | OSC1                                    | -5                                                    | —    | +5   | μΑ    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$             |  |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

# 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

| DC CHAF | DC CHARACTERISTICS |                                                             |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |       |                                                                    |  |  |

|---------|--------------------|-------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------------------|--|--|

| Param.  | Symbol             | Characteristic                                              | Min. | Тур.                                                                                                                              | Max. | Units | Conditions                                                         |  |  |

| HDO10   | Vol                | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |      |                                                                                                                                   | 0.4  | V     | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)                                 |  |  |

|         |                    | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | —    | _                                                                                                                                 | 0.4  | V     | IOL ≤ 8 mA, VDD = 3.3V<br>(Note 1)                                 |  |  |

| HDO20   | Vон                | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4  |                                                                                                                                   | —    | V     | IOH ≥ -10 mA, VDD = 3.3V<br>(Note 1)                               |  |  |

|         |                    | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4  | _                                                                                                                                 | —    | V     | ІОн ≥ 15 mA, VDD = 3.3V<br>(Note 1)                                |  |  |

| HDO20A  | Vон1               | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5  | -                                                                                                                                 | —    | V     | IOH ≥ -3.9 mA, VDD = 3.3V<br>(Note 1)                              |  |  |

|         |                    |                                                             | 2.0  | _                                                                                                                                 | —    |       | $IOH \ge -3.7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>(Note 1)  |  |  |

|         |                    |                                                             | 3.0  |                                                                                                                                   | —    |       | IOH ≥ -2 mA, VDD = 3.3V<br>(Note 1)                                |  |  |

|         |                    | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5  |                                                                                                                                   | _    | V     | IOH ≥ -7.5 mA, VDD = 3.3V<br>(Note 1)                              |  |  |

|         |                    |                                                             | 2.0  | _                                                                                                                                 | —    |       | $IOH \ge -6.8 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$<br>(Note 1) |  |  |

|         |                    |                                                             | 3.0  | _                                                                                                                                 | —    |       | IOH ≥ -3 mA, VDD = 3.3V<br>(Note 1)                                |  |  |

## TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

| Units                   |        | MILLIMETERS |      |       |

|-------------------------|--------|-------------|------|-------|

| Dimension               | Limits | MIN         | NOM  | MAX   |

| Number of Pins          | Ν      | 44          |      |       |

| Number of Pins per Side | ND     | 12          |      |       |

| Number of Pins per Side | NE     | 10          |      |       |

| Pitch                   | е      | 0.50 BSC    |      |       |

| Overall Height          | Α      | 0.80        | 0.90 | 1.00  |

| Standoff                | A1     | 0.025       | -    | 0.075 |

| Overall Width           | Е      | 6.00 BSC    |      |       |

| Exposed Pad Width       | E2     | 4.40        | 4.55 | 4.70  |

| Overall Length          | D      | 6.00 BSC    |      |       |

| Exposed Pad Length      | D2     | 4.40        | 4.55 | 4.70  |

| Contact Width           | b      | 0.20        | 0.25 | 0.30  |

| Contact Length          | L      | 0.20        | 0.25 | 0.30  |

| Contact-to-Exposed Pad  | К      | 0.20        | -    | -     |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.