Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc202-h-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0              | R/W-0              | R/W-0                | R-0                | R-0                | R-0                |

|--------|-----|--------------------|--------------------|----------------------|--------------------|--------------------|--------------------|

| VAR    | _   | US1 <sup>(1)</sup> | US0 <sup>(1)</sup> | EDT <sup>(1,2)</sup> | DL2 <sup>(1)</sup> | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15 |     |                    |                    |                      |                    |                    | bit 8              |

| R/W-0               | R/W-0               | R/W-1                | R/W-0                 | R/C-0               | R-0 | R/W-0              | R/W-0             |

|---------------------|---------------------|----------------------|-----------------------|---------------------|-----|--------------------|-------------------|

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup> | SATDW <sup>(1)</sup> | ACCSAT <sup>(1)</sup> | IPL3 <sup>(3)</sup> | SFA | RND <sup>(1)</sup> | IF <sup>(1)</sup> |

| bit 7               |                     |                      |                       |                     |     |                    | bit 0             |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 VAR: Variable Exception Processing Latency Control bit

1 = Variable exception processing latency is enabled

0 = Fixed exception processing latency is enabled

bit 14 **Unimplemented:** Read as '0'

bit 13-12 US<1:0>: DSP Multiply Unsigned/Signed Control bits<sup>(1)</sup>

11 = Reserved

10 = DSP engine multiplies are mixed-sign01 = DSP engine multiplies are unsigned

00 = DSP engine multiplies are signed

bit 11 **EDT:** Early DO Loop Termination Control bit<sup>(1,2)</sup>

1 = Terminates executing DO loop at end of current loop iteration

0 = No effect

bit 10-8 **DL<2:0>:** DO Loop Nesting Level Status bits<sup>(1)</sup>

111 = 7 DO loops are active

•

•

001 = 1 DO loop is active 000 = 0 DO loops are active

bit 7 SATA: ACCA Saturation Enable bit (1)

1 = Accumulator A saturation is enabled

0 = Accumulator A saturation is disabled

bit 6 SATB: ACCB Saturation Enable bit<sup>(1)</sup>

1 = Accumulator B saturation is enabled

0 = Accumulator B saturation is disabled

bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit<sup>(1)</sup>

1 = Data Space write saturation is enabled

0 = Data Space write saturation is disabled

bit 4 ACCSAT: Accumulator Saturation Mode Select bit<sup>(1)</sup>

1 = 9.31 saturation (super saturation)

0 = 1.31 saturation (normal saturation)

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(3)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: This bit is always read as '0'.

3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

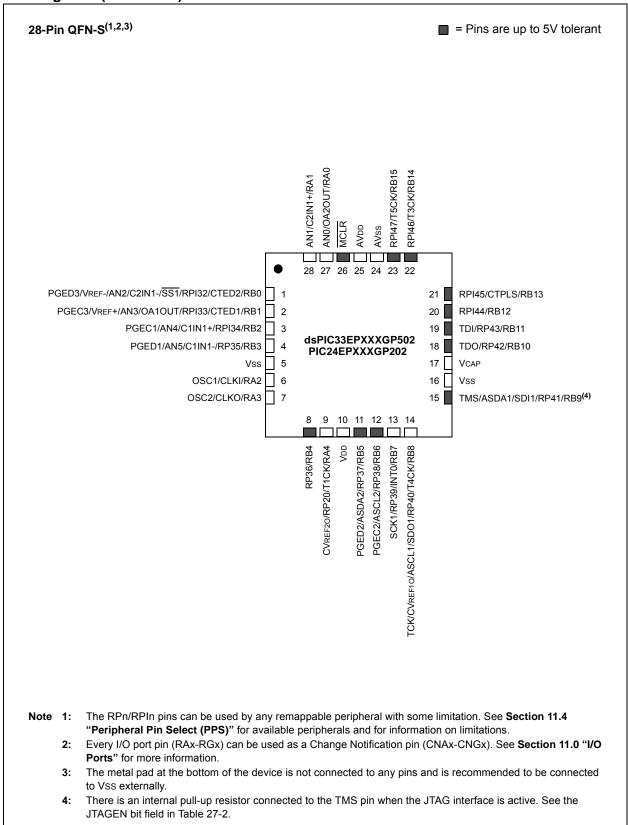

FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

DS70000657H-page 98

TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      |       |       | AMOD  | E<1:0> | _       | _      | MODE   | E<1:0> | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSEI | L<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 23:16>  |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 23:16>  |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | E<1:0> | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 23:16>  |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 23:16>  |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | E<1:0> | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSEI | L<7:0>  |        |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 23:16>  |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 23:16>  |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | E<1:0> | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  | •      |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 23:16>  |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 23:16>  |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | l<3:0> | •      | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | DSADR  | <23:16> |        |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY **TABLE 4-56:**

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | -      | _      | -      | -      | 1      | 1      | _     | TRISA8 | -     | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | -      | -      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | -      | -      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | -      | -      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | -      | -      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | -      | -      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | -      | -      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | _      | _      | _      |        | _      | _     | _      | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      |        | -      | 1      | 1      | 1      | _     | TRISC8 | _     | -     | _     | _     | 1     | _     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  | _      | _      | -      | -      | -      | _      | _     | RC8    | -     | _     | _     | -     | -     | _     | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | _      | _      | -      | -      | -      | _      | _     | LATC8  | -     | _     | _     | -     | -     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | _      | _      | -      | -      | -      | _      | _     | ODCC8  | -     | _     | _     | -     | -     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | _      | _      | -      | -      | -      | _      | _     | CNIEC8 | -     | _     | _     | -     | -     | _     | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | _      | _      | -      | -      | -      | _      | _     | CNPUC8 | -     | _     | _     | -     | -     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | _      | _      | -      | -      | -      | _      | _     | CNPDC8 | -     | _     | _     | -     | -     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _      | -      | ı      | ı      | -      | ı      | -     | _      | -     | ı     | _     | -     | ı     | _     | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

W = Writable bit

| R/W-0  | R/W-0                 | R/W-0                 | R/W-0                  | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

|--------|-----------------------|-----------------------|------------------------|------------------------|----------------------|----------------------|----------------------|

| NSTDIS | OVAERR <sup>(1)</sup> | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup> | COVBERR <sup>(1)</sup> | OVATE <sup>(1)</sup> | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| bit 15 | •                     |                       |                        |                        |                      |                      | bit 8                |

| R/W-0                   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------------------------|---------|---------|---------|---------|--------|---------|-------|

| SFTACERR <sup>(1)</sup> | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | _     |

| bit 7                   |         |         |         |         |        |         | bit 0 |

U = Unimplemented bit, read as '0'

x = Bit is unknown

| -n = Value at Po | OR '1' = Bit is set                                                                                                     | '0' = Bit is cleared                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| bit 15           | <b>NSTDIS:</b> Interrupt Nesting Disable bit 1 = Interrupt nesting is disabled                                          |                                          |

|                  | 0 = Interrupt nesting is enabled                                                                                        |                                          |

| bit 14           | OVAERR: Accumulator A Overflow Trap                                                                                     | · · · · · · · · · · · · · · · · · · ·    |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 13           | <b>OVBERR:</b> Accumulator B Overflow Tra                                                                               | p Flag bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap was caused by overflow of Acc</li><li>0 = Trap was not caused by overflow of</li></ul>                 |                                          |

| bit 12           | <b>COVAERR:</b> Accumulator A Catastrophi 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi | erflow of Accumulator A                  |

| bit 11           | COVBERR: Accumulator B Catastrophi                                                                                      | ic Overflow Trap Flag bit <sup>(1)</sup> |

|                  | 1 = Trap was caused by catastrophic ov 0 = Trap was not caused by catastrophi                                           | ic overflow of Accumulator B             |

| bit 10           | <b>OVATE:</b> Accumulator A Overflow Trap I                                                                             | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator A</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 9            | <b>OVBTE:</b> Accumulator B Overflow Trap                                                                               | Enable bit <sup>(1)</sup>                |

|                  | <ul><li>1 = Trap overflow of Accumulator B</li><li>0 = Trap is disabled</li></ul>                                       |                                          |

| bit 8            | COVTE: Catastrophic Overflow Trap Er                                                                                    | nable bit <sup>(1)</sup>                 |

|                  | <ul><li>1 = Trap on catastrophic overflow of Ac</li><li>0 = Trap is disabled</li></ul>                                  | cumulator A or B is enabled              |

| bit 7            | SFTACERR: Shift Accumulator Error St                                                                                    |                                          |

|                  | 1 = Math error trap was caused by an ir<br>0 = Math error trap was not caused by a                                      |                                          |

| bit 6            | <b>DIV0ERR:</b> Divide-by-Zero Error Status                                                                             |                                          |

|                  | 1 = Math error trap was caused by a div<br>0 = Math error trap was not caused by a                                      | -                                        |

| bit 5            | DMACERR: DMAC Trap Flag bit                                                                                             |                                          |

|                  |                                                                                                                         |                                          |

1 = DMAC trap has occurred0 = DMAC trap has not occurred

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

Legend:

R = Readable bit

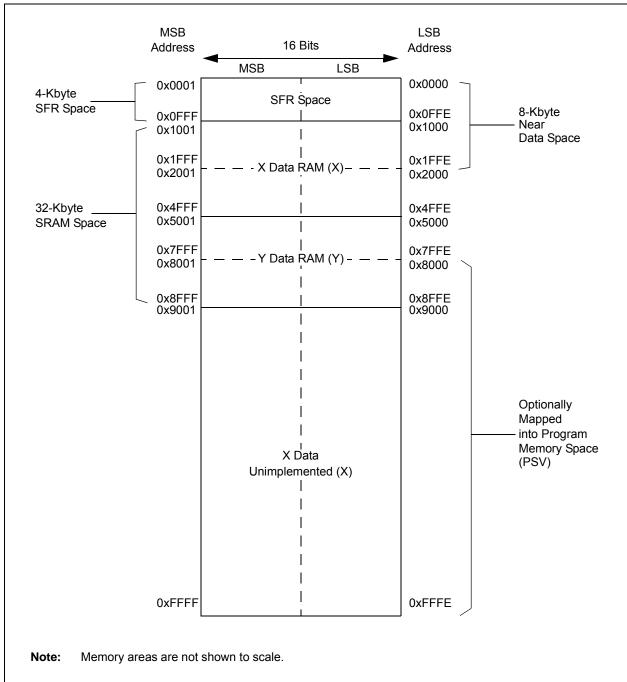

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of 'b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

## REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

# REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | DTCMP3R<6:0 | 0>    |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------------|-------|-------|-------|

| _     |       |       |       | DTCMP2R<6:0 | )>    |       |       |

| bit 7 |       |       |       |             |       |       | bit 0 |

| Legend | : |

|--------|---|

|--------|---|

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **DTCMP3R<6:0>:** Assign PWM Dead-Time Compensation Input 3 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 DTCMP2R<6:0>: Assign PWM Dead-Time Compensation Input 2 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL <sup>(2)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> | _   | _   | TCS <sup>(1,3)</sup> |       |

| bit 7 |                      |                       |                       |     |     |                      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timery On bit<sup>(1)</sup>

1 = Starts 16-bit Timery

0 = Stops 16-bit Timery

bit 14 **Unimplemented:** Read as '0'

bit 13 **TSIDL:** Timery Stop in Idle Mode bit<sup>(2)</sup>

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 **TGATE**: Timery Gated Time Accumulation Enable bit<sup>(1)</sup>

When TCS = 1: This bit is ignored.

When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timery Input Clock Prescale Select bits<sup>(1)</sup>

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timery Clock Source Select bit (1,3)

1 = External clock is from pin, TyCK (on the rising edge)

0 = Internal clock (FP)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When 32-bit operation is enabled (T2CON<3> = 1), these bits have no effect on Timery operation; all timer functions are set through TxCON.

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

**Note:** The ADC module needs to be disabled before modifying the AD12B bit.

### 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- · External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- · Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

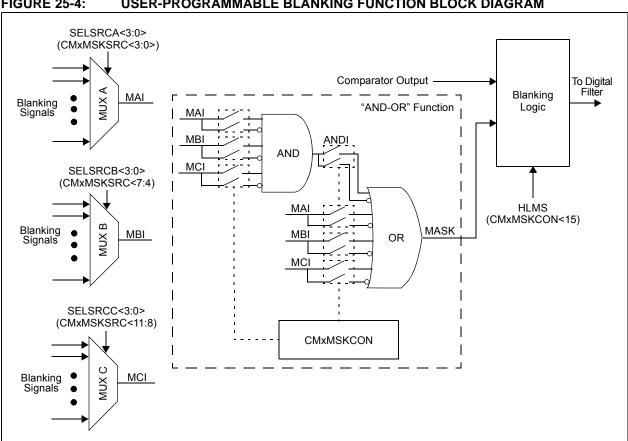

**FIGURE 25-4: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM**

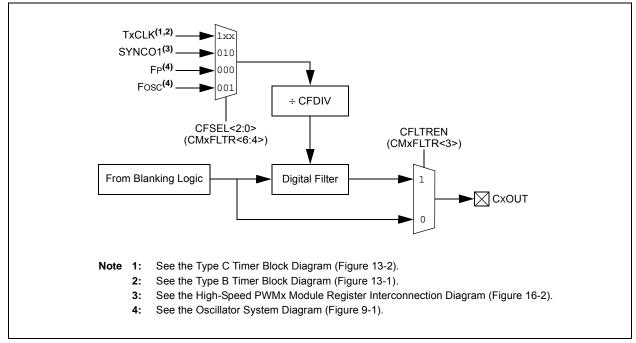

#### **FIGURE 25-5:** DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

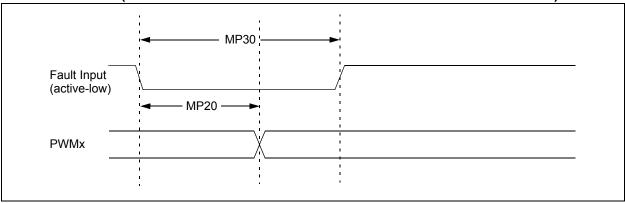

FIGURE 30-9: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

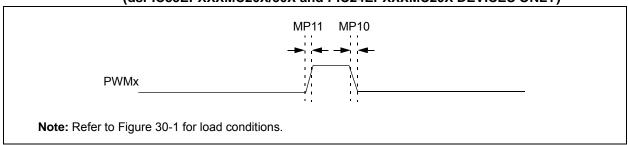

FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                  | (unless | rd Operate otherwise ng tempe | se stated<br>rature - | )<br>-40°C ≤ T | 3.0V to 3.6V<br>A ≤ +85°C for Industrial<br>A ≤ +125°C for Extended |

|--------------------|--------|----------------------------------|---------|-------------------------------|-----------------------|----------------|---------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min.    | Тур.                          | Max.                  | Units          | Conditions                                                          |

| MP10               | TFPWM  | PWMx Output Fall Time            | _       | _                             | _                     | ns             | See Parameter DO32                                                  |

| MP11               | TRPWM  | PWMx Output Rise Time            | _       | _                             | _                     | ns             | See Parameter DO31                                                  |

| MP20               | TFD    | Fault Input ↓ to PWMx I/O Change |         | _                             | 15                    | ns             |                                                                     |

| MP30               | TFH    | Fault Input Pulse Width          | 15      | _                             | _                     | ns             |                                                                     |

Note 1: These parameters are characterized but not tested in manufacturing.

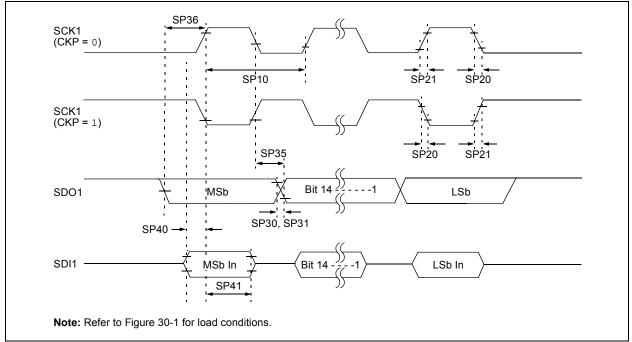

FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 30-43: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING REQUIREMENTS

|        |           |                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |                     |      |                          |                      |  |  |  |

|--------|-----------|-------------------------------|-----------------------------------------------------------------------|---------------------|------|--------------------------|----------------------|--|--|--|

| AC CHA | RACTERIST | TICS                          |                                                                       |                     |      | о т.                     | .0500 ()             |  |  |  |

|        |           |                               | Operating                                                             | temperat            |      | _                        | +85°C for Industrial |  |  |  |

|        |           |                               |                                                                       |                     | -40° | $^{\circ}C \leq TA \leq$ | +125°C for Extended  |  |  |  |

| Param. | Symbol    | Characteristic <sup>(1)</sup> | Min.                                                                  | Typ. <sup>(2)</sup> | Max. | Units                    | Conditions           |  |  |  |

| SP10   | FscP      | Maximum SCK1 Frequency        | _                                                                     | _                   | 10   | MHz                      | (Note 3)             |  |  |  |

| SP20   | TscF      | SCK1 Output Fall Time         | _                                                                     | _                   | _    | ns                       | See Parameter DO32   |  |  |  |

|        |           | '                             |                                                                       |                     |      |                          | (Note 4)             |  |  |  |

| SP21   | TscR      | SCK1 Output Rise Time         | _                                                                     | _                   | _    | ns                       | See Parameter DO31   |  |  |  |

|        |           | ·                             |                                                                       |                     |      |                          | (Note 4)             |  |  |  |

| SP30   | TdoF      | SDO1 Data Output Fall Time    | _                                                                     | _                   | _    | ns                       | See Parameter DO32   |  |  |  |

|        |           | ·                             |                                                                       |                     |      |                          | (Note 4)             |  |  |  |

| SP31   | TdoR      | SDO1 Data Output Rise Time    | _                                                                     | _                   | _    | ns                       | See Parameter DO31   |  |  |  |

|        |           | ·                             |                                                                       |                     |      |                          | (Note 4)             |  |  |  |

| SP35   | TscH2doV, | SDO1 Data Output Valid after  | _                                                                     | 6                   | 20   | ns                       |                      |  |  |  |

|        | TscL2doV  | SCK1 Edge                     |                                                                       |                     |      |                          |                      |  |  |  |

| SP36   | TdoV2sc,  | SDO1 Data Output Setup to     | 30                                                                    | _                   | _    | ns                       |                      |  |  |  |

|        | TdoV2scL  | First SCK1 Edge               |                                                                       |                     |      |                          |                      |  |  |  |

| SP40   | TdiV2scH, | Setup Time of SDI1 Data       | 30                                                                    | _                   | _    | ns                       |                      |  |  |  |

|        | TdiV2scL  | Input to SCK1 Edge            |                                                                       |                     |      |                          |                      |  |  |  |

| SP41   | TscH2diL, | Hold Time of SDI1 Data Input  | 30                                                                    |                     |      | ns                       |                      |  |  |  |

|        | TscL2diL  | to SCK1 Edge                  |                                                                       |                     |      |                          |                      |  |  |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

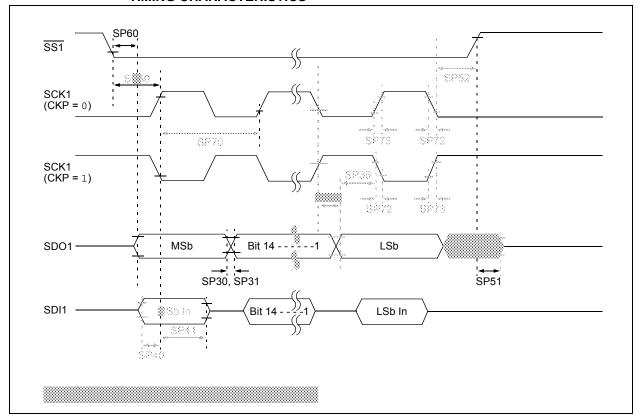

FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)

TIMING CHARACTERISTICS

| sPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/N | 1C20X |

|------------------------------------------------------------|-------|

| OTES:                                                      |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

|                                                            |       |

#### 33.0 PACKAGING INFORMATION

#### 33.1 Package Marking Information

#### 28-Lead SPDIP

#### Example

#### 28-Lead SOIC (.300")

#### Example

#### 28-Lead SSOP

#### Example

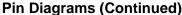

#### 28-Lead QFN-S (6x6x0.9 mm)

#### Example

| Legend: | XXX        | Customer-specific information                                                                                    |

|---------|------------|------------------------------------------------------------------------------------------------------------------|

|         | Υ          | Year code (last digit of calendar year)                                                                          |

|         | YY         | Year code (last 2 digits of calendar year)                                                                       |

|         | WW         | Week code (week of January 1 is week '01')                                                                       |

|         | NNN        | Alphanumeric traceability code                                                                                   |

|         | <b>e</b> 3 | Pb-free JEDEC designator for Matte Tin (Sn)                                                                      |

|         | *          | This package is Pb-free. The Pb-free JEDEC designator (©3) can be found on the outer packaging for this package. |

**Note:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

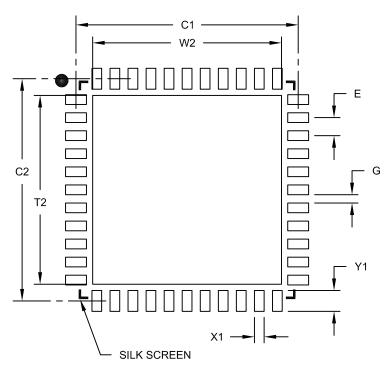

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                             | MILLIMETERS |      |      |      |

|-----------------------------|-------------|------|------|------|

| Dimension                   | MIN         | NOM  | MAX  |      |

| Contact Pitch               | 0.65 BSC    |      |      |      |

| Optional Center Pad Width   | W2          |      |      | 6.60 |

| Optional Center Pad Length  | T2          |      |      | 6.60 |

| Contact Pad Spacing         | C1          |      | 8.00 |      |

| Contact Pad Spacing         | C2          |      | 8.00 |      |

| Contact Pad Width (X44)     | X1          |      |      | 0.35 |

| Contact Pad Length (X44) Y1 |             |      |      | 0.85 |

| Distance Between Pads       | G           | 0.25 | ·    |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

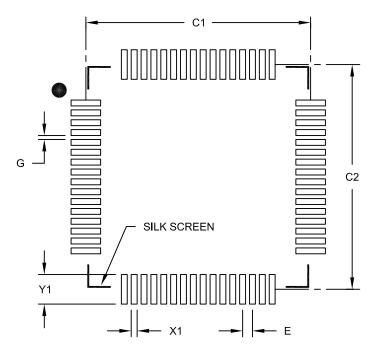

## 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | N   | <b>ILLIMETER</b> | S     |      |  |

|--------------------------|-----|------------------|-------|------|--|

| Dimension                | MIN | NOM              | MAX   |      |  |

| Contact Pitch            | Е   | 0.50 BSC         |       |      |  |

| Contact Pad Spacing      | C1  |                  | 11.40 |      |  |

| Contact Pad Spacing      | C2  |                  | 11.40 |      |  |

| Contact Pad Width (X64)  | X1  |                  |       | 0.30 |  |

| Contact Pad Length (X64) | Y1  |                  |       | 1.50 |  |

| Distance Between Pads    | G   | 0.20             |       |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

| DSPIC33EPXXXGP50X, DSPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |