#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc202-h-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

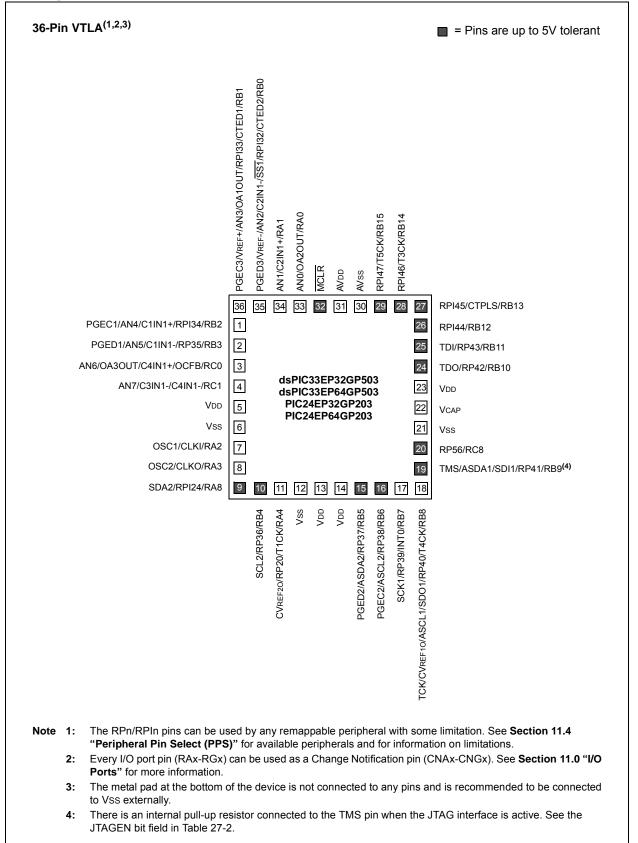

### **Pin Diagrams (Continued)**

|             |       |        |        |        |        |        |        | •            |              |               |              |       |        |       |       |       |       |               |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |        |        |        |        |        |        |              | Timer1       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |        |        |        |        |        |              | Period F     | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2        | 0106  |        |        |        |        |        |        |              | Timer2       | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108  |        |        |        |        |        | Time   | er3 Holding  | Register (fo | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A  |        |        |        |        |        |        |              | Timer3       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR2         | 010C  |        |        |        |        |        |        |              | Period F     | Register 2    |              |       |        |       |       |       |       | FFFF          |

| PR3         | 010E  |        |        |        |        |        |        |              | Period F     | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON    | —      | TSIDL  | —      | —      | —      | _            | —            | —             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112  | TON    | -      | TSIDL  | _      | _      | _      | _            | -            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   |       | 0000          |

| TMR4        | 0114  |        |        | •      | •      | •      | •      | •            | Timer4       | Register      |              |       |        | •     |       | •     |       | xxxx          |

| TMR5HLD     | 0116  |        |        |        |        |        | Т      | imer5 Holdir | ng Register  | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |        |        |        |        |        |              | Timer5       | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |        |        |        |        |        |              | Period F     | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |        |        |        |        |        |              | Period F     | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | —      | TSIDL  | —      | —      | —      | —            | _            | —             | TGATE        | TCKP  | S<1:0> | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _             | TGATE        | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

### TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| R/W-0                 | R/W-0                                                                                                                                      | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|--|--|--|--|

| CHEN                  | SIZE                                                                                                                                       | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |  |  |  |  |

| bit 15                |                                                                                                                                            |                                                      |                                               |                                    |                  |                 | bit     |  |  |  |  |

| U-0                   | U-0                                                                                                                                        | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |  |  |  |  |

|                       | 0-0                                                                                                                                        | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |  |  |  |  |

| bit 7                 |                                                                                                                                            | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |  |  |  |  |

| Lovende               |                                                                                                                                            |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

| Legend:<br>R = Readab | lo hit                                                                                                                                     | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |  |  |  |  |

|                       |                                                                                                                                            | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |  |  |  |  |

| -n = Value a          | IT POR                                                                                                                                     | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown    |  |  |  |  |

| bit 15                | CHEN: DMA                                                                                                                                  | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |  |  |  |  |

|                       | 1 = Channel                                                                                                                                |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

| bit 14                | <ul> <li>0 = Channel is disabled</li> <li>SIZE: DMA Data Transfer Size bit</li> </ul>                                                      |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

|                       |                                                                                                                                            | 1 = Byte                                             |                                               |                                    |                  |                 |         |  |  |  |  |

|                       | 0 = Word                                                                                                                                   |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

| bit 13                | DIR: DMA Transfer Direction bit (source/destination bus select)                                                                            |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

|                       |                                                                                                                                            | om RAM addre<br>om peripheral a                      |                                               |                                    |                  |                 |         |  |  |  |  |

| bit 12                | <ul> <li>0 = Reads from peripheral address, writes to RAM address</li> <li>HALF: DMA Block Transfer Interrupt Select bit</li> </ul>        |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

|                       | 1 = Initiates i                                                                                                                            | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |  |  |  |  |

| bit 11                | <ul> <li>0 = Initiates interrupt when all of the data has been moved</li> <li>NULLW: Null Data Peripheral Write Mode Select bit</li> </ul> |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

|                       |                                                                                                                                            | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |  |  |  |  |

| bit 10-6              | Unimplemen                                                                                                                                 | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |  |  |  |  |

| bit 5-4               | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                        |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register                                                                                              |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |  |  |  |  |

| bit 3-2               | Unimplemen                                                                                                                                 | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |  |  |  |  |

| bit 1-0               | -                                                                                                                                          | DMA Channel                                          |                                               | de Select bits                     |                  |                 |         |  |  |  |  |

|                       | 11 = One-Sho<br>10 = Continue                                                                                                              | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |  |  |  |  |

### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

| R/W-0           | R/W-0                                                                                                                                                 | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                                                                  | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |  |

| bit 15          |                                                                                                                                                       |                                   | •                    |                        |                    |                 | bit 8     |  |  |  |  |

|                 |                                                                                                                                                       |                                   |                      |                        |                    |                 |           |  |  |  |  |

| R/W-0           | R/W-1                                                                                                                                                 | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                                                                              | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |  |

| bit 7           |                                                                                                                                                       |                                   |                      |                        |                    |                 | bit (     |  |  |  |  |

|                 |                                                                                                                                                       |                                   |                      |                        |                    |                 |           |  |  |  |  |

| Legend:         |                                                                                                                                                       |                                   |                      |                        |                    |                 |           |  |  |  |  |

| R = Readable    |                                                                                                                                                       | W = Writable                      |                      | -                      | nented bit, read   |                 |           |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                   | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |  |

| h:+ 45          |                                                                                                                                                       | on Interview h                    |                      |                        |                    |                 |           |  |  |  |  |

| bit 15          |                                                                                                                                                       | on Interrupt bis will clear the l |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                                                       | s have no effect                  |                      | EN bit                 |                    |                 |           |  |  |  |  |

| bit 14-12       | •                                                                                                                                                     |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | DOZE<2:0>: Processor Clock Reduction Select bits <sup>(1)</sup><br>111 = Fcy divided by 128                                                           |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 110 = Fcy divided by 64                                                                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 101 = Fcy divided by 32                                                                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 100 = Fcy divided by 16<br>011 = Fcy divided by 8 (default)                                                                                           |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 011 = FCY divided by 8 (default)010 = FCY divided by 4                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 001 = Fcy divided by 2                                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 000 = Fcy divided by 1                                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

| bit 11          | <b>DOZEN:</b> Doze Mode Enable bit <sup>(2,3)</sup><br>1 = DOZE<2:0> field specifies the ratio between the peripheral clocks and the processor clocks |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                                                       |                                   |                      |                        |                    | nd the process  | or clocks |  |  |  |  |

|                 |                                                                                                                                                       | -                                 | -                    | ratio is forced to     |                    |                 |           |  |  |  |  |

| bit 10-8        | FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits                                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 111 = FRC divided by 256<br>110 = FRC divided by 64                                                                                                   |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 101 = FRC divided by 64<br>101 = FRC divided by 32                                                                                                    |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 100 = FRC divided by 16                                                                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 011 = FRC divided by 8                                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 010 = FRC divided by 4                                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 001 = FRC divided by 2<br>000 = FRC divided by 1 (default)                                                                                            |                                   |                      |                        |                    |                 |           |  |  |  |  |

| bit 7-6         | PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)                                                               |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 11 = Output divided by 8                                                                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 10 = Reserved                                                                                                                                         |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                                                       | livided by 4 (de                  | efault)              |                        |                    |                 |           |  |  |  |  |

| bit 5           | 00 = Output d                                                                                                                                         | ted: Read as '                    | o'                   |                        |                    |                 |           |  |  |  |  |

|                 | •                                                                                                                                                     |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                                                                       |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                                                                      | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |  |

|                 | DOJENUS                                                                                                                                               |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |  |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

NOTES:

### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-0                          | U-0                                                                        | U-0                                                                                                                        | U-0                                                              | U-0                  | U-0                       | R/W-0              | R/W-0   |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------|---------------------------|--------------------|---------|

| CHPCLKEN                       | —                                                                          | —                                                                                                                          | —                                                                | —                    | —                         | CHOPC              | LK<9:8> |

| bit 15                         |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    | bit 8   |

|                                |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| R/W-0                          | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0                | R/W-0                     | R/W-0              | R/W-0   |

|                                |                                                                            |                                                                                                                            | CHOPC                                                            | LK<7:0>              |                           |                    |         |

| bit 7                          |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    | bit 0   |

|                                |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| Legend:                        |                                                                            |                                                                                                                            |                                                                  |                      |                           |                    |         |

| R = Readable I                 | bit                                                                        | W = Writable                                                                                                               | bit                                                              | U = Unimplei         | mented bit, read          | as '0'             |         |

| -n = Value at P                | OR                                                                         | '1' = Bit is set                                                                                                           |                                                                  | '0' = Bit is cleared |                           | x = Bit is unknown |         |

| bit 15<br>bit 14-10<br>bit 9-0 | 1 = Chop clos<br>0 = Chop clos<br>Unimplemen<br>CHOPCLK<9<br>The frequence | Enable Chop<br>ck generator is<br>ck generator is<br>ted: Read as '<br>9:0>: Chop Clo<br>y of the chop c<br>ncy = (FP/PCL) | enabled<br>disabled<br>0'<br>ck Divider bits<br>lock signal is g | given by the fo      | ollowing expressi<br>+ 1) | on:                |         |

### REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-----------------|-----------|-------|--|

|                                    |       |                | MDC   | <15:8>                                  |                 |           |       |  |

| bit 15                             |       |                |       |                                         |                 |           | bit 8 |  |

|                                    |       |                |       |                                         |                 |           |       |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |

|                                    |       |                | MD    | C<7:0>                                  |                 |           |       |  |

| bit 7                              |       |                |       |                                         |                 |           | bit 0 |  |

|                                    |       |                |       |                                         |                 |           |       |  |

| Legend:                            |       |                |       |                                         |                 |           |       |  |

| R = Readable                       | bit   | W = Writable b | bit   | U = Unimpler                            | mented bit, rea | ad as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                                                    | ,_, ., ., ., .,                                                                  | -,-,-,                |                  |                  |                 |                 |  |  |  |  |

|---------------|------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|-----------------|--|--|--|--|

| R/W-0         | R-0                                                  | R-0                                                                              | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENn         | TXABTn                                               | TXLARBn                                                                          | TXERRn                | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |  |

| bit 15        |                                                      |                                                                                  |                       |                  |                  |                 | bit 8           |  |  |  |  |

| R/W-0         | R-0                                                  | R-0                                                                              | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                                | TXLARBm <sup>(1)</sup>                                                           | TXERRm <sup>(1)</sup> | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |  |

| bit 7         |                                                      |                                                                                  |                       |                  |                  |                 | bit C           |  |  |  |  |

| Legend:       |                                                      |                                                                                  |                       |                  |                  |                 |                 |  |  |  |  |

| R = Readabl   | le bit                                               | W = Writable                                                                     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value at | t POR                                                | '1' = Bit is set                                                                 |                       | '0' = Bit is cle | ared             | x = Bit is unki | nown            |  |  |  |  |

| bit 15-8      | See Definitio                                        | n for bits<7:0>,                                                                 | Controls Buffe        | <u>er n</u>      |                  |                 |                 |  |  |  |  |

| bit 7         |                                                      |                                                                                  |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | <b>TXENm:</b> TX/RX Buffer Selection bit<br>1 = Buffer TRBn is a transmit buffer |                       |                  |                  |                 |                 |  |  |  |  |

|               | 0 = Buffer TR                                        | RBn is a receive                                                                 | buffer                |                  |                  |                 |                 |  |  |  |  |

| bit 6         | TXABTm: Message Aborted bit <sup>(1)</sup>           |                                                                                  |                       |                  |                  |                 |                 |  |  |  |  |

|               | 1 = Message was aborted                              |                                                                                  |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | completed tran                                                                   |                       |                  |                  |                 |                 |  |  |  |  |

| bit 5         | TXLARBm: Message Lost Arbitration bit <sup>(1)</sup> |                                                                                  |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | lost arbitration did not lose ar                                                 |                       |                  |                  |                 |                 |  |  |  |  |

| bit 4         | TXERRm: Er                                           | <b>TXERRm:</b> Error Detected During Transmission bit <sup>(1)</sup>             |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | or occurred wh<br>or did not occu                                                |                       |                  |                  |                 |                 |  |  |  |  |

| bit 3         |                                                      | essage Send F                                                                    |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | 0                                                                                | •                     | bit automatic    | ally clears wher | n the message   | is successfully |  |  |  |  |

|               | 0 = Clearing                                         | the bit to '0' wh                                                                | nile set reques       | ts a message     | abort            |                 |                 |  |  |  |  |

| bit 2         | RTRENm: Au                                           | uto-Remote Tra                                                                   | Insmit Enable         | bit              |                  |                 |                 |  |  |  |  |

|               |                                                      | emote transmit<br>emote transmit                                                 | •                     |                  |                  |                 |                 |  |  |  |  |

| bit 1-0       | TXmPRI<1:0                                           | >: Message Tra                                                                   | ansmission Pri        | iority bits      |                  |                 |                 |  |  |  |  |

|               | 11 = Highest                                         | message prior                                                                    | ity                   |                  |                  |                 |                 |  |  |  |  |

|               | 0                                                    | ermediate mes                                                                    |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      | ermediate mess<br>message priori                                                 |                       |                  |                  |                 |                 |  |  |  |  |

|               |                                                      |                                                                                  | -                     |                  |                  |                 |                 |  |  |  |  |

| Note 1: ⊤     | his bit is cleared                                   | when TXREQ                                                                       | s set.                |                  |                  |                 |                 |  |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al                                                                                                                              |                                                      | CONTROL REG         |                 |                  |                 |              |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|------------------|-----------------|--------------|--|--|--|

| R/W-0         | R/W-                                                                                                                                  | -0 R/W-0                                             | U-0                 | U-0             | R/W-0            | R/W-0           | R/W-0        |  |  |  |

| VCFG2         | VCFC                                                                                                                                  | G1 VCFG0                                             | —                   | —               | CSCNA            | CHPS1           | CHPS0        |  |  |  |

| bit 15        |                                                                                                                                       |                                                      |                     |                 |                  |                 | bit          |  |  |  |

| R-0           | R/W-                                                                                                                                  | -0 R/W-0                                             | R/W-0               | R/W-0           | R/W-0            | R/W-0           | R/W-0        |  |  |  |

| BUFS          | SMP                                                                                                                                   |                                                      | SMPI2               | SMPI1           | SMPI0            | BUFM            | ALTS         |  |  |  |

| bit 7         | Sivil                                                                                                                                 |                                                      | SIVILIZ             |                 |                  | BOTIM           | bit          |  |  |  |

| Logondi       |                                                                                                                                       |                                                      |                     |                 |                  |                 |              |  |  |  |

| Legend:       | . hit                                                                                                                                 | M = Mritable                                         |                     |                 | montod hit roo   |                 |              |  |  |  |

| R = Readable  |                                                                                                                                       | W = Writable                                         |                     |                 | mented bit, read |                 |              |  |  |  |

| -n = Value at | POR                                                                                                                                   | '1' = Bit is se                                      | et '(               | )' = Bit is cle | eared            | x = Bit is unkr | nown         |  |  |  |

| bit 15-13     | VCFG<2                                                                                                                                | 2:0>: Converter Vol                                  | tage Reference C    | onfiguration    | bits             |                 |              |  |  |  |

|               | Value                                                                                                                                 | VREFH                                                | VREFL               |                 |                  |                 |              |  |  |  |

|               | 000                                                                                                                                   | Avdd                                                 | Avss                |                 |                  |                 |              |  |  |  |

|               | 001                                                                                                                                   | External VREF+                                       | Avss                |                 |                  |                 |              |  |  |  |

|               | 010                                                                                                                                   | Avdd                                                 | External VREF-      |                 |                  |                 |              |  |  |  |

|               | 011                                                                                                                                   | External VREF+                                       | External VREF-      |                 |                  |                 |              |  |  |  |

|               | 1xx                                                                                                                                   | Avdd                                                 | Avss                |                 |                  |                 |              |  |  |  |

| bit 12-11     | Unimple                                                                                                                               | emented: Read as                                     | 'O'                 |                 |                  |                 |              |  |  |  |

| bit 10        | CSCNA: Input Scan Select bit                                                                                                          |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | 1 = Scans inputs for CH0+ during Sample MUXA                                                                                          |                                                      |                     |                 |                  |                 |              |  |  |  |

|               |                                                                                                                                       | s not scan inputs                                    | 5 1                 |                 |                  |                 |              |  |  |  |

| bit 9-8       | CHPS<1:0>: Channel Select bits                                                                                                        |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':                                                 |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | 1x = Converts CH0, CH1, CH2 and CH3                                                                                                   |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | 01 = Converts CH0 and CH1<br>00 = Converts CH0                                                                                        |                                                      |                     |                 |                  |                 |              |  |  |  |

| L:1 7         |                                                                                                                                       |                                                      |                     |                 |                  |                 |              |  |  |  |

| bit 7         |                                                                                                                                       | Buffer Fill Status bit                               |                     | -               | o ucor opplicat  | ion chould coor | oo data in t |  |  |  |

|               | 1 = ADC is currently filling the second half of the buffer; the user application should access data in th<br>first half of the buffer |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | 0 = ADC is currently filling the first half of the buffer; the user application should access data in the                             |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | second half of the buffer                                                                                                             |                                                      |                     |                 |                  |                 |              |  |  |  |

| bit 6-2       | SMPI<4                                                                                                                                | :0>: Increment Rat                                   | e bits              |                 |                  |                 |              |  |  |  |

|               | When ADDMAEN = 0:                                                                                                                     |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | x1111 = Generates interrupt after completion of every 16th sample/conversion operation                                                |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | x1110 = Generates interrupt after completion of every 15th sample/conversion operation                                                |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | •                                                                                                                                     |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | •                                                                                                                                     |                                                      |                     |                 |                  |                 |              |  |  |  |

|               |                                                                                                                                       | Generates interru                                    |                     |                 |                  |                 | n            |  |  |  |

|               |                                                                                                                                       | <ul> <li>Generates interru</li> </ul>                | pt after completior | of every sa     | ample/conversion | n operation     |              |  |  |  |

|               |                                                                                                                                       | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 11 address offer a  | omplation of    | four 20rd of     | male (conversi  | on onoratio  |  |  |  |

|               |                                                                                                                                       | Increments the DI<br>Increments the DI               |                     |                 |                  |                 |              |  |  |  |

|               | •                                                                                                                                     |                                                      |                     | Simpletion      | n every orac sa  |                 |              |  |  |  |

|               |                                                                                                                                       |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | •                                                                                                                                     |                                                      |                     |                 |                  |                 |              |  |  |  |

|               | •                                                                                                                                     | - Increments the DI                                  |                     |                 |                  |                 |              |  |  |  |

#### . . ACOND. ADCA CONTROL DECISTED 2

### 24.3 PTG Control Registers

### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0        | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |  |

|--------------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|--|

| PTGEN        | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |  |

| bit 15 bit 8 |         |         |         |     |                       |                        |                        |  |

|              |         |         |         |     |                       |                        |                        |  |

| R/W-0        | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/W-0                  |                        |  |

| PTGSTRT      | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |  |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  |       | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |       | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |       | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |       | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |       | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |       | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |       | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |       | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |       | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |       | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |       | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |       | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |       | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |       | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |       | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |       | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |       | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |       | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |       | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |