#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:( | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | —           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | _      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |  |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|------------|-------|--------|-------|-------|---------------|--|

| RPOR0        | 0680  |        |        |        | RP35R<5:0> |        |        |       |       | _     | —     |            | RP20R<5:0> |       |        |       |       |               |  |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       |       | _     |            |            | RP36F | <5:0>  |       |       | 0000          |  |

| RPOR2        | 0684  | _      | _      |        |            | RP39   | R<5:0> |       |       | _     | _     |            |            | RP38F | <5:0>  |       |       | 0000          |  |

| RPOR3        | 0686  | _      | _      |        |            | RP41   | R<5:0> |       |       | _     | _     |            |            | RP40F | <5:0>  |       |       | 0000          |  |

| RPOR4        | 0688  | _      | _      |        |            | RP43   | R<5:0> |       |       | _     | _     | RP42R<5:0> |            |       |        |       | 0000  |               |  |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0> |        |        |       |       | _     | —     | RP54R<5:0> |            |       |        |       |       | 0000          |  |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       |       | _     | —     |            |            | RP56F | R<5:0> |       |       | 0000          |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0>  |        |        |       |       | _     | _     | RP20R<5:0> |       |       |        |       |       | 0000          |

| RPOR1        | 0682  | _      |        |        | RP37R<5:0>  |        |        |       |       | _     | _     | RP36R<5:0> |       |       |        |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        | RP39R<5:0>  |        |        |       |       | _     | _     |            |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |             | RP41F  | २<5:0> |       |       | _     | _     |            |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | २<5:0> |       |       | —     | _     | RP42R<5:0> |       |       |        |       | 0000  |               |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | २<5:0> |       |       | —     | _     |            |       | RP54  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |             | RP57F  | २<5:0> |       |       | —     | _     |            |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        |       |       | —     | _     | _          | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        | RP118R<5:0> |        |        |       |       | _     | _     | —          | _     | —     | _      | —     | _     | 0000          |

| RPOR9        | 0692  | —      | _      | _      |             |        |        |       | _     | _     | _     |            |       | RP120 | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                           | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                               | _                               | _                     | —                |                  | _               |         |  |  |  |  |  |

| bit 15               |                                                                               |                                 |                       |                  |                  |                 | bit 8   |  |  |  |  |  |

|                      |                                                                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| R/W-0                | R/W-0                                                                         | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                       | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |  |

| bit 7                |                                                                               |                                 |                       |                  |                  |                 | bit     |  |  |  |  |  |

| Legend:              |                                                                               | S = Settable b                  | oit                   |                  |                  |                 |         |  |  |  |  |  |

| R = Readable         | bit                                                                           | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value at F      | POR                                                                           | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|                      |                                                                               |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

| bit 15               | FORCE: Force                                                                  | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |  |

|                      | 1 = Forces a                                                                  | single DMA tra                  | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |  |  |

|                      | 0 = Automati                                                                  | c DMA transfer                  | initiation by D       | DMA request      |                  |                 |         |  |  |  |  |  |

| bit 14-8             | Unimplemen                                                                    | Unimplemented: Read as '0'      |                       |                  |                  |                 |         |  |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>                                                                   | -: DMA Periphe                  | eral IRQ Num          | ber Select bits  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | ECAN1 – TX D                    |                       | 2)               |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC4 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC3 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | ECAN1 – RX D<br>SPI2 Transfer I | -                     |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | UART2TX – UA                    |                       | itter            |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | UART2RX – U                     |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | TMR5 – Timer5                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011011 =                                                                    | TMR4 – Timer4                   | 1                     |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | OC4 – Output (                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                             |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                           |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter<br>00001011 = UART1RX – UART1 Receiver |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | SPI1 – Transfe                  |                       | er               |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | TMR3 – Timer3                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | TMR2 – Timer2                   |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000110 = OC2 – Output Compare 2                                             |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000101 = IC2 – Input Capture 2                                              |                                 |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000010 =                                                                    | OC1 – Output (                  | Compare 1             |                  |                  |                 |         |  |  |  |  |  |

|                      |                                                                               | IC1 – Input Ca                  |                       |                  |                  |                 |         |  |  |  |  |  |

|                      | 00000000 =                                                                    | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

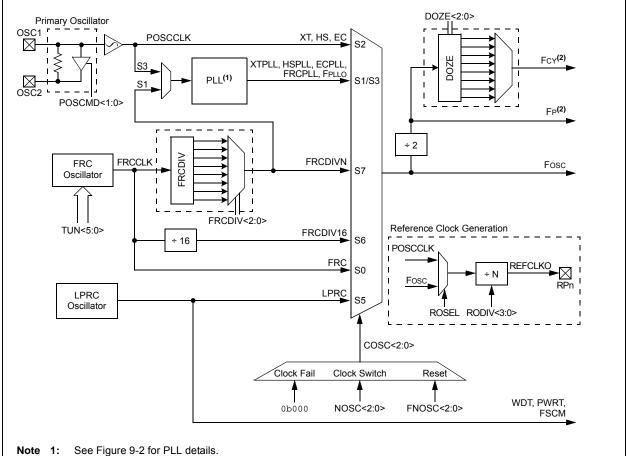

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> AALO                              | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA            | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0             | U-0                               | U-0            | U-0 | U-0          | U-0                                     | U-0                     | U-0         |  |  |  |

|-----------------|-----------------------------------|----------------|-----|--------------|-----------------------------------------|-------------------------|-------------|--|--|--|

| —               | —                                 | —              | _   | —            | —                                       | —                       | _           |  |  |  |

| bit 15          |                                   |                |     |              |                                         |                         | bit 8       |  |  |  |

|                 |                                   |                |     |              |                                         |                         |             |  |  |  |

| U-0             | U-0                               | U-0            | U-0 | U-0          | R/W-0                                   | R/W-0                   | R/W-0       |  |  |  |

| —               | —                                 | —              | _   | —            | PCLKDIV2 <sup>(1)</sup>                 | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |  |  |

| bit 7           |                                   |                |     |              |                                         |                         | bit 0       |  |  |  |

|                 |                                   |                |     |              |                                         |                         |             |  |  |  |

| Legend:         |                                   |                |     |              |                                         |                         |             |  |  |  |

| R = Readable    | bit                               | W = Writable   | bit | U = Unimpler | mented bit, read                        | as '0'                  |             |  |  |  |

| -n = Value at F | n = Value at POR '1' = Bit is set |                |     |              | '0' = Bit is cleared x = Bit is unknown |                         |             |  |  |  |

|                 |                                   |                |     |              |                                         |                         |             |  |  |  |

| bit 15-3        | Unimplemen                        | ted: Read as ' | י'  |              |                                         |                         |             |  |  |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | TRGC  | MP<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | TRGC  | MP<7:0>           |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

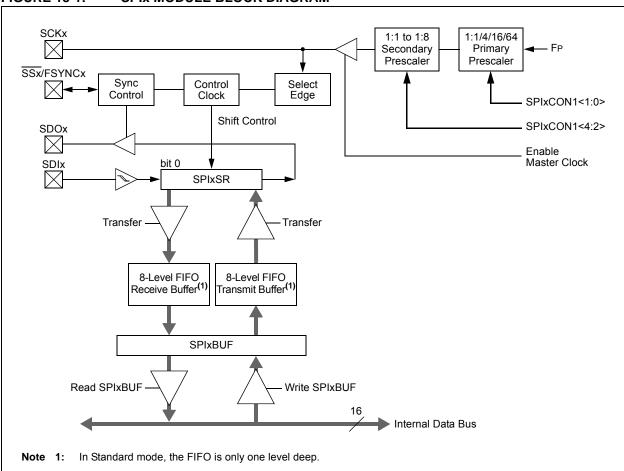

#### FIGURE 18-1: SPIx MODULE BLOCK DIAGRAM

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

## Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

| DC CHARACTERISTICS |                               |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |

|--------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|

| Parameter<br>No.   | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Units Conditions      |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |

| DC60d              | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |

| DC60d              | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |

| DC60c              | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |

| DC60d              | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.57            |  |  |

| DC60c              | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |

| DC60d              | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 250                           | 450           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.5 V           |  |  |

| DC60c              | 1000                          | 1200          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

| Power-Down Cu      | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |

| DC60d              | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |

| DC60a              | 45                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |

| DC60b              | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 V           |  |  |

| DC60c              | 1100                          | 1500          | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |

#### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS |                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                              |                     |                              |        |                                            |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------------------------------|--------|--------------------------------------------|

| Param<br>No.       | Symbol           | Characteristic                                                                                                                                                                                                                                                                                | Min.                         | Тур. <sup>(2)</sup> | Max.                         | Units  | Conditions                                 |

| Op Am              | p DC Chara       | cteristics                                                                                                                                                                                                                                                                                    |                              |                     |                              |        |                                            |

| CM40               | VCMR             | Common-Mode Input<br>Voltage Range                                                                                                                                                                                                                                                            | AVss                         | _                   | AVDD                         | V      |                                            |

| CM41               | CMRR             | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                                                                                                                                                                                                                                                 | —                            | 40                  | —                            | db     | VCM = AVDD/2                               |

| CM42               | VOFFSET          | Op Amp Offset<br>Voltage <sup>(3)</sup>                                                                                                                                                                                                                                                       | —                            | ±5                  | —                            | mV     |                                            |