#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K × 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc202t-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

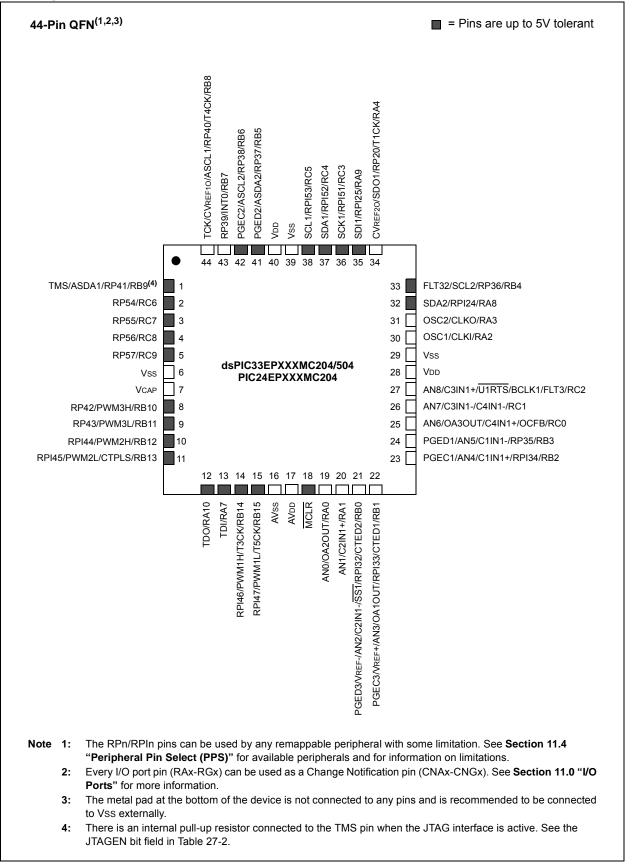

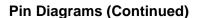

### Pin Diagrams (Continued)

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

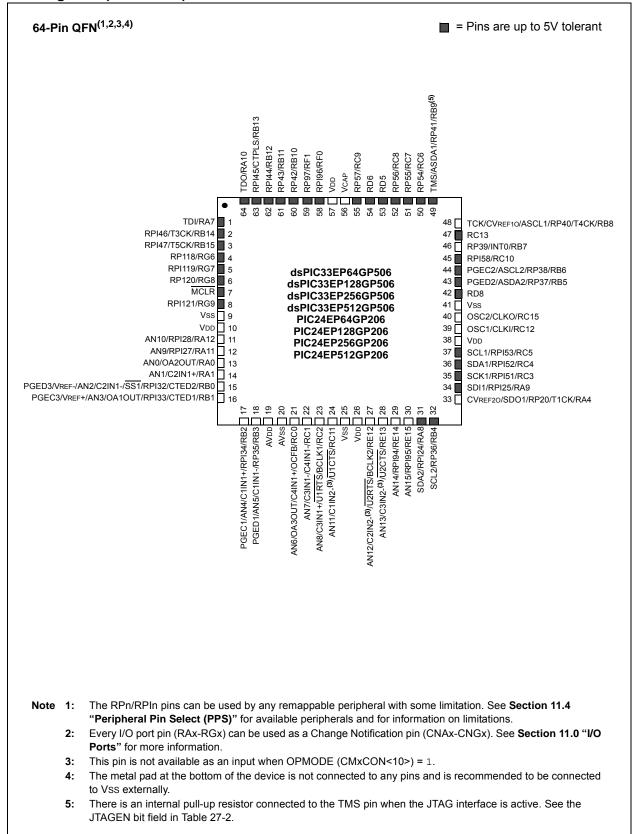

# 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

# **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

### 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| R/W-0         | R/W-0                                                                                                | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD                                                                                                 | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |                                                                                                      |                                                       |         |                   |                       |                      | bit   |

|               |                                                                                                      |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0                                                                                                | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD                                                                                                 | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |                                                                                                      |                                                       |         |                   |                       |                      | bit   |

| Legend:       |                                                                                                      |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit                                                                                                | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR                                                                                                  | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m                                                                                         | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m                                                                                         | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m                                                                                         | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m                                                                                         | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m                                                                                         | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod                                                                                         | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod                                                                                          | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen                                                                                           | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | I2C1MD: I2C1 Module Disable bit<br>1 = I2C1 module is disabled<br>0 = I2C1 module is enabled         |                                                       |         |                   |                       |                      |       |

| bit 6         | <b>U2MD:</b> UART2 Module Disable bit<br>1 = UART2 module is disabled<br>0 = UART2 module is enabled |                                                       |         |                   |                       |                      |       |

| bit 5         | 1 = UART1 m                                                                                          | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod                                                                                         | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

#### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

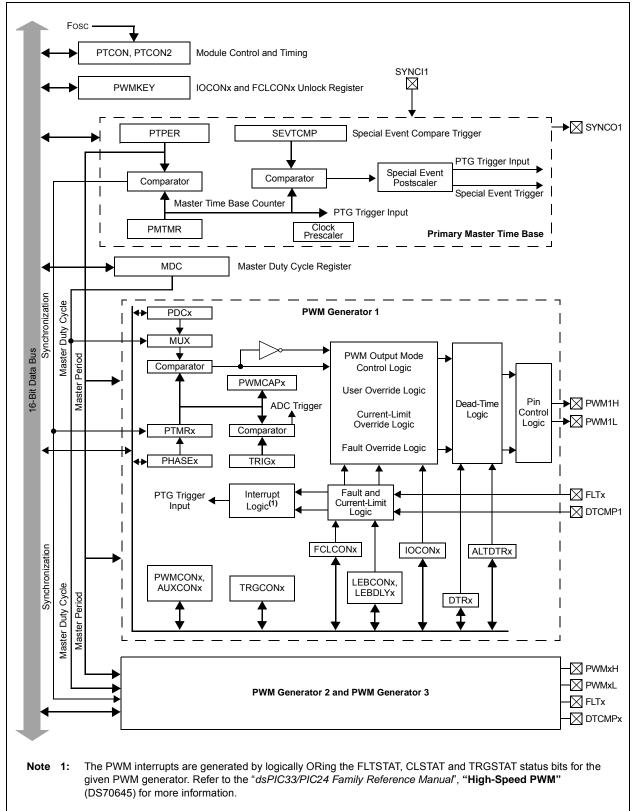

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| U-0       R/W-0       R/W       R/W       R/W </th <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>U-0</th> <th>U-0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0         | R/W-0                                                                                                                                                                                     | R/W-0                             | R/W-0                           | R/W-0                  | R/W-0            | U-0               | U-0   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|------------------------|------------------|-------------------|-------|--|--|

| U-0       U-0       RW-0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHR           | PHF                                                                                                                                                                                       | PLR                               | PLF                             | FLTLEBEN               | CLLEBEN          | —                 |       |  |  |

| -         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPH         BPHL         BPLH         BPHH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15        |                                                                                                                                                                                           |                                   |                                 |                        |                  |                   | bit   |  |  |

| bit 7       t         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input       1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | U-0                                                                                                                                                                                       | R/W-0                             | R/W-0                           | R/W-0                  | R/W-0            | R/W-0             | R/W-0 |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>nn = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PHR: PWMxH Rising Edge Trigger Enable bit<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxH<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Rising edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Leading-Edge Blanking is applied to selected Fault input<br>0 = Leading-Edge Blanking is applied to selected Fault input<br>1 = Leading-Edge Blanking is applied to selected Current-limit input<br>1 = Leading-Edge Blanking is not applied to selected current-limit input<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low<br>0 = No blanking when selected blanking signal Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low<br>0 = No blanking when PWMxH dupt is high<br>0 = No blanking when PWMxH dupt signals) when PWMxH output is high<br>0 = No blanking when PWMxH tow Enable bit<br>1 = State blanking (of current-limit and/ | _             | _                                                                                                                                                                                         | BCH <sup>(1)</sup>                | BCL <sup>(1)</sup>              | BPHH                   | BPHL             | BPLH              | BPLL  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 13       PLR: PWMxL Falling Edge Trigger Enable bit       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 9-6       Unimplemented: Read as '0'       1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking signal is high       1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                                                                                                                                                                           |                                   |                                 |                        |                  |                   | bit   |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH       11 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH       11 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores fising edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input       0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking signal Figh Enable bit         1 = State blanking in Selected Blanking Singal High Enable bit <sup>(1)</sup> 1 = State blanking in Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:       |                                                                                                                                                                                           |                                   |                                 |                        |                  |                   |       |  |  |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ol> <li>Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readabl   | e bit                                                                                                                                                                                     | W = Writable                      | bit                             | U = Unimpler           | mented bit, read | as '0'            |       |  |  |

| <ul> <li>1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxH</li> <li>PHF: PWMxH Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>PLR: PVMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>Det Leading-Edge Blanking ignores ralling edge of PWMxL</li> <li>D = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = Leading-Edge Blanking Signal Liph Enable bit<sup>(1)</sup></li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No b</li></ul>                                                                                                                                                                | -n = Value at | POR                                                                                                                                                                                       | '1' = Bit is set                  | :                               | '0' = Bit is cle       | ared             | x = Bit is unkr   | nown  |  |  |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 FLTLEBEN: Fault Input Leading-Edge Blanking Counter</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is nigh</li> <li>0 = No bla</li></ul>                                                                                                                                                                 | bit 15        | 1 = Rising ed                                                                                                                                                                             | ge of PWMxH                       | will trigger Le                 | ading-Edge Bla         |                  |                   |       |  |  |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>pLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11</li> <li>FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking when selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH dutput is high</li> <li>0 = No blanking when PWMxH Low Enable bit</li> <li>1 = State blanking (of</li></ul>                                                                                                                                                         | bit 14        | 1 = Falling ed                                                                                                                                                                            | lge of PWMxH                      | will trigger Le                 | eading-Edge Bla        | 0                |                   |       |  |  |

| bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = No blanking when selected Blanking signal Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         0 = No blanking when P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 13        | 1 = Rising ed                                                                                                                                                                             | ge of PWMxL                       | will trigger Le                 | ading-Edge Bla         |                  |                   |       |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li></ul>                                                                                                                                                                 | bit 12        | 1 = Falling ed                                                                                                                                                                            | lge of PWMxL                      | will trigger Le                 | ading-Edge Bla         |                  |                   |       |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>bit 5</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>bit 4</li> <li>BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Ligh Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL output is high</li> </ul>                                                                                                                                                                                                 | bit 11        | 1 = Leading-E                                                                                                                                                                             | Edge Blanking                     | is applied to                   | selected Fault in      | nput             |                   |       |  |  |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       State blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxL output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 10        | 1 = Leading-E                                                                                                                                                                             | Edge Blanking                     | is applied to                   | selected current       | t-limit input    |                   |       |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 9-6       | Unimplemen                                                                                                                                                                                |                                   |                                 |                        |                  |                   |       |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>BPHH: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 5         | <b>BCH:</b> Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup><br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high |                                   |                                 |                        |                  |                   |       |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 4         | <b>BCL:</b> Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup><br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low   |                                   |                                 |                        |                  |                   |       |  |  |

| 1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3         | <b>BPHH:</b> Blanking in PWMxH High Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high                                              |                                   |                                 |                        |                  |                   |       |  |  |

| bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 2         | <b>BPHL:</b> Blanking in PWMxH Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low                                                |                                   |                                 |                        |                  |                   |       |  |  |

| bit 0 <b>BPLL:</b> Blanking in PWMxL Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1         | <b>BPLH:</b> Blanking in PWMxL High Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high                                              |                                   |                                 |                        |                  |                   |       |  |  |

| $\sim$ i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 0         | <b>BPLL:</b> Blanki<br>1 = State blar                                                                                                                                                     | ng in PWMxL I<br>hking (of currer | Low Enable b<br>nt-limit and/or | it<br>Fault input sigr | nals) when PWN   | /IxL output is lo | w     |  |  |

### REGISTER 16-16: LEBCONX: PWMx LEADING-EDGE BLANKING CONTROL REGISTER

Note 1: The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

| R-0                                                                  | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|----------------------------------------------------------------------|------------------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                      |                  | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| R-0                                                                  | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |

|                                                                      |                  | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

|                                                                      |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| t = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |

| OR                                                                   | '1' = Bit is set |                              | '0' = Bit is cleared x = Bit is unknown            |                                                                                                |                                                                                           |                                                                                                                      |