Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 32KB (10.7K × 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc203t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

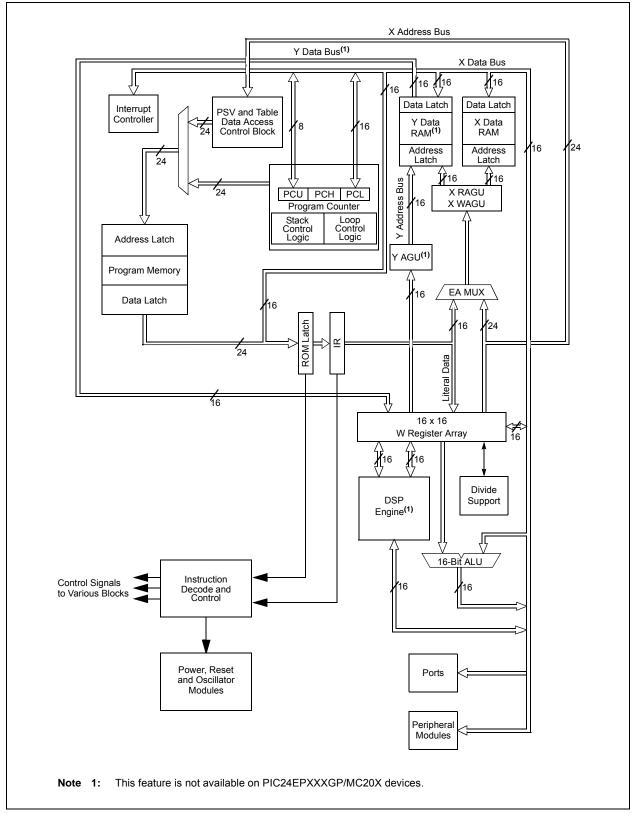

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

## TABLE 4-20: ADC1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8        | Bit 7    | Bit 6    | Bit 5    | Bit 4     | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|-----------|--------|---------|--------|-----------|---------|--------------|----------|----------|----------|-----------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 0  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 1  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 2  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 3  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 4  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF5  | 030A  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 5  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF6  | 030C  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 6  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 7  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 8  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312  |        |           |        |         |        |           |         | ADC1 Data B  | uffer 9  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314  |        |           |        |         |        |           |         | ADC1 Data Bu | Iffer 10 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |           |        |         |        |           |         | ADC1 Data Bu | uffer 11 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |           |        |         |        |           |         | ADC1 Data Bu | Iffer 12 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |           |        |         |        |           |         | ADC1 Data Bu | Iffer 13 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |           |        |         |        |           |         | ADC1 Data Bu | Iffer 14 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |           |        |         |        |           |         | ADC1 Data Bu | iffer 15 |          |          |           |        |          |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>       | Ś        | SRC<2:0> | <b>`</b> | SSRCG     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  | ١      | VCFG<2:0> | >      | _       | _      | CSCNA     | CHP     | S<1:0>       | BUFS     |          |          | SMPI<4:0> | >      |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _         | _      |         |        | SAMC<4:03 | >       |              |          |          |          | ADCS      | <7:0>  |          |         |         | 0000          |

| AD1CHS123 | 0326  | _      | _         | _      | _       | _      | CH123N    | NB<1:0> | CH123SB      | —        | _        | —        | _         | _      | CH123N   | A<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | _         | _      |         |        | CH0SB<4:0 | >       |              | CH0NA    | _        | —        |           | С      | H0SA<4:0 | >       |         | 0000          |

| AD1CSSH   | 032E  | CSS31  | CSS30     | _      | _       |        | CSS26     | CSS25   | CSS24        | _        |          | _        | —         | _      | —        | —       | —       | 0000          |

| AD1CSSL   | 0330  | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8         | CSS7     | CSS6     | CSS5     | CSS4      | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

| AD1CON4   | 0332  |        | _         | _      | _       |        | _         | _       | ADDMAEN      | -        |          |          |           | _      | D        | MABL<2: | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12                    | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|---------------------------|--------|--------|-------|-------|-------|------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | _      |        |                           | RP35   | R<5:0> |       |       | _     | —          |            |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |                           | RP37   | R<5:0> |       |       |       | —          |            |       | RP36F | <5:0>  |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> — — RP38R<5:0> |        |        |       |       | 0000  |            |            |       |       |        |       |       |               |

| RPOR3        | 0686  | _      | _      |        |                           | RP41   | R<5:0> |       |       |       | —          | RP40R<5:0> |       |       |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        |                           | RP43   | R<5:0> |       |       |       | —          | RP42R<5:0> |       |       |        |       | 0000  |               |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0>                |        |        |       | _     | —     | RP54R<5:0> |            |       |       |        | 0000  |       |               |

| RPOR6        | 068C  | _      | —      |        |                           | RP57   | R<5:0> |       |       | _     | —          |            |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |        | RP35F  | R<5:0> |       |       | _     | _     |       | •     | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      |        |        |        | RP37F  | R<5:0> |       |       | _     | _     |       |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        |        | RP39F  | २<5:0> |       |       | _     | _     |       |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |        | RP41F  | २<5:0> |       |       | _     | _     |       |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F  | २<5:0> |       |       | —     | _     |       |       | RP42  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |        | RP55F  | २<5:0> |       |       | —     | _     |       |       | RP54  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |        | RP57F  | २<5:0> |       |       | —     | _     |       |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        |        | RP97F  | २<5:0> |       |       | —     | _     | _     | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        |        | RP118  | R<5:0> |       |       | _     | _     | —     | _     | —     | _      | —     | _     | 0000          |

| RPOR9        | 0692  | —      | _      | _      | _      | _      | _      | _     | _     | _     | _     |       |       | RP120 | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |

|-------|--------------------------------------------|

|       | word-sized data (LSb of every EA is always |

|       | clear). The XBREVx value is scaled         |

|       | accordingly to generate compatible (byte)  |

|       | addresses.                                 |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

| R/W-0                 | R/W-0                                             | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |  |  |  |  |  |

|-----------------------|---------------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|--|--|--|--|--|

| CHEN                  | SIZE                                              | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |  |  |  |  |  |

| bit 15                |                                                   |                                                      |                                               |                                    |                  |                 | bit     |  |  |  |  |  |

| U-0                   | U-0                                               | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |  |  |  |  |  |

|                       | 0-0                                               | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |  |  |  |  |  |

| bit 7                 |                                                   | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |  |  |  |  |  |

| Lovende               |                                                   |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |  |

| Legend:<br>R = Readab | lo hit                                            | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |  |  |  |  |  |

|                       |                                                   | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |  |  |  |  |  |

| -n = Value a          | IT POR                                            | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15                | CHEN: DMA                                         | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |  |  |  |  |  |

|                       | 1 = Channel<br>0 = Channel                        |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |  |

| bit 14                |                                                   | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |         |  |  |  |  |  |

|                       | 1 = Byte                                          |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |  |

|                       | 0 = Word                                          |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |  |

| bit 13                | DIR: DMA Tra                                      | ansfer Directior                                     | n bit (source/d                               | estination bus                     | select)          |                 |         |  |  |  |  |  |

|                       |                                                   | om RAM addre<br>om peripheral a                      |                                               | •                                  |                  |                 |         |  |  |  |  |  |

| bit 12                |                                                   | Block Transfer                                       |                                               |                                    |                  |                 |         |  |  |  |  |  |

|                       | 1 = Initiates i                                   | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |  |  |  |  |  |

| bit 11                |                                                   | Data Periphera                                       |                                               |                                    |                  |                 |         |  |  |  |  |  |

|                       |                                                   | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |  |  |  |  |  |

| bit 10-6              | Unimplemen                                        | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |  |  |  |  |  |

| bit 5-4               | AMODE<1:0                                         | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |         |  |  |  |  |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register     |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |  |  |  |  |  |

| bit 3-2               | Unimplemen                                        | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |  |  |  |  |  |

| bit 1-0               | MODE<1:0>: DMA Channel Operating Mode Select bits |                                                      |                                               |                                    |                  |                 |         |  |  |  |  |  |

|                       | 11 = One-Sho<br>10 = Continue                     | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |  |  |  |  |  |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                                                                               | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |  |

|--------------|----------------------|-----------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| U-0          | U-0                  | U-0                                                                                                       | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            |                      | —                                                                                                         |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |

| bit 15       |                      |                                                                                                           |                 |                   |                 |                 | bit   |  |  |  |  |  |

| U-0          | U-0                  | U-0                                                                                                       | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                      |                                                                                                           |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |

| bit 7        |                      |                                                                                                           |                 |                   |                 |                 | bit   |  |  |  |  |  |

|              |                      |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| Legend:      | 1.1.1                |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   |                      | W = Writable b                                                                                            | Dit             | •                 | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value a | at POR               | '1' = Bit is set                                                                                          |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                                                                           | ,               |                   |                 |                 |       |  |  |  |  |  |

| bit 11       | -                    | t Capture 4 Mod                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                    | ture 4 module is                                                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 0 = Input Cap        | oture 4 module is                                                                                         | s enabled       |                   |                 |                 |       |  |  |  |  |  |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                                                                           | ule Disable bit |                   |                 |                 |       |  |  |  |  |  |

|              |                      | <ul> <li>1 = Input Capture 3 module is disabled</li> <li>0 = Input Capture 3 module is enabled</li> </ul> |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                      |                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 9        |                      | t Capture 2 Mod                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                      | oture 2 module is<br>oture 2 module is                                                                    |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                                                                           | ule Disable bit |                   |                 |                 |       |  |  |  |  |  |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is                                                                    | s disabled      |                   |                 |                 |       |  |  |  |  |  |

| bit 7-4      |                      | ted: Read as '0                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | OC4MD: Out           | put Compare 4                                                                                             | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |

|              |                      | ompare 4 modul                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|              | -                    | ompare 4 modu                                                                                             |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 2        |                      | put Compare 3                                                                                             |                 | e bit             |                 |                 |       |  |  |  |  |  |

|              | •                    | ompare 3 modul                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| L:1 4        | -                    | ompare 3 modul                                                                                            |                 | . h.:4            |                 |                 |       |  |  |  |  |  |

| bit 1        |                      | put Compare 2                                                                                             |                 |                   |                 |                 |       |  |  |  |  |  |

|              | $\perp$ – Output Co  | ompare 2 modu                                                                                             |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 0 = Output Co        | ompare 2 modul                                                                                            | le is enabled   |                   |                 |                 |       |  |  |  |  |  |

| bit 0        | •                    | ompare 2 modul<br>put Compare 1                                                                           |                 | e bit             |                 |                 |       |  |  |  |  |  |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                                                       | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |

#### ~

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0               | U-0                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                    | R/W-0                              | U-0                                              | R/W-0            | R/W-0                     |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|--------------------------------------------------|------------------|---------------------------|

| UARTEN <sup>(</sup> | <sup>1)</sup>                                                       | USIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IREN <sup>(2)</sup>                                      | RTSMD                              | _                                                | UEN1             | UEN0                      |

| bit 15              |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | •                                  |                                                  |                  | bit 8                     |

|                     |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>D</b> AMA                                             | <b>D</b> 444 0                     | <b>D</b> 444 0                                   | <b>D</b> 444.0   | <b>D</b> 444 0            |

| R/W-0, H0           |                                                                     | R/W-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                    | R/W-0                              | R/W-0                                            | R/W-0            | R/W-0                     |

| WAKE                | LPBACK                                                              | ABAUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | URXINV                                                   | BRGH                               | PDSEL1                                           | PDSEL0           | STSEL                     |

| bit 7               |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                                    |                                                  |                  | bit                       |

| Legend:             |                                                                     | HC = Hardwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e Clearable b                                            | it                                 |                                                  |                  |                           |

| R = Reada           | ble bit                                                             | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oit                                                      | U = Unimplem                       | ented bit, read                                  | as '0'           |                           |

| -n = Value          | at POR                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | '0' = Bit is clea                  | ared                                             | x = Bit is unkn  | iown                      |

| bit 15              | 1 = UARTx is                                                        | ARTx Enable bit <sup>(</sup><br>s enabled; all UA<br>s disabled; all UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ARTx pins are                                            |                                    |                                                  |                  |                           |

| bit 14              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |

| bit 13              | USIDL: UAR                                                          | Tx Stop in Idle M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lode bit                                                 |                                    |                                                  |                  |                           |

|                     |                                                                     | nues module opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |                                    | le mode                                          |                  |                           |

| bit 12              | 1 = IrDA enc                                                        | Encoder and De<br>oder and decod<br>oder and decod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | er are enable                                            | d                                  |                                                  |                  |                           |

| bit 11              | $1 = \overline{\text{UxRTS}} p$                                     | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mode                                                     | t                                  |                                                  |                  |                           |

| bit 10              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |

| bit 9-8             | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                        | IARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | nd used <sup>(4)</sup><br>UxCT <u>S pin is</u> c | controlled by PC | ORT latches <sup>(4</sup> |

| bit 7               | WAKE: Wake                                                          | e-up on Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Detect During                                            | Sleep Mode Ei                      | nable bit                                        |                  |                           |

|                     | in hardwa                                                           | ontinues to sam<br>are on the follow<br>-up is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |                                    | generated on t                                   | the falling edge | ; bit is cleare           |

| bit 6               | 1 = Enables                                                         | ARTx Loopback<br>Loopback mode<br>k mode is disab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | :                                                        | bit                                |                                                  |                  |                           |

| 2:                  | Refer to the " <b>UAI</b><br>enabling the UAR<br>This feature is or | Tx module for realized and the second s | eceive or trans<br>the 16x BRG                           | mit operation.<br>mode (BRGH =     | -                                                | ce Manual" for i | nformation or             |

|                     | This feature is or                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                        | -                                  |                                                  |                  |                           |

| A-                  | This fastura is ar                                                  | ny available on l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | al nin dovicos                                           |                                    |                                                  |                  |                           |

4: This feature is only available on 64-pin devices.

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |