Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc204-h-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

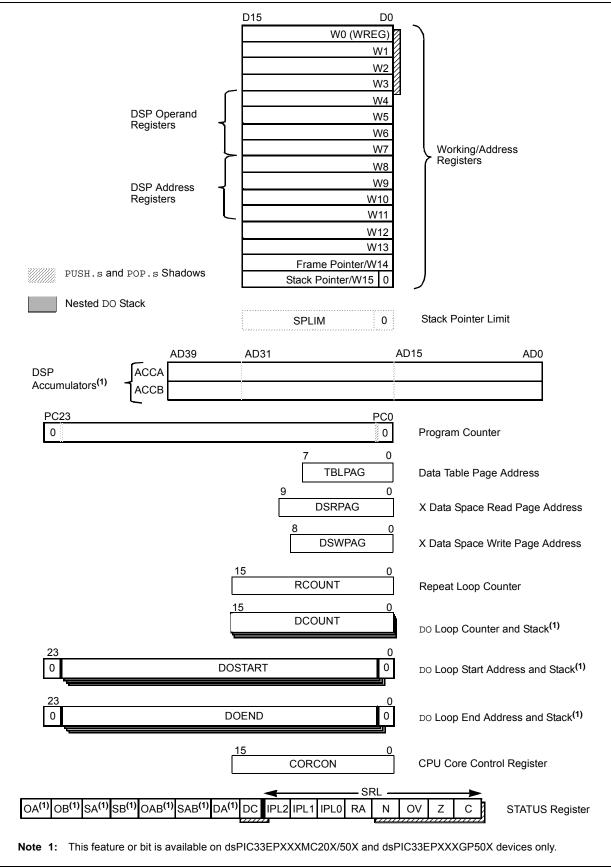

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

## TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | —     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | _      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

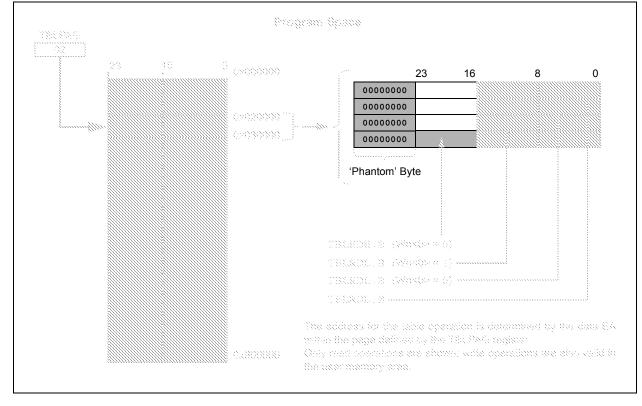

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

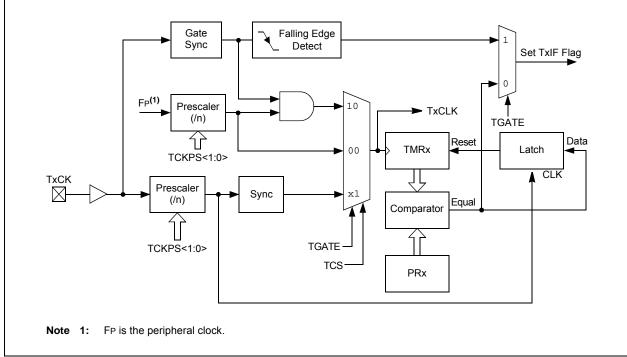

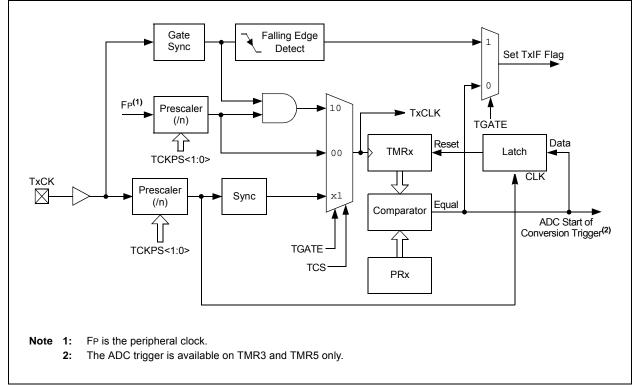

#### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

## FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

#### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |  |  |  |

|-------------------|-----------------------------|-----------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-----------------|-------|------------------|-----------------------------------------|------------------------------------|-------|-------|-------|--|--|--|

| —               | —     |                  | DTRx<13:8>                              |                                    |       |       |       |  |  |  |

| bit 15          |       |                  | bit                                     |                                    |       |       |       |  |  |  |

|                 |       |                  |                                         |                                    |       |       |       |  |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                 |       |                  | DTR                                     | x<7:0>                             |       |       |       |  |  |  |

| bit 7           |       |                  |                                         |                                    |       |       | bit 0 |  |  |  |

|                 |       |                  |                                         |                                    |       |       |       |  |  |  |

| Legend:         |       |                  |                                         |                                    |       |       |       |  |  |  |

| R = Readable    | bit   | W = Writable b   | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |  |  |

## REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0                                                                  | R/W-0            | R/W-0         | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|---------------|-----------------------------------------|-------|-------|-------|--|--|--|

| _               | _                                                                    |                  | ALTDTRx<13:8> |                                         |       |       |       |  |  |  |

| bit 15          |                                                                      |                  |               |                                         |       |       | bit 8 |  |  |  |

|                 |                                                                      |                  |               |                                         |       |       |       |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0         | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                 |                                                                      |                  | ALTDT         | Rx<7:0>                                 |       |       |       |  |  |  |

| bit 7           |                                                                      |                  |               |                                         |       |       | bit 0 |  |  |  |

| Legend:         |                                                                      |                  |               |                                         |       |       |       |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |               |                                         |       |       |       |  |  |  |

| -n = Value at P | OR                                                                   | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | W = Writable bit U = Unimplemented bit, read as '0'            |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                            |                    |  |  |

|-------------------|----------------------------------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, rea | ad as '0'          |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared       | x = Bit is unknown |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| Bit Field             | Description                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDTPRE                | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                         |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         |

| WDTWIN<1:0>           | Watchdog Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period |

| ALTI2C1               | Alternate I2C1 pin<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                  |

| ALTI2C2               | Alternate I2C2 pin<br>1 = I2C2 is mapped to the SDA2/SCL2 pins<br>0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                  |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                |

| ICS<1:0>              | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use       |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  |                 |                                                  | Wn = decimal adjust Wn                      |               | 1                             | С                        |

| 26                 | DEC                  | DEC             | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC             | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC             | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2            | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2            | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2            | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI            | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                 | DIV                  | DIV.S           | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.SD          | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.U           | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.UD          | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF            | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                 | DO                   | DO              | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                    |                      | DO              | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                 | ED                   | ED              | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC            | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH            | Wns,Wnd                                          | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                 | FBCL                 | FBCL            | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                 | FF1L                 | FF1L            | Ws,Wnd                                           | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                 | FF1R                 | FF1R            | Ws,Wnd                                           | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                 | GOTO                 | GOTO            | Expr                                             | Go to address                               | 2             | 4                             | None                     |

|                    |                      | GOTO            | Wn                                               | Go to indirect                              | 1             | 4                             | None                     |

|                    |                      | GOTO.L          | Wn                                               | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                 | INC                  | INC             | f                                                | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC             | f,WREG                                           | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC             | Ws,Wd                                            | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2            | f                                                | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2            | f,WREG                                           | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2            | Ws,Wd                                            | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR             | f                                                | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | f,WREG                                           | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | #lit10,Wn                                        | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                 | LAC                  | LAC             | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK             | #lit14                                           | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                 | LSR                  | LSR             | f                                                | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | f,WREG                                           | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | LSR             | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                 | MAC                  | MAC             | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd(1)                       | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

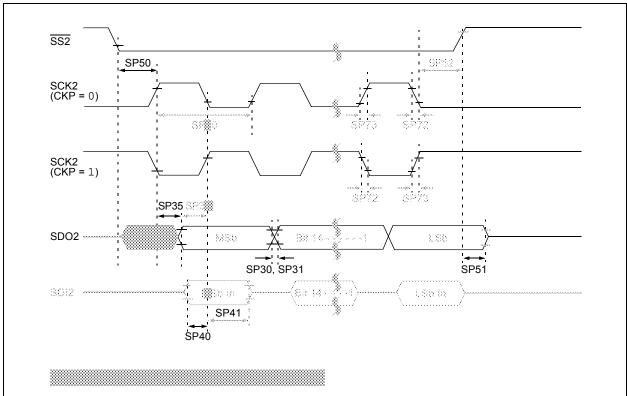

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-40:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extende} \end{array}$ |                     |      |       |                                |

|--------------------|-----------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                 | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                    | —                                                                                                                                                                                                                                                                                    | —                   | 11   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK2 Input Fall Time                            | —                                                                                                                                                                                                                                                                                    | —                   | _    | ns    | See Parameter DO32 (Note 4)    |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                                                                                                                                                                                                                                                                    | —                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | —                                                                                                                                                                                                                                                                                    | _                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                                                                                                                                                                                                                                                    | _                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                                                                                                                                                                                                                                                    | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                                                                                                                                                                                                                                                   | —                   | _    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                                                                                                                                                                                                                                                   | —                   | _    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                                                                                                                                                                                                                                                   | —                   | _    | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                                                                                                                                                                                                                                                  | —                   | _    | ns    |                                |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                                                                                                                                                                                                                                                   | —                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                                                                                                                                                                                                                                                         | —                   |      | ns    | (Note 4)                       |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

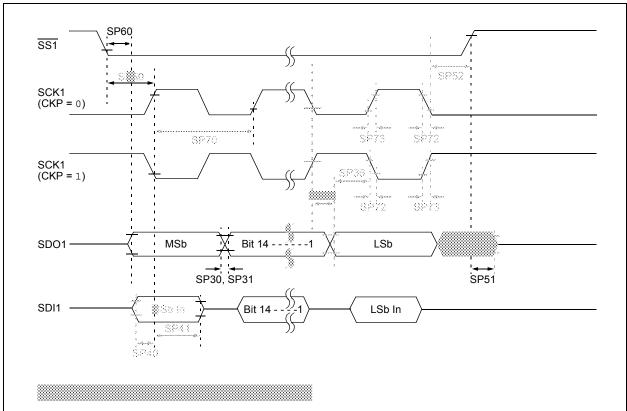

#### FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

|              |        |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |           |      |                                                         |

|--------------|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------|---------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                | Min. Typ. Max. Units                                                                                                                                                                                                                                                                          |          |           |      | Conditions                                              |

|              |        | ADC A                                         | ccuracy (                                                                                                                                                                                                                                                                                     | 10-Bit N | lode)     |      |                                                         |

| AD20b        | Nr     | Resolution                                    | 10                                                                                                                                                                                                                                                                                            | ) Data B | its       | bits |                                                         |

| AD21b        | INL    | Integral Nonlinearity                         | -0.625                                                                                                                                                                                                                                                                                        |          | 0.625     | LSb  | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|              |        |                                               | -1.5                                                                                                                                                                                                                                                                                          |          | 1.5       | LSb  | +85°C < TA ≤ +125°C (Note 2)                            |

| AD22b        | DNL    | Differential Nonlinearity                     | -0.25                                                                                                                                                                                                                                                                                         | —        | 0.25      | LSb  | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|              |        |                                               | -0.25                                                                                                                                                                                                                                                                                         | —        | 0.25      | LSb  | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD23b        | Gerr   | Gain Error                                    | -2.5                                                                                                                                                                                                                                                                                          | —        | 2.5       | LSb  | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                   |

|              |        |                                               | -2.5                                                                                                                                                                                                                                                                                          |          | 2.5       | LSb  | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD24b        | EOFF   | Offset Error                                  | -1.25                                                                                                                                                                                                                                                                                         | —        | 1.25      | LSb  | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$ |

|              |        |                                               | -1.25                                                                                                                                                                                                                                                                                         | —        | 1.25      | LSb  | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD25b        | —      | Monotonicity                                  | _                                                                                                                                                                                                                                                                                             |          | _         | —    | Guaranteed                                              |

|              |        | Dynamic P                                     | erforman                                                                                                                                                                                                                                                                                      | ce (10-E | Bit Mode) |      |                                                         |

| AD30b        | THD    | Total Harmonic Distortion <sup>(3)</sup>      | _                                                                                                                                                                                                                                                                                             | 64       |           | dB   |                                                         |

| AD31b        | SINAD  | Signal to Noise and Distortion <sup>(3)</sup> |                                                                                                                                                                                                                                                                                               | 57       |           | dB   |                                                         |

| AD32b        | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup> | —                                                                                                                                                                                                                                                                                             | 72       | —         | dB   |                                                         |

| AD33b        | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>         |                                                                                                                                                                                                                                                                                               | 550      | —         | kHz  |                                                         |

| AD34b        | ENOB   | Effective Number of Bits <sup>(3)</sup>       | _                                                                                                                                                                                                                                                                                             | 9.4      | —         | bits |                                                         |

#### TABLE 30-59: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

**3:** Parameters are characterized but not tested in manufacturing.

## Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section Name                                   | Update Description                                                                              |

|------------------------------------------------|-------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal | The following 512-Kbyte devices were added to the General Purpose Families table (see Table 1): |

| Controllers (up to                             | <ul> <li>PIC24EP512GP202</li> </ul>                                                             |

| 512-Kbyte Flash and                            | • PIC24EP512GP204                                                                               |

| 48-Kbyte SRAM) with High-                      | • PIC24EP512GP206                                                                               |

| Speed PWM, Op amps, and Advanced Analog"       | • dsPIC33EP512GP502                                                                             |

| Advanced Analog                                | • dsPIC33EP512GP504                                                                             |

|                                                | • dsPIC33EP512GP506                                                                             |

|                                                | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |

|                                                | • PIC24EP512MC202                                                                               |

|                                                | • PIC24EP512MC204                                                                               |

|                                                | • PIC24EP512MC206                                                                               |

|                                                | • dsPIC33EP512MC202                                                                             |

|                                                | • dsPIC33EP512MC204                                                                             |

|                                                | • dsPIC33EP512MC206                                                                             |

|                                                | • dsPIC33EP512MC502                                                                             |

|                                                | • dsPIC33EP512MC504                                                                             |

|                                                | • dsPIC33EP512MC506                                                                             |

|                                                | Certain Pin Diagrams were updated to include the new 512-Kbyte devices.                         |

| Section 4.0 "Memory                            | Added a Program Memory Map for the new 512-Kbyte devices (see Figure 4-4).                      |

| Organization"                                  | Added a Data Memory Map for the new dsPIC 512-Kbyte devices (see Figure 4-11).                  |

|                                                | Added a Data Memory Map for the new PIC24 512-Kbyte devices (see Figure 4-16).                  |

| Section 7.0 "Interrupt<br>Controller"          | Updated the VECNUM bits in the INTTREG register (see Register 7-7).                             |

| Section 11.0 "I/O Ports"                       | Added tip 6 to Section 11.5 "I/O Helpful Tips".                                                 |

| Section 27.0 "Special<br>Features"             | The following modifications were made to the Configuration Byte Register Map (see Table 27-1):  |

|                                                | <ul> <li>Added the column Device Memory Size (Kbytes)</li> </ul>                                |

|                                                | Removed Notes 1 through 4                                                                       |

|                                                | Added addresses for the new 512-Kbyte devices                                                   |

| Section 30.0 "Electrical                       | Updated the Minimum value for Parameter DC10 (see Table 30-4).                                  |

| Characteristics"                               | Added Power-Down Current (Ipd) parameters for the new 512-Kbyte devices (see Table 30-8).       |

|                                                | Updated the Minimum value for Parameter CM34 (see Table 30-53).                                 |

|                                                | Updated the Minimum and Maximum values and the Conditions for paramteer SY12 (see Table 30-22). |

## INDEX

#### Α

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                            |

| 10-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                            |

| 12-Bit ADC Conversion Requirements 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                            |

| ADC Module45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                            |