Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc204-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

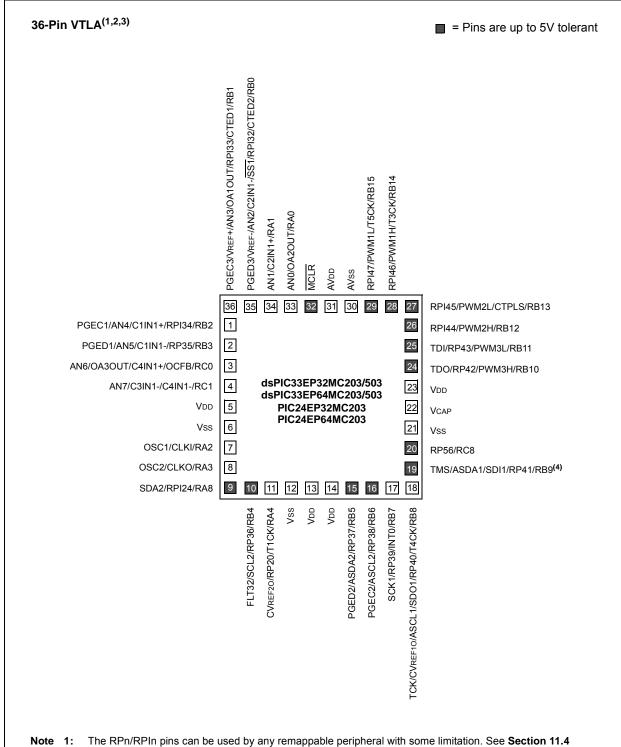

# Pin Diagrams (Continued)

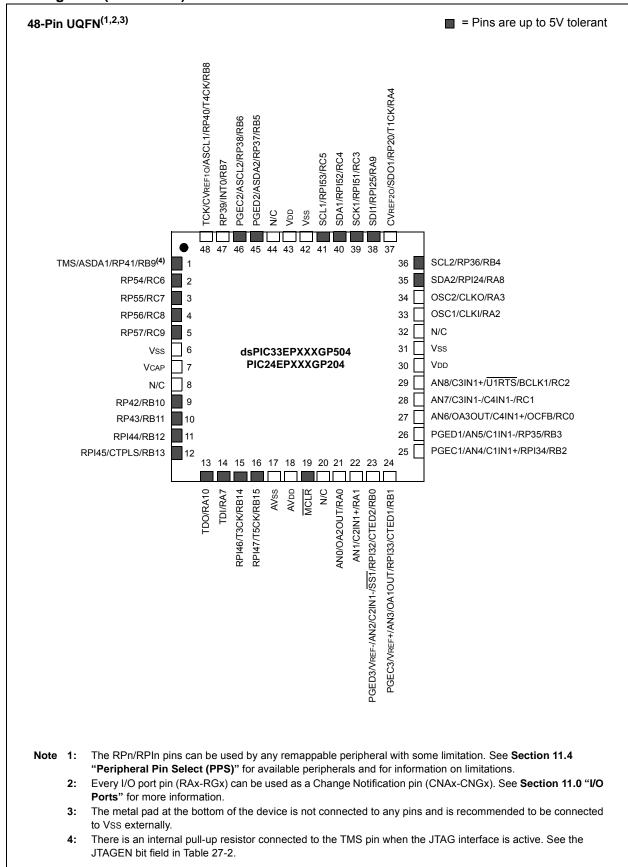

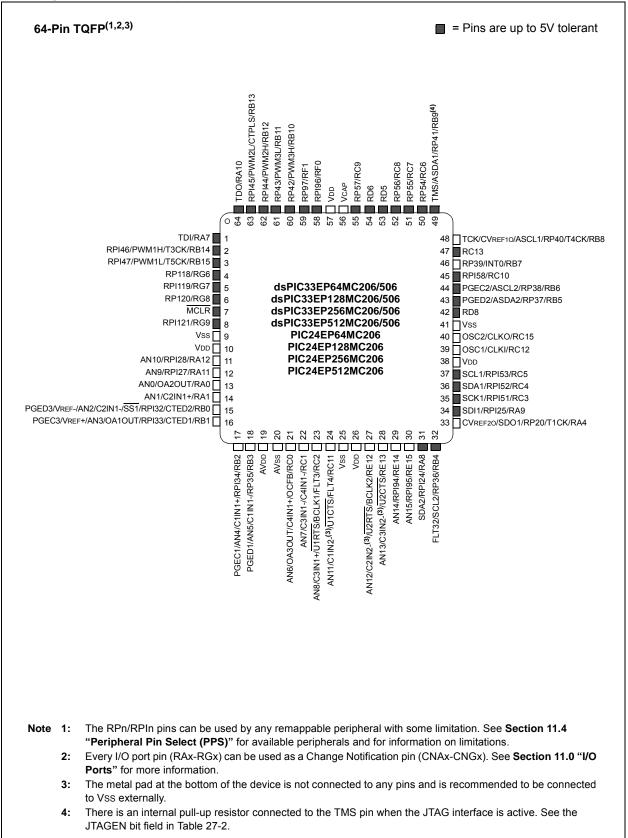

- Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 "Peripheral Pin Select (PPS)" for available peripherals and for information on limitations.

- 2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See **Section 11.0 "I/O Ports"** for more information.

- 3: The metal pad at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# Pin Diagrams (Continued)

# Pin Diagrams (Continued)

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the "dsPIC33/PIC24 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

| $\Box$        |

|---------------|

| ŭ.            |

| 2             |

| 2             |

| 000065        |

| ö             |

| $\rightarrow$ |

| 弌             |

| 1-page        |

| ge            |

| 2             |

| g             |

## TABLE 4-12: PWM REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15       | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8     | Bit 7  | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------|--------------|------------------------------|--------|--------|--------|--------|---------|-----------|--------|-------|---------|-------|-------|-------|----------|-------|---------------|

| PTCON     | 0C00  | PTEN         | _                            | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN   | SYNCEN | SYI   | NCSRC<2 | 2:0>  |       | SEV   | TPS<3:0> |       | 0000          |

| PTCON2    | 0C02  | _            | 1 SEACH SEACH                |        |        |        |        |         |           |        |       |         |       |       | 0000  |          |       |               |

| PTPER     | 0C04  |              | PTPER<15:0>                  |        |        |        |        |         |           |        |       |         |       |       | 00F8  |          |       |               |

| SEVTCMP   | 0C06  |              |                              |        |        |        |        |         | SEVTCMP<1 | 5:0>   |       |         |       |       |       |          |       | 0000          |

| MDC       | 0C0A  |              |                              |        |        |        |        |         | MDC<15:0  | )>     |       |         |       |       |       |          |       | 0000          |

| CHOP      | 0C1A  | CHPCLKEN     | HPCLKEN — — — — CHOPCLK<9:0> |        |        |        |        |         |           |        |       |         |       |       | 0000  |          |       |               |

| PWMKEY    | 0C1E  | PWMKEY<15:0> |                              |        |        |        |        |         |           |        |       | 0000    |       |       |       |          |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12       | Bit 11                                             | Bit 10 | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|--------|---------|--------------|----------------------------------------------------|--------|--------|-----------|----------|--------|-------|---------|-------|----------|-------|-------|---------------|

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN       | CLIEN                                              | TRGIEN | ITB    | MDCS      | DTC<     | :1:0>  | DTCP  | _       | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL         | PMOD                                               | <1:0>  | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA | AT<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | -       |        | (       | CLSRC<4:     | 0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>      |        |        |           |          |        |       | 0000    |       |          |       |       |               |

| PDC1      | 0C26  |         |        |         |              |                                                    |        |        | PDC1<15:0 | 0>       |        |       |         |       |          |       |       | FFF8          |

| PHASE1    | 0C28  |         |        |         | PHASE1<15:0> |                                                    |        |        |           |          |        |       | 0000    |       |          |       |       |               |

| DTR1      | 0C2A  | -       | _      |         |              |                                                    |        |        |           | DTR1<13: | 0>     |       |         |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | -       | _      |         |              |                                                    |        |        | Д         | LTDTR1<1 | 3:0>   |       |         |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |        |         |              |                                                    |        |        | TRGCMP<1  | 5:0>     |        |       |         |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |              | _                                                  | _      | _      | _         | _        | _      |       |         | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF          | PLF FLTLEBEN CLLEBEN BCH BCL BPHH BPHL BPLH BPLL 0 |        |        |           |          |        |       | 0000    |       |          |       |       |               |

| LEBDLY1   | 0C3C  | _       | _      | _       | _            |                                                    |        |        |           |          | LEB<11 | 1:0>  |         |       |          |       |       | 0000          |

| AUXCON1   | 0C3E  | _       | _      | _       | _            | - BLANKSEL<3:0> CHOPSEL<3:0> CHOPHEN CHOPLEN       |        |        |           |          |        |       | 0000    |       |          |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4 | Bit 3   | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|--------|---------|---------|-------|-------|--------|----------|-------|---------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | _      | _      | C4EVT  | C3EVT   | C2EVT   | C1EVT | _     | _      | _        | _     | C4OUT   | C3OUT  | C2OUT     | C1OUT | 0000          |

| CVRCON                   | 0A82  | _      | CVR2OE | _      | _      | _      | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS |         | CVR<   | 3:0>      |       | 0000          |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -       | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  | _      | _      | _      | _      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | A8A0  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN | C      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -       | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  | _      | _      | _      | _      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | ı      | _      | 1      |        | 1      | _       | ı       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN | C      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   |        | 1      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | 1        | CREF  | ı       | I      | CCH       | <1:0> | 0000          |

| CM3MSKSRC <sup>(1)</sup> | 0A96  | ı      | _      | ı      | -      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN | C      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _      | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -       | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | ı      | _      | ı      | _      |        | SELSRO  | CC<3:0> | •     |       | SELSRC | B<3:0>   | •     |         | SELSRC | A<3:0>    | •     | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN | C      | CFDIV<2:0 | >     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

#### **TABLE 4-43: CTMU REGISTER MAP**

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12     | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|---------|----------|------------|----------|----------|----------|----------|---------|---------|-------|--------|---------|-------|-------|-------|---------------|

| CTMUCON1  | 033A  | CTMUEN  | _       | CTMUSIDL | TGEN       | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _      | _       | _     | _     | _     | 0000          |

| CTMUCON2  | 033C  | EDG1MOD | EDG1POL |          | EDG1       | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2SI | EL<3:0> |       | _     | _     | 0000          |

| CTMUICON  | 033E  |         |         | ITRIM<5  | ITRIM<5:0> |          |          |          | <1:0>    | ı       | _       | I     | _      |         |       | _     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11       | Bit 10           | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | _      | _      | _      |              | JDATAH<27:16> x: |       |       |       |       |       |       |       |       |       | xxxx  |               |

| JDATAL    | 0FF2 |        |        |        |        | JDATAL<15:0> |                  |       |       |       |       |       |       |       | 0000  |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

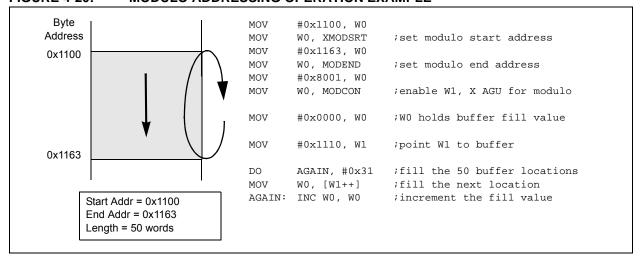

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

**Note:** Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP42  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP43R<5:0>: Peripheral Output Function is Assigned to RP43 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP42R<5:0>: Peripheral Output Function is Assigned to RP42 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP55  | R<5:0> |       |       |

| bit 15 | _   | _     | _     | _     |        | _     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP55R<5:0>:** Peripheral Output Function is Assigned to RP55 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits

(see Table 11-3 for peripheral function numbers)

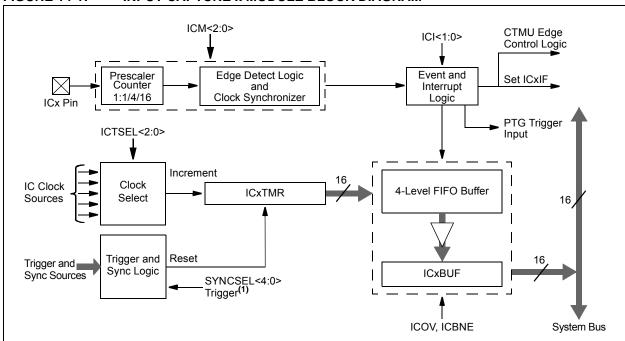

## 14.0 INPUT CAPTURE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

#### FIGURE 14-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

Note 1: The Trigger/Sync source is enabled by default and is set to Timer3 as a source. This timer must be enabled for proper ICx module operation or the Trigger/Sync source must be changed to another source option.

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | _   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | t HS = Hardware Settable bit              |  |

|-------------------|-----------------------------|-------------------------------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'        |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared $x = Bit$ is unknown |  |

bit 15 PTEN: PWMx Module Enable bit 1 = PWMx module is enabled 0 = PWMx module is disabled bit 14 Unimplemented: Read as '0' bit 13 PTSIDL: PWMx Time Base Stop in Idle Mode bit 1 = PWMx time base halts in CPU Idle mode 0 = PWMx time base runs in CPU Idle mode bit 12 **SESTAT:** Special Event Interrupt Status bit 1 = Special event interrupt is pending 0 = Special event interrupt is not pending bit 11 SEIEN: Special Event Interrupt Enable bit 1 = Special event interrupt is enabled 0 = Special event interrupt is disabled EIPU: Enable Immediate Period Updates bit(1) bit 10 1 = Active Period register is updated immediately 0 = Active Period register updates occur on PWMx cycle boundaries bit 9 **SYNCPOL:** Synchronize Input and Output Polarity bit<sup>(1)</sup> 1 = SYNCI1/SYNCO1 polarity is inverted (active-low) 0 = SYNCI1/SYNCO1 is active-high **SYNCOEN:** Primary Time Base Sync Enable bit<sup>(1)</sup> bit 8 1 = SYNCO1 output is enabled 0 = SYNCO1 output is disabled **SYNCEN:** External Time Base Synchronization Enable bit<sup>(1)</sup> bit 7 1 = External synchronization of primary time base is enabled 0 = External synchronization of primary time base is disabled

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| TRGCMP<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15 bit   |       |       |       |       |       |       |       |  |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | TRGCM | 1P<7:0> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPIx Master modes only)

1 = Internal SPIx clock is disabled, pin functions as I/O

0 = Internal SPIx clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data is sampled at end of data output time

0 = Input data is sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

${\tt 1}$  = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Receiver is active

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character (character at the top of the receive FIFO)

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)

- 0 = Framing error has not been detected

- bit 1 OERR: Receive Buffer Overrun Error Status bit (clear/read-only)

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1  $\rightarrow$  0 transition) resets the receiver buffer and the UxRSR to the empty state

- bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

# REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EID<15:0>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|--------|--------|-------|--------|-------|--------|-------|--------|

| F7MSł  | <<1:0> | F6MSł | <<1:0> | F5MS  | K<1:0> | F4MSI | K<1:0> |

| bit 15 |        |       |        | •     |        | •     | bit 8  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0                  | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|-------|-------|-------|------------------------|-------|--------|-------|--------|

| F3MSk | <1:0> | F2MSł | <b>&lt;&lt;1:0&gt;</b> | F1MS  | K<1:0> | F0MSI | K<1:0> |

| bit 7 |       |       |                        |       |        |       | bit 0  |

Legend:

bit 3-2

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 F7MSK<1:0>: Mask Source for Filter 7 bits

11 = Reserved

10 = Acceptance Mask 2 registers contain mask

01 = Acceptance Mask 1 registers contain mask

00 = Acceptance Mask 0 registers contain mask

bit 13-12 **F6MSK<1:0>:** Mask Source for Filter 6 bits (same values as bits<15:14>)

bit 11-10 **F5MSK<1:0>:** Mask Source for Filter 5 bits (same values as bits<15:14>)

bit 9-8 **F4MSK<1:0>:** Mask Source for Filter 4 bits (same values as bits<15:14>)

bit 7-6 **F3MSK<1:0>:** Mask Source for Filter 3 bits (same values as bits<15:14>)

bit 5-4 **F2MSK<1:0>:** Mask Source for Filter 2 bits (same values as bits<15:14>)

**F1MSK<1:0>:** Mask Source for Filter 1 bits (same values as bits<15:14>)

bit 1-0 **F0MSK<1:0>:** Mask Source for Filter 0 bits (same values as bits<15:14>)

# REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0   | R/W-0 | R/W-0   |

|--------|--------|-------|--------|-------|---------|-------|---------|

| F15MSI | K<1:0> | F14MS | K<1:0> | F13MS | SK<1:0> | F12MS | SK<1:0> |

| bit 15 |        |       |        | •     |         | •     | bit 8   |

| R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0  |

|-------|--------|-------|--------|-------|--------|-------|--------|

| F11MS | K<1:0> | F10MS | K<1:0> | F9MS  | K<1:0> | F8MSI | K<1:0> |

| bit 7 |        |       |        |       |        |       | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | F15MSK<1:0>: Mask Source for Filter 15 bits  11 = Reserved  10 = Acceptance Mask 2 registers contain mask  01 = Acceptance Mask 1 registers contain mask  00 = Acceptance Mask 0 registers contain mask |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bits (same values as bits<15:14>)                                                                                                                                |

| bit 11-10 | F13MSK<1:0>: Mask Source for Filter 13 bits (same values as bits<15:14>)                                                                                                                                |

| bit 9-8   | F12MSK<1:0>: Mask Source for Filter 12 bits (same values as bits<15:14>)                                                                                                                                |

| bit 7-6   | F11MSK<1:0>: Mask Source for Filter 11 bits (same values as bits<15:14>)                                                                                                                                |

| bit 5-4   | F10MSK<1:0>: Mask Source for Filter 10 bits (same values as bits<15:14>)                                                                                                                                |

| bit 3-2   | F9MSK<1:0>: Mask Source for Filter 9 bits (same values as bits<15:14>)                                                                                                                                  |

| bit 1-0   | F8MSK<1:0>: Mask Source for Filter 8 bits (same values as bits<15:14>)                                                                                                                                  |

TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS |                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |       |            |       |         |  |

|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|---------|--|

| Parameter<br>No.   | Тур.                | Max.                                                                                                                                                                                                                                             | Units | Conditions |       |         |  |

| Idle Current (III  | DLE) <sup>(1)</sup> |                                                                                                                                                                                                                                                  |       |            |       |         |  |

| DC40d              | 3                   | 8                                                                                                                                                                                                                                                | mA    | -40°C      |       |         |  |

| DC40a              | 3                   | 8                                                                                                                                                                                                                                                | mA    | +25°C      | 3.3V  | 10 MIPS |  |

| DC40b              | 3                   | 8                                                                                                                                                                                                                                                | mA    | +85°C      | 3.3 V | 10 MIFS |  |

| DC40c              | 3                   | 8                                                                                                                                                                                                                                                | mA    | +125°C     |       |         |  |

| DC42d              | 6                   | 12                                                                                                                                                                                                                                               | mA    | -40°C      |       | 20 MIPS |  |

| DC42a              | 6                   | 12                                                                                                                                                                                                                                               | mA    | +25°C      | 3.3V  |         |  |

| DC42b              | 6                   | 12                                                                                                                                                                                                                                               | mA    | +85°C      | J.5 V |         |  |

| DC42c              | 6                   | 12                                                                                                                                                                                                                                               | mA    | +125°C     |       |         |  |

| DC44d              | 11                  | 18                                                                                                                                                                                                                                               | mA    | -40°C      |       |         |  |

| DC44a              | 11                  | 18                                                                                                                                                                                                                                               | mA    | +25°C      | 3.3V  | 40 MIPS |  |

| DC44b              | 11                  | 18                                                                                                                                                                                                                                               | mA    | +85°C      | 3.5 V |         |  |

| DC44c              | 11                  | 18                                                                                                                                                                                                                                               | mA    | +125°C     |       |         |  |

| DC45d              | 17                  | 27                                                                                                                                                                                                                                               | mA    | -40°C      |       | 60 MIPS |  |

| DC45a              | 17                  | 27                                                                                                                                                                                                                                               | mA    | +25°C      | 3.3V  |         |  |

| DC45b              | 17                  | 27                                                                                                                                                                                                                                               | mA    | +85°C      |       |         |  |

| DC45c              | 17                  | 27                                                                                                                                                                                                                                               | mA    | +125°C     |       |         |  |

| DC46d              | 20                  | 35                                                                                                                                                                                                                                               | mA    | -40°C      |       |         |  |

| DC46a              | 20                  | 35                                                                                                                                                                                                                                               | mA    | +25°C      | 3.3V  | 70 MIPS |  |

| DC46b              | 20                  | 35                                                                                                                                                                                                                                               | mA    | +85°C      |       |         |  |

Note 1: Base Idle current (IIDLE) is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- · JTAG is disabled

TABLE 30-60: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                      |         |       |            |                                      |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|-------|------------|--------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                  | Min. Typ. Max. Units |         |       | Conditions |                                      |

|                    |        | Clock                                                                                                                                                                                                                                                           | k Paramet            | ters    |       |            |                                      |

| AD50               | TAD    | ADC Clock Period                                                                                                                                                                                                                                                | 117.6                | _       | -     | ns         |                                      |

| AD51               | trc    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                                                                                                                                                                                | _                    | 250     | _     | ns         |                                      |

|                    |        | Con                                                                                                                                                                                                                                                             | version R            | ate     |       |            |                                      |

| AD55               | tconv  | Conversion Time                                                                                                                                                                                                                                                 | _                    | 14 TAD  |       | ns         |                                      |

| AD56               | FCNV   | Throughput Rate                                                                                                                                                                                                                                                 | _                    | _       | 500   | ksps       |                                      |

| AD57a              | TSAMP  | Sample Time when Sampling any ANx Input                                                                                                                                                                                                                         | 3 TAD                |         | 1     | _          |                                      |

| AD57b              | TSAMP  | Sample Time when Sampling the Op<br>Amp Outputs (Configuration A and<br>Configuration B) <sup>(4,5)</sup>                                                                                                                                                       | 3 TAD                | _       | _     | _          |                                      |

|                    |        | Timin                                                                                                                                                                                                                                                           | g Parame             | ters    |       |            |                                      |

| AD60               | tPCS   | Conversion Start from Sample Trigger <sup>(2,3)</sup>                                                                                                                                                                                                           | 2 TAD                | _       | 3 TAD | _          | Auto-convert trigger is not selected |

| AD61               | tPSS   | Sample Start from Setting Sample (SAMP) bit (2,3)                                                                                                                                                                                                               | 2 TAD                | _       | 3 TAD | _          |                                      |

| AD62               | tcss   | Conversion Completion to Sample Start (ASAM = $1$ ) <sup>(2,3)</sup>                                                                                                                                                                                            | _                    | 0.5 TAD | _     | _          |                                      |

| AD63               | tDPU   | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(2,3)</sup>                                                                                                                                                                                          | _                    | _       | 20    | μS         | (Note 6)                             |

- **Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- **4:** See Figure 25-6 for configuration information.

- **5:** See Figure 25-7 for configuration information.

- **6:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

#### 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between -40°C to +150°C are identical to those shown in **Section 30.0 "Electrical Characteristics"** for operation between -40°C to +125°C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into VDD pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

|                                                                                   |                      |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- **3:** Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

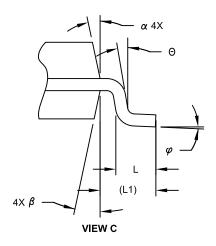

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |           | MILLIMETERS |          |      |  |

|--------------------------|-----------|-------------|----------|------|--|

| Dimensi                  | on Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N         | 28          |          | •    |  |

| Pitch                    | е         |             | 1.27 BSC |      |  |

| Overall Height           | Α         | -           | -        | 2.65 |  |

| Molded Package Thickness | A2        | 2.05        | -        | -    |  |

| Standoff §               | A1        | 0.10        | =        | 0.30 |  |

| Overall Width            | E         | 10.30 BSC   |          |      |  |

| Molded Package Width     | E1        | 7.50 BSC    |          |      |  |

| Overall Length           | D         | 17.90 BSC   |          |      |  |

| Chamfer (Optional)       | h         | 0.25        | -        | 0.75 |  |

| Foot Length              | L         | 0.40        | -        | 1.27 |  |

| Footprint                | L1        | 1.40 REF    |          |      |  |

| Lead Angle               | Θ         | 0°          | -        | -    |  |

| Foot Angle               | φ         | 0°          | -        | 8°   |  |

| Lead Thickness           | С         | 0.18        | -        | 0.33 |  |

| Lead Width               | b         | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α         | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β         | 5°          | _        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

| ECAN Module                                  |          | Instruction Set                             |     |

|----------------------------------------------|----------|---------------------------------------------|-----|

| Control Registers                            | 290      | Overview                                    | 390 |

| Modes of Operation                           | 289      | Summary                                     | 387 |

| Overview                                     | 287      | Symbols Used in Opcode Descriptions         | 388 |

| Resources                                    | 289      | Inter-Integrated Circuit (I <sup>2</sup> C) | 273 |

| Electrical Characteristics                   | 401      | Control Registers                           |     |

| AC                                           | 413, 471 | Resources                                   |     |

| Enhanced CAN (ECAN) Module                   |          | Internal RC Oscillator                      |     |

| Equations                                    |          | Use with WDT                                | 385 |

| Device Operating Frequency                   | 154      | Internet Address                            |     |

| FPLLO Calculation                            |          | Interrupt Controller                        | 02- |

| FVCO Calculation                             |          | •                                           | 121 |

|                                              |          | Control and Status Registers                |     |

| Errata                                       | 23       | INTCON1                                     |     |

| F                                            |          | INTCON2                                     |     |

| Filter Organitar (O===) Organifications      | 400      | INTCON3                                     |     |

| Filter Capacitor (CEFC) Specifications       |          | INTCON4                                     |     |

| Flash Program Memory                         |          | INTTREG                                     |     |

| Control Registers                            |          | Interrupt Vector Details                    |     |

| Programming Operations                       |          | Interrupt Vector Table (IVT)                | 127 |

| Resources                                    |          | Reset Sequence                              | 127 |

| RTSP Operation                               | 120      | Resources                                   | 131 |

| Table Instructions                           | 119      | _                                           |     |

| Flexible Configuration                       | 379      | J                                           |     |

| _                                            |          | JTAG Boundary Scan Interface                | 379 |

| G                                            |          | JTAG Interface                              |     |

| Guidelines for Getting Started               | 29       | o in Contact                                |     |

| Application Examples                         |          | M                                           |     |

| Basic Connection Requirements                |          | Memory Maps                                 |     |

|                                              |          | · ·                                         | 100 |

| CPU Logic Filter Capacitor Connection (VCAP) |          | Extended Data Space                         |     |

| Decoupling Capacitors                        |          | Memory Organization                         |     |

| External Oscillator Pins                     |          | Resources                                   |     |

| ICSP Pins                                    |          | Microchip Internet Web Site                 |     |

| Master Clear (MCLR) Pin                      |          | Modulo Addressing                           |     |

| Oscillator Value Conditions on Start-up      | 32       | Applicability                               | 115 |

| Unused I/Os                                  | 32       | Operation Example                           | 114 |

|                                              |          | Start and End Address                       | 114 |

| Н                                            |          | W Address Register Selection                | 114 |

| High-Speed PWM                               | 225      | MPLAB Assembler, Linker, Librarian          |     |

| Control Registers                            | 230      | MPLAB ICD 3 In-Circuit Debugger             |     |

| Faults                                       |          | MPLAB PM3 Device Programmer                 |     |

| Resources                                    |          | MPLAB REAL ICE In-Circuit Emulator System   |     |

| High-Temperature Electrical Characteristics  |          | MPLAB X Integrated Development              | 000 |

| Absolute Maximum Ratings                     |          | • '                                         | 207 |

| Absolute Maximum Natings                     | 407      | Environment Software                        |     |

|                                              |          | MPLAB X SIM Software Simulator              |     |

| I/O Ports                                    | 170      | MPLIB Object Librarian                      |     |

|                                              | 173      | MPLINK Object Linker                        | 398 |

| Helpful Tips                                 |          | 0                                           |     |

| Parallel I/O (PIO)                           |          | O                                           |     |

| Resources                                    |          | Op Amp                                      |     |

| Write/Read Timing                            |          | Application Considerations                  | 358 |

| In-Circuit Debugger                          | 386      | Configuration A                             | 358 |

| In-Circuit Emulation                         | 379      | Configuration B                             | 359 |

| In-Circuit Serial Programming (ICSP)         | 379, 386 | Op Amp/Comparator                           |     |

| Input Capture                                |          | Control Registers                           |     |

| Control Registers                            |          | Resources                                   |     |

| Resources                                    |          | Open-Drain Configuration                    |     |

| Input Change Notification (ICN)              |          |                                             | 1/4 |

|                                              |          | Oscillator                                  | 450 |

| Instruction Addressing Modes                 |          | Control Registers                           |     |

| File Register Instructions                   |          | Resources                                   |     |

| Fundamental Modes Supported                  |          | Output Compare                              | 219 |

| MAC Instructions                             |          | Control Registers                           | 221 |

| MCU Instructions                             |          | Resources                                   | 220 |

| Move and Accumulator Instructions            | 113      |                                             |     |

| Other Instructions                           | 113      |                                             |     |