Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

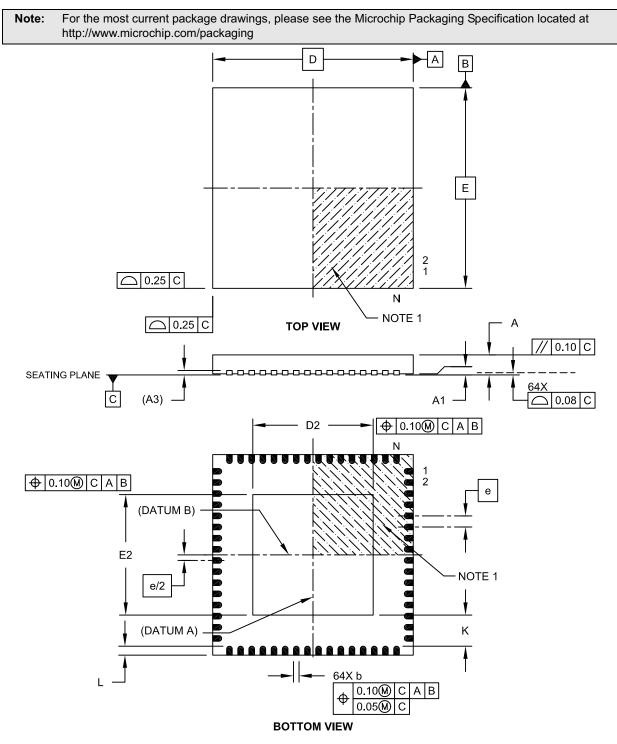

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc204t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

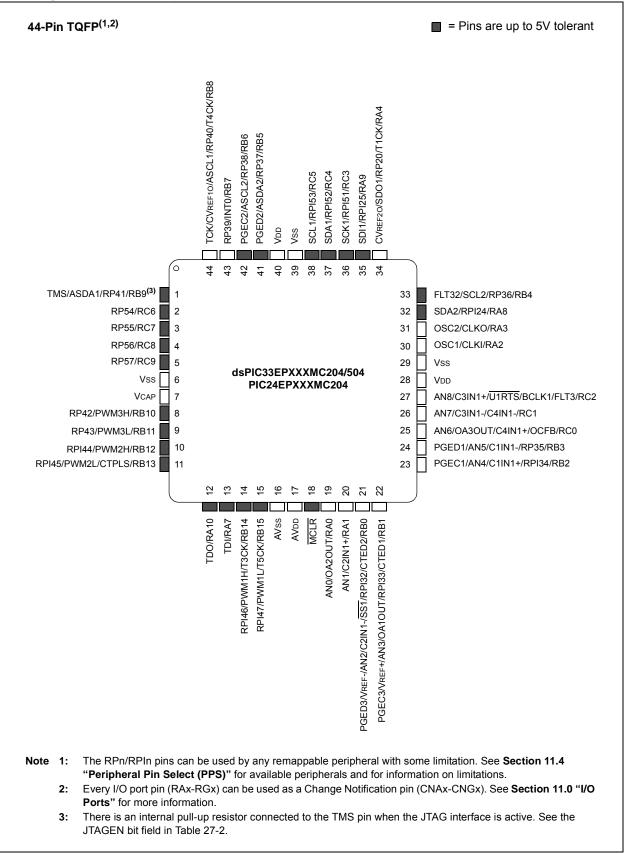

#### Pin Diagrams (Continued)

| 1:    | CPU C                                                                                                 | ORE RE                                                                                                                            | EGISTEI                                                                                               | R MAP F                                                                           | OR dsF                                                                                                                                              | PIC33EP                                                                                                                                                                  | XXXMC                                                                                                                                                                                     | 20X/50X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ( AND d                                                                                                                                                                                                                                               | sPIC33                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EPXXX                                                                                                                                                                                                                                                                                                                                                                                                             | GP50X                                                                                                                                                                                                                                                                                    | DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S ONL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Y (CON                                                                                                                                       | TINUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr. | Bit 15                                                                                                | Bit 14                                                                                                                            | Bit 13                                                                                                | Bit 12                                                                            | Bit 11                                                                                                                                              | Bit 10                                                                                                                                                                   | Bit 9                                                                                                                                                                                     | Bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 7                                                                                                                                                                                                                                                 | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 5                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 4                                                                                                                                                                                                                                                                                    | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 1                                                                                                                                        | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | All<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0042  | OA                                                                                                    | OB                                                                                                                                | SA                                                                                                    | SB                                                                                | OAB                                                                                                                                                 | SAB                                                                                                                                                                      | DA                                                                                                                                                                                        | DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IPL2                                                                                                                                                                                                                                                  | IPL1                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IPL0                                                                                                                                                                                                                                                                                                                                                                                                              | RA                                                                                                                                                                                                                                                                                       | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Z                                                                                                                                            | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0044  | VAR                                                                                                   | _                                                                                                                                 | US<                                                                                                   | :1:0>                                                                             | EDT                                                                                                                                                 | EDT DL<2:0> SATA SATB SATDW ACCSAT IPL3 SFA RND                                                                                                                          |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   | IF                                                                                                                                                                                                                                                                                       | 0020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0046  | XMODEN                                                                                                | YMODEN                                                                                                                            | _                                                                                                     | _                                                                                 |                                                                                                                                                     | BWM<3:0> YWM<3:0> XWM<3:0>                                                                                                                                               |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0048  |                                                                                                       | •                                                                                                                                 |                                                                                                       | •                                                                                 | •                                                                                                                                                   | XMODSRT<15:0>                                                                                                                                                            |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 004A  |                                                                                                       |                                                                                                                                   |                                                                                                       |                                                                                   |                                                                                                                                                     | XMODEND<15:0> —                                                                                                                                                          |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 004C  |                                                                                                       |                                                                                                                                   |                                                                                                       |                                                                                   |                                                                                                                                                     |                                                                                                                                                                          | YMC                                                                                                                                                                                       | DSRT<15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )>                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 004E  |                                                                                                       |                                                                                                                                   |                                                                                                       |                                                                                   |                                                                                                                                                     |                                                                                                                                                                          | YMC                                                                                                                                                                                       | DEND<15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )>                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0050  | BREN                                                                                                  |                                                                                                                                   |                                                                                                       |                                                                                   |                                                                                                                                                     |                                                                                                                                                                          |                                                                                                                                                                                           | XBF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REV<14:0>                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0052  | _                                                                                                     | _                                                                                                                                 |                                                                                                       |                                                                                   |                                                                                                                                                     |                                                                                                                                                                          |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DISICNT<                                                                                                                                                                                                                                              | 13:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0054  | _                                                                                                     | _                                                                                                                                 | _                                                                                                     | _                                                                                 | _                                                                                                                                                   | _                                                                                                                                                                        | _                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   | TBLPA                                                                                                                                                                                                                                                                                    | G<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |