Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | - ·                                                                              |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc204t-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

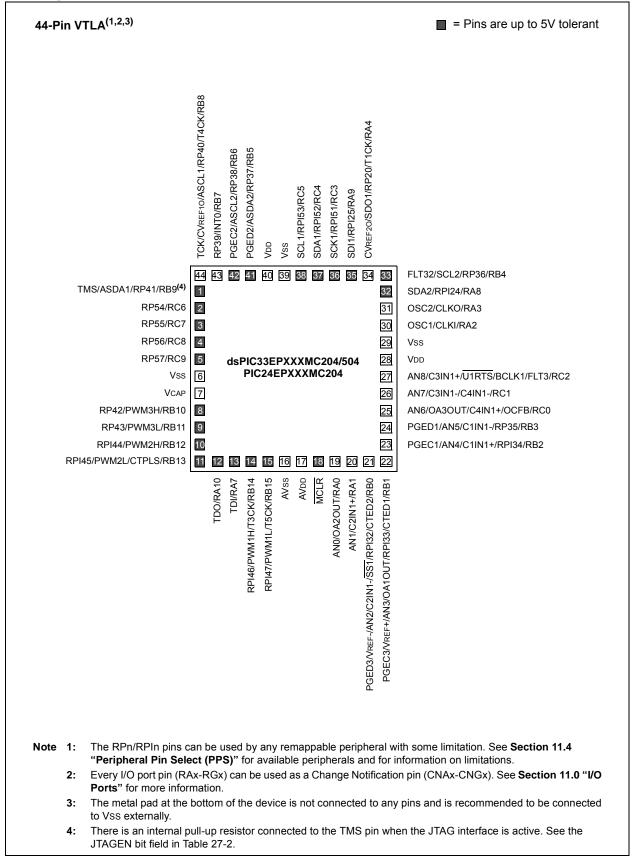

#### Pin Diagrams (Continued)

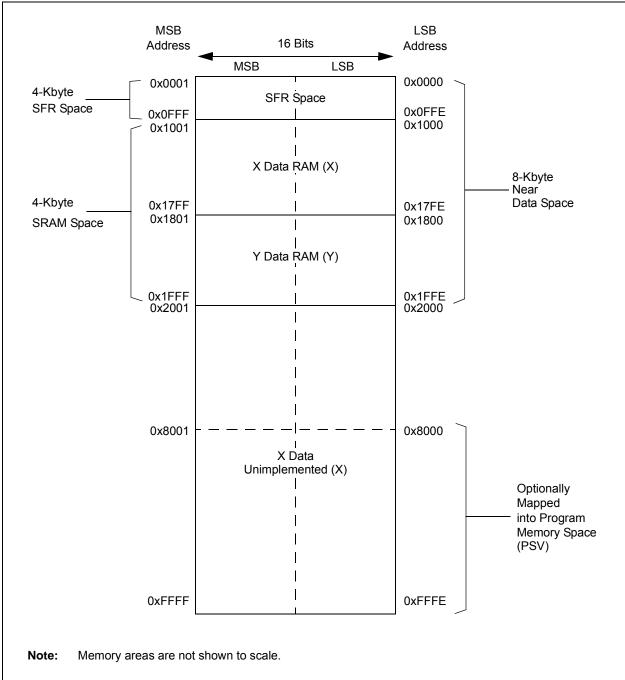

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0                                                                  | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0      | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|------------|-----------------|-------|

| —                                                                    |                           |                                                                                                    |                            | QEB1R<6:0>        |            |                 |       |

| bit 15                                                               |                           |                                                                                                    |                            |                   |            |                 | bit 8 |

|                                                                      |                           |                                                                                                    |                            |                   |            |                 |       |

| U-0                                                                  | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0      | R/W-0           | R/W-0 |

| —                                                                    |                           |                                                                                                    |                            | QEA1R<6:0>        |            |                 |       |

| bit 7                                                                |                           |                                                                                                    |                            |                   |            |                 | bit 0 |

|                                                                      |                           |                                                                                                    |                            |                   |            |                 |       |

| Legend:                                                              |                           |                                                                                                    |                            |                   |            |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                           |                                                                                                    |                            |                   |            |                 |       |

| -n = Value a                                                         | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared       | x = Bit is unkr | nown  |

|                                                                      | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |            |                 |       |

| bit 7                                                                | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |            |                 |       |

| bit 6-0                                                              | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits |                 |       |

#### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0                                                                      | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0         | R/W-0           | R/W-0  |

|--------------------------------------------------------------------------|--------------|--------------------------------------------------------|---------------|----------------------|---------------|-----------------|--------|

| _                                                                        |              |                                                        |               | HOME1R<6:0           | >             |                 |        |

| bit 15                                                                   |              |                                                        |               |                      |               |                 | bit 8  |

|                                                                          |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0               | 5444.0        | -               | 5444.6 |

| U-0                                                                      | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0         | R/W-0           | R/W-0  |

|                                                                          |              |                                                        |               | INDX1R<6:0>          | >             |                 |        |

| bit 7                                                                    |              |                                                        |               |                      |               |                 | bit C  |

| Legend:                                                                  |              |                                                        |               |                      |               |                 |        |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |              |                                                        |               |                      |               |                 |        |

| -n = Value a                                                             | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cleared |               | x = Bit is unkr | nown   |

|                                                                          |              | nput tied to RPI                                       |               |                      |               |                 |        |

|                                                                          |              | nput tied to CM<br>nput tied to Vss                    |               |                      |               |                 |        |

| bit 7                                                                    |              | nted: Read as '                                        |               |                      |               |                 |        |

| bit 6-0                                                                  | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                    | responding RI | Pn Pin bits     |        |

|                                                                          |              | nput tied to CM                                        |               |                      |               |                 |        |

#### REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                                                                | R/W-0            | R/W-0                                                    | R/W-0                                           | R/W-0       | R/W-0 | R/W-0           | R/W-0 |  |

|--------------------------------------------------------------------|------------------|----------------------------------------------------------|-------------------------------------------------|-------------|-------|-----------------|-------|--|

|                                                                    |                  |                                                          |                                                 | DTCMP3R<6:0 | )>    |                 |       |  |

| bit 15                                                             |                  |                                                          |                                                 |             |       |                 | bit 8 |  |

| U-0                                                                | R/W-0            | R/W-0                                                    | R/W-0                                           | R/W-0       | R/W-0 | R/W-0           | R/W-0 |  |

| 0-0                                                                | R/W-0            | R/W-0                                                    | -                                               | DTCMP2R<6:0 |       | R/W-0           | R/W-U |  |

| bit 7                                                              |                  |                                                          |                                                 |             | 17    |                 | bit 0 |  |

| bit i                                                              |                  |                                                          |                                                 |             |       |                 | bit 0 |  |

| Legend:                                                            |                  |                                                          |                                                 |             |       |                 |       |  |

| R = Readab                                                         | ole bit          | W = Writable                                             | Writable bit U = Unimplemented bit, read as '0' |             |       |                 |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |                  |                                                          |                                                 |             |       | x = Bit is unkr | nown  |  |

|                                                                    |                  |                                                          |                                                 |             |       |                 |       |  |

|                                                                    |                  | nput tied to CMI                                         |                                                 |             |       |                 |       |  |

| bit 7                                                              | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |                                                 |             |       |                 |       |  |

NOTES:

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                                                                       | CONTROL R      | EGISTER          |                      |                      |                     |  |  |  |

|---------------|-----------------------------------------|------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|--|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                                                            | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                                                            | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |

| bit 15        | ·                                       | •                                                                                  |                | ÷                |                      |                      | bit                 |  |  |  |

| R/W-0         | R/W-0                                   | R/W-0                                                                              | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| DTC1          |                                         | DTCP <sup>(3)</sup>                                                                | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |

| bit 7         | DICO                                    | DICE                                                                               | _              | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |

|               |                                         |                                                                                    |                |                  |                      |                      | <u> </u>            |  |  |  |

| Legend:       |                                         | HC = Hardware                                                                      | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |

| R = Reada     | able bit                                | W = Writable bi                                                                    | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |

| -n = Value    | at POR                                  | '1' = Bit is set                                                                   |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                                                                | is hit(1)      |                  |                      |                      |                     |  |  |  |

| DIL 15        |                                         | rrupt is pending                                                                   |                |                  |                      |                      |                     |  |  |  |

|               |                                         | interrupt is pendi                                                                 | ng             |                  |                      |                      |                     |  |  |  |

|               |                                         | ared by setting F                                                                  |                |                  |                      |                      |                     |  |  |  |

| bit 14        |                                         | rent-Limit Interru                                                                 | •              |                  |                      |                      |                     |  |  |  |

|               |                                         | mit interrupt is pe                                                                |                |                  |                      |                      |                     |  |  |  |

|               |                                         | nt-limit interrupt is<br>ared by setting C                                         |                |                  |                      |                      |                     |  |  |  |

| bit 13        |                                         | This bit is cleared by setting CLIEN = 0.<br>TRGSTAT: Trigger Interrupt Status bit |                |                  |                      |                      |                     |  |  |  |

|               |                                         | terrupt is pendin                                                                  |                |                  |                      |                      |                     |  |  |  |

|               |                                         | r interrupt is pen                                                                 |                |                  |                      |                      |                     |  |  |  |

|               |                                         | ared by setting T                                                                  |                |                  |                      |                      |                     |  |  |  |

| bit 12        |                                         | t Interrupt Enable                                                                 | e bit          |                  |                      |                      |                     |  |  |  |

|               |                                         | rrupt is enabled rrupt is disabled                                                 | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |  |

| bit 11        |                                         | ent-Limit Interrup                                                                 |                |                  | cu .                 |                      |                     |  |  |  |

|               |                                         | mit interrupt is er                                                                |                |                  |                      |                      |                     |  |  |  |

|               |                                         | mit interrupt is di                                                                |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                                                                   | able bit       |                  |                      |                      |                     |  |  |  |

|               |                                         | event generates                                                                    |                |                  | T hit is cleared     |                      |                     |  |  |  |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I                                             |                |                  | i bit is cleared     |                      |                     |  |  |  |

| DIL 9         |                                         | register provides                                                                  |                | riad for this PM | VM generator         |                      |                     |  |  |  |

|               |                                         | egister provides f                                                                 | •              |                  | •                    |                      |                     |  |  |  |

| bit 8         |                                         | er Duty Cycle Re                                                                   |                |                  |                      |                      |                     |  |  |  |

|               |                                         | ister provides du<br>jister provides du                                            |                |                  |                      | r                    |                     |  |  |  |

| Note 1:       | Software must clea                      |                                                                                    |                |                  | -                    |                      | t controller        |  |  |  |

| Note 1.<br>2: | These bits should                       | -                                                                                  |                | -                | -                    | the interrup         |                     |  |  |  |

| 3:            | DTC<1:0> = 11 fo                        | -                                                                                  |                | -                | -                    |                      |                     |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                                                                   |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |

| 5:            | To operate in Exter                     |                                                                                    | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |  |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| R/W-0                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |

|------------------------------------------------------------|-------|-------|-------|-----------------------------------------|-----------|-------|-------|

|                                                            |       |       | INDXH | LD<15:8>                                |           |       |       |

| bit 15                                                     |       |       |       |                                         |           |       | bit 8 |

|                                                            |       |       |       |                                         |           |       |       |

| R/W-0                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |

|                                                            |       |       | INDXF | ILD<7:0>                                |           |       |       |

| bit 7                                                      |       |       |       |                                         |           |       | bit 0 |

| Legend:                                                    |       |       |       |                                         |           |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, r |       |       |       | nented bit, rea                         | ad as '0' |       |       |

| -n = Value at POR '1' = Bit is set                         |       |       |       | '0' = Bit is cleared x = Bit is unknown |           |       |       |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

#### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                                                           | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                       | R/W-0                                                                               |  |

|-----------------------------------------------------------------|-------|----------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

|                                                                 |       | QEIIC                            | <31:24>                             |                                                                                       |                                                                                                                                             |                                                                                     |  |

|                                                                 |       |                                  |                                     |                                                                                       |                                                                                                                                             | bit 8                                                                               |  |

|                                                                 |       |                                  |                                     |                                                                                       |                                                                                                                                             |                                                                                     |  |

| R/W-0                                                           | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                       | R/W-0                                                                               |  |

|                                                                 |       | QEIIC                            | <23:16>                             |                                                                                       |                                                                                                                                             |                                                                                     |  |

|                                                                 |       |                                  |                                     |                                                                                       |                                                                                                                                             | bit 0                                                                               |  |

|                                                                 |       |                                  |                                     |                                                                                       |                                                                                                                                             |                                                                                     |  |

|                                                                 |       |                                  |                                     |                                                                                       |                                                                                                                                             |                                                                                     |  |

| R = Readable bit W = Writable bit U                             |       |                                  |                                     | U = Unimplemented bit, read as '0'                                                    |                                                                                                                                             |                                                                                     |  |

| = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is |       |                                  | x = Bit is unkr                     | nown                                                                                  |                                                                                                                                             |                                                                                     |  |

|                                                                 | R/W-0 | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplen | QEIIC<31:24>         R/W-0       R/W-0       R/W-0         QEIIC<23:16>         it       W = Writable bit       U = Unimplemented bit, real | QEIIC<31:24>         R/W-0       R/W-0       R/W-0       R/W-0         QEIIC<23:16> |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                  | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|--------------|----------------------------------------|------------------------------------|-------|-------|-------|--|

|                                    |       |              | QEII                                   | C<15:8>                            |       |       |       |  |

| bit 15                             |       |              |                                        |                                    |       |       | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                  | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |              | QEI                                    | C<7:0>                             |       |       |       |  |

| bit 7                              |       |              |                                        |                                    |       |       | bit C |  |

| Legend:                            |       |              |                                        |                                    |       |       |       |  |

| R = Readable                       | bit   | W = Writable | bit                                    | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknow |                                    |       | nown  |       |  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                                                                  | R/W-x | R/W-x | R/W-x | R/W-x           | R/W-x | R/W-x | R/W-x |

|------------------------------------------------------------------------|-------|-------|-------|-----------------|-------|-------|-------|

|                                                                        |       |       | Ву    | /te 3           |       |       |       |

| bit 15                                                                 |       |       |       |                 |       |       | bit 8 |

|                                                                        |       |       |       |                 |       |       |       |

| R/W-x                                                                  | R/W-x | R/W-x | R/W-x | R/W-x           | R/W-x | R/W-x | R/W-x |

|                                                                        |       |       | Ву    | /te 2           |       |       |       |

| bit 7                                                                  |       |       |       |                 |       |       | bit 0 |

| Legend:                                                                |       |       |       |                 |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'   |       |       |       |                 |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       |       |       | x = Bit is unkr | nown  |       |       |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x           | R/W-x                             | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|-----------------|-----------------------------------|------------------|-------|------------------------------------|-------|-------|-------|--|

|                 |                                   |                  | В     | yte 5                              |       |       |       |  |

| bit 15          |                                   |                  |       |                                    |       |       | bit 8 |  |

| R/W-x           | R/W-x                             | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|                 |                                   |                  |       | yte 4                              |       |       |       |  |

| bit 7           |                                   |                  |       | -                                  |       |       | bit 0 |  |

|                 |                                   |                  |       |                                    |       |       |       |  |

| Legend:         |                                   |                  |       |                                    |       |       |       |  |

| R = Readable I  | R = Readable bit W = Writable bit |                  |       | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at P | OR                                | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is un |       |       | nown  |  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

| _                    |                                                                     |                                 |                         |                        |                      |                      |                      |  |  |  |

|----------------------|---------------------------------------------------------------------|---------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|--|--|--|

| R/W-0                | U-0                                                                 | U-0                             | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| ADRC                 | —                                                                   | —                               | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |  |  |  |

| bit 15               |                                                                     |                                 |                         |                        |                      |                      | bit 8                |  |  |  |

|                      |                                                                     |                                 |                         |                        |                      |                      |                      |  |  |  |

| R/W-0                | R/W-0                                                               | R/W-0                           | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>                                                | ADCS5 <sup>(2)</sup>            | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |  |  |  |

| bit 7                |                                                                     |                                 |                         |                        |                      |                      | bit 0                |  |  |  |

| r                    |                                                                     |                                 |                         |                        |                      |                      |                      |  |  |  |

| Legend:              |                                                                     |                                 |                         |                        |                      |                      |                      |  |  |  |

| R = Readable b       |                                                                     | W = Writable k                  | bit                     | •                      | nented bit, read     | l as '0'             |                      |  |  |  |

| -n = Value at P      | OR                                                                  | '1' = Bit is set                |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |  |  |  |

| bit 15               | ADRC: ADC1 Conversion Clock Source bit<br>1 = ADC internal RC clock |                                 |                         |                        |                      |                      |                      |  |  |  |

|                      |                                                                     | ved from syste                  |                         |                        |                      |                      |                      |  |  |  |

| bit 14-13            | •                                                                   | ted: Read as '0                 |                         |                        |                      |                      |                      |  |  |  |

| bit 12-8             |                                                                     | Auto-Sample T                   | ime bits <sup>(1)</sup> |                        |                      |                      |                      |  |  |  |

|                      | 11111 = <b>31</b> T                                                 | AD                              |                         |                        |                      |                      |                      |  |  |  |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |  |  |  |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |  |  |  |

|                      | 00001 = 1 TA<br>00000 = 0 TA                                        |                                 |                         |                        |                      |                      |                      |  |  |  |

| bit 7-0              | ADCS<7:0>:                                                          | ADC1 Convers                    | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |  |  |  |

|                      | 11111111 = <sup>-</sup><br>•                                        | TP • (ADCS<7:                   | 0> + 1) = TP •          | 256 = Tad              |                      |                      |                      |  |  |  |

|                      | •                                                                   |                                 |                         |                        |                      |                      |                      |  |  |  |

|                      | 00000010 = -                                                        | TP • (ADCS<7:                   | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |  |  |  |

|                      | 0000001 =                                                           | TP • (ADCS<7:<br>TP • (ADCS<7:  | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |  |  |  |

|                      | •                                                                   | d if SSRC<2:0><br>if ADRC (AD10 | •                       | ,                      | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |  |  |  |

#### REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0      | U-0                                      | U-0                                                             | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |

|------------|------------------------------------------|-----------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|

| CH0NB      |                                          | _                                                               | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |

| bit 15     |                                          | -                                                               |                                 |                       |                          |                       | bit 8                 |

|            |                                          |                                                                 |                                 |                       |                          |                       |                       |

| R/W-0      | U-0                                      | U-0                                                             | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |

| CH0NA      |                                          | _                                                               | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |

| bit 7      |                                          |                                                                 |                                 |                       |                          |                       | bit C                 |

|            |                                          |                                                                 |                                 |                       |                          |                       |                       |

| Legend:    |                                          |                                                                 |                                 |                       |                          |                       |                       |

| R = Reada  |                                          | W = Writable                                                    |                                 |                       | nented bit, read         |                       |                       |

| -n = Value | e at POR                                 | '1' = Bit is set                                                |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |

| hit 15     |                                          |                                                                 | Input Coloct for                | r Comple MUX          |                          |                       |                       |

| bit 15     |                                          | nannel 0 Negative<br>el 0 negative input                        |                                 |                       |                          |                       |                       |

|            |                                          | el 0 negative input                                             |                                 |                       |                          |                       |                       |

| bit 14-13  | Unimpleme                                | ented: Read as '0                                               | )'                              |                       |                          |                       |                       |

| bit 12-8   | CH0SB<4:0                                | 0>: Channel 0 Po:                                               | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |

|            |                                          | pen; use this sele                                              |                                 |                       |                          | ement                 |                       |

|            | 11110 <b>= Ch</b>                        | nannel 0 positive in                                            | put is connected                | to the CTMU te        | mperature meas           | surement diode        | (CTMU TEMP            |

|            | 11101 <b>= R</b> e                       |                                                                 |                                 |                       |                          |                       |                       |

|            | 11100 <b>= Re</b><br>11011 <b>= Re</b>   |                                                                 |                                 |                       |                          |                       |                       |

|            |                                          | nannel 0 positive i                                             | input is the outp               | out of OA3/AN6        | (2,3)                    |                       |                       |

|            |                                          | nannel 0 positive i                                             |                                 |                       |                          |                       |                       |

|            |                                          | nannel 0 positive i                                             | input is the outp               | out of OA1/AN3        | (2)                      |                       |                       |

|            | 10111 <b>= Re</b>                        | served                                                          |                                 |                       |                          |                       |                       |

|            | •                                        |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                        |                                                                 |                                 |                       |                          |                       |                       |

|            | 10000 <b>= Re</b>                        |                                                                 |                                 |                       |                          |                       |                       |

|            | 01111 = Ch                               | nannel 0 positive i                                             | input is AN15 <sup>(3)</sup>    |                       |                          |                       |                       |

|            | 01110 = Cr                               | nannel 0 positive i<br>nannel 0 positive i                      | input is AN14 <sup>(3)</sup>    |                       |                          |                       |                       |

|            | •                                        |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                        |                                                                 |                                 |                       |                          |                       |                       |

|            | •                                        |                                                                 | (2)                             |                       |                          |                       |                       |

|            | 00010 = Ch                               | nannel 0 positive i<br>nannel 0 positive i                      | input is AN2 <sup>(3)</sup>     |                       |                          |                       |                       |

|            |                                          | nannel 0 positive i                                             |                                 |                       |                          |                       |                       |

| bit 7      |                                          | nannel 0 Negative                                               | •                               | r Samnle MI IX        | Δ hit                    |                       |                       |

|            | CINIA. OI                                | lanner o Negative                                               | •                               |                       | A DIL                    |                       |                       |

|            | 1 = Channell                             | 1 0 negative input                                              | is AN1(1)                       |                       |                          |                       |                       |

|            |                                          | el 0 negative input<br>el 0 negative input                      |                                 |                       |                          |                       |                       |

| bit 6-5    | 0 = Channe                               | el 0 negative input<br>el 0 negative input<br>ented: Read as '0 | is Vrefl                        |                       |                          |                       |                       |

|            | 0 = Channe<br>Unimpleme<br>AN0 through A | el 0 negative input                                             | is VREFL<br>,'<br>ed when compa |                       |                          |                       |                       |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

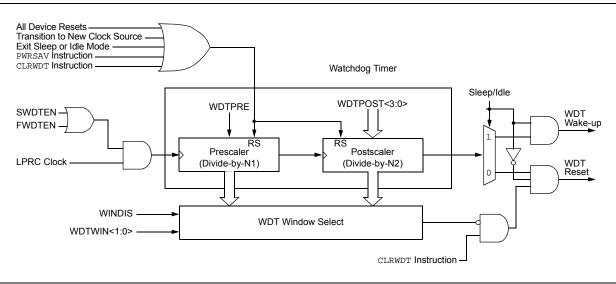

### 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |