Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502-h-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

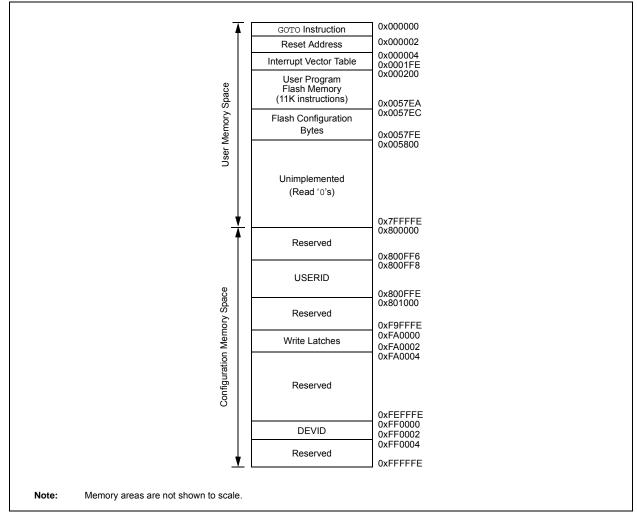

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                       | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3               | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|----------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|---------------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                        | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0>          |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>           |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _                   | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                              |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |                     |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                        | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0>          |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                            | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0> PPRE<1:0> |       |        | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN                                        | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _                   | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | 58 SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |            |              | 0000        |            |        |       |                     |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-1        | R/W-0                                                    | R/W-0                                                                | U-0          | U-0              | U-0              | U-0                | U-0    |  |  |  |  |  |

|--------------|----------------------------------------------------------|----------------------------------------------------------------------|--------------|------------------|------------------|--------------------|--------|--|--|--|--|--|

| GIE          | DISI                                                     | SWTRAP                                                               |              |                  |                  | _                  |        |  |  |  |  |  |

| bit 15       |                                                          |                                                                      |              |                  |                  |                    | bit 8  |  |  |  |  |  |

|              |                                                          |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| U-0          | U-0                                                      | U-0                                                                  | U-0          | U-0              | R/W-0            | R/W-0              | R/W-0  |  |  |  |  |  |

|              | —                                                        |                                                                      |              |                  | INT2EP           | INT1EP             | INT0EP |  |  |  |  |  |

| bit 7        |                                                          |                                                                      |              |                  |                  |                    | bit C  |  |  |  |  |  |

| Legend:      |                                                          |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| R = Readab   | le bit                                                   | W = Writable                                                         | bit          | U = Unimpler     | mented bit, read | l as '0'           |        |  |  |  |  |  |

| -n = Value a |                                                          | '1' = Bit is set                                                     |              | '0' = Bit is cle |                  | x = Bit is unknown |        |  |  |  |  |  |

|              |                                                          |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| bit 15       | GIE: Global                                              | Interrupt Enable                                                     | e bit        |                  |                  |                    |        |  |  |  |  |  |

|              | 1 = Interrupt                                            | 1 = Interrupts and associated IE bits are enabled                    |              |                  |                  |                    |        |  |  |  |  |  |

|              | 0 = Interrupts are disabled, but traps are still enabled |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| bit 14       | DISI: DISI Instruction Status bit                        |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

|              |                                                          | 1 = DISI instruction is active<br>0 = DISI instruction is not active |              |                  |                  |                    |        |  |  |  |  |  |

| bit 13       | SWTRAP: Software Trap Status bit                         |                                                                      |              |                  |                  |                    |        |  |  |  |  |  |

|              |                                                          | Software trap is enabled                                             |              |                  |                  |                    |        |  |  |  |  |  |

| bit 12-3     | Unimpleme                                                | nted: Read as '                                                      | 0'           |                  |                  |                    |        |  |  |  |  |  |

| bit 2        | INT2EP: Ext                                              | ternal Interrupt 2                                                   | 2 Edge Detec | t Polarity Selec | t bit            |                    |        |  |  |  |  |  |

|              |                                                          | on negative edg                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| bit 1        | INT1EP: Ext                                              | <b>NT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit   |              |                  |                  |                    |        |  |  |  |  |  |

|              |                                                          | on negative edg                                                      |              |                  |                  |                    |        |  |  |  |  |  |

| bit 0        | INTOEP: Ext                                              | ternal Interrupt C                                                   | Edge Detec   | t Polarity Selec | t bit            |                    |        |  |  |  |  |  |

|              |                                                          | on negative edg                                                      |              |                  |                  |                    |        |  |  |  |  |  |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0                               | U-0                                                                                                      | U-0                     | U-0            | U-0                                | U-0  | U-0                | U-0   |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|----------------|------------------------------------|------|--------------------|-------|--|--|--|--|--|

| -                                 | —                                                                                                        | —                       | —              | —                                  | —    | —                  | —     |  |  |  |  |  |

| bit 15                            |                                                                                                          |                         |                |                                    |      |                    | bit 8 |  |  |  |  |  |

| U-0                               | U-0                                                                                                      | U-0                     | U-0            | R-1                                | R-1  | R-1                | R-1   |  |  |  |  |  |

| _                                 | _                                                                                                        | _                       | _              |                                    | LSTC | H<3:0>             |       |  |  |  |  |  |

| bit 7                             |                                                                                                          |                         |                |                                    |      |                    | bit 0 |  |  |  |  |  |

| Legend:                           |                                                                                                          |                         |                |                                    |      |                    |       |  |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                          |                         | bit            | U = Unimplemented bit, read as '0' |      |                    |       |  |  |  |  |  |

| -n = Value a                      | at POR                                                                                                   | '1' = Bit is set        |                | '0' = Bit is cle                   | ared | x = Bit is unknown |       |  |  |  |  |  |

|                                   |                                                                                                          |                         |                |                                    |      |                    |       |  |  |  |  |  |

| bit 15-4                          | Unimplemen                                                                                               | ted: Read as '          | 0'             |                                    |      |                    |       |  |  |  |  |  |

| bit 3-0                           | LSTCH<3:0>                                                                                               | : Last DMAC C           | hannel Active  | e Status bits                      |      |                    |       |  |  |  |  |  |

|                                   | 1111 = No DI<br>1110 = Rese                                                                              | MA transfer has<br>rved | s occurred sir | nce system Res                     | set  |                    |       |  |  |  |  |  |

|                                   | •                                                                                                        | •                       |                |                                    |      |                    |       |  |  |  |  |  |

|                                   | •                                                                                                        |                         |                |                                    |      |                    |       |  |  |  |  |  |

|                                   | •                                                                                                        |                         |                |                                    |      |                    |       |  |  |  |  |  |

|                                   |                                                                                                          | data transfer wa        |                |                                    |      |                    |       |  |  |  |  |  |

|                                   | 0010 = Last data transfer was handled by Channel 2<br>0001 = Last data transfer was handled by Channel 1 |                         |                |                                    |      |                    |       |  |  |  |  |  |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

## 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

## REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ole bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

## bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

| U-0              | R/W-0                                                                           | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|--|--|

| _                | CLSRC4                                                                          | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |

| bit 15           |                                                                                 |                                    | •               |                   |                                |                      | bit 8           |  |  |  |  |  |

|                  | <b>D</b> 4 4                                                                    | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | <b>D</b> 444.0  |  |  |  |  |  |

| R/W-1            | R/W-1                                                                           | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                                         | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |  |

|                  |                                                                                 |                                    |                 |                   |                                |                      | DI              |  |  |  |  |  |

| Legend:          |                                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

| R = Readable     | bit                                                                             | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |  |  |

| -n = Value at I  | POR                                                                             | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |  |  |

|                  |                                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

| bit 15           | Unimplemen                                                                      | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |  |  |

| bit 14-10        | CLSRC<4:0>: Current-Limit Control Signal Source Select for PWM Generator # bits |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 11111 = Fault 32                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 11110 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  |                                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | •                                                                               |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 01100 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 01011 = Comparator 4                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 01011 = Op Amp/Comparator 3                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 01001 = Op Amp/Comparator 2                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 01000 = Op Amp/Comparator 1                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00111 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00110 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00101 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00100 = Reserved                                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00011 = Fault 4                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00010 <b>= Fau</b>                                                              |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00001 = Fault 2                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 00000 = Fault 1 (default)                                                       |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

| bit 9            | CLPOL: Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup>            |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | 0 = The selec                                                                   | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |  |  |

| bit 8            | CLMOD: Cur                                                                      | rent-Limit Mode                    | e Enable for P  | WM Generator      | r # bit                        |                      |                 |  |  |  |  |  |

|                  |                                                                                 | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |  |  |

|                  | ne PWMLOCK                                                                      |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |  |

| the              | unlock sequen                                                                   | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |  |  |

|                  |                                                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |

## REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R-0, HSC      | R-0, HSC                                                                  | U-0          | U-0        | U-0          | R/C-0, HS        | R-0, HSC                              | R-0, HSC |  |

|---------------|---------------------------------------------------------------------------|--------------|------------|--------------|------------------|---------------------------------------|----------|--|

| ACKSTAT       | TRSTAT                                                                    | _            | _          | —            | BCL              | GCSTAT                                | ADD10    |  |

| bit 15        |                                                                           |              |            |              |                  |                                       | bit 8    |  |

|               |                                                                           |              |            |              |                  |                                       |          |  |

| R/C-0, HS     | R/C-0, HS                                                                 | R-0, HSC     | R/C-0, HSC | R/C-0, HSC   | R-0, HSC         | R-0, HSC                              | R-0, HSC |  |

| IWCOL         | I2COV                                                                     | D_A          | Р          | S            | R_W              | RBF                                   | TBF      |  |

| bit 7         |                                                                           |              |            |              |                  |                                       | bit 0    |  |

|               |                                                                           |              |            |              |                  |                                       |          |  |

| Legend:       |                                                                           | C = Clearab  | le bit     | HS = Hardwa  | re Settable bit  | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readabl   | e bit                                                                     | W = Writable | e bit      | U = Unimplem | nented bit, read | as '0'                                |          |  |

| -n = Value at | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |            |              |                  |                                       |          |  |

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

## 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

## REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |       | Ву    | /te 3                                   |       |       |       |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|                                    |       |       | Ву    | /te 2                                   |       |       |       |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

## BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                                   |       |                  | B     | yte 5                              |       |                 |       |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                                   |       |                  |       | yte 4                              |       |                 |       |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |

|                                   |       |                  |       |                                    |       |                 |       |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

NOTES:

## REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

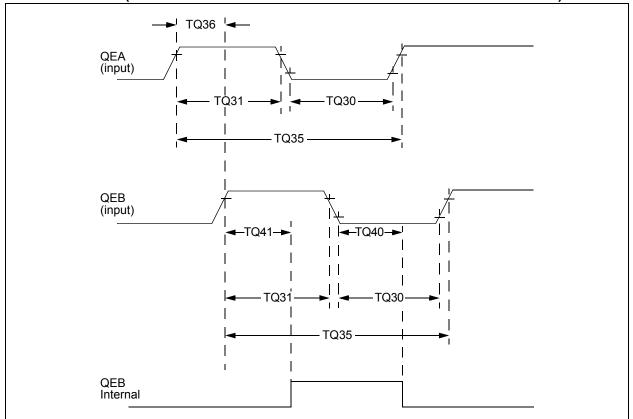

## FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |                                                         |  |

|--------------------|--------|-------------------------------------------------------------|-------------------------------------------------------|-------|------------|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | nbol Characteristic <sup>(1)</sup> Typ. <sup>(2)</sup> Max. |                                                       | Units | Conditions |                                                         |  |

| TQ30               | TQUL   | Quadrature Input Low Time                                   | 6 Tcy                                                 |       | ns         |                                                         |  |

| TQ31               | TQUH   | Quadrature Input High Time                                  | 6 Tcy                                                 | —     | ns         |                                                         |  |

| TQ35               | TQUIN  | Quadrature Input Period                                     | 12 TCY                                                | _     | ns         |                                                         |  |

| TQ36               | TQUP   | Quadrature Phase Period                                     | 3 TCY                                                 | —     | ns         |                                                         |  |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter           | 3 * N * Tcy                                           | —     | ns         | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter          | 3 * N * Tcy                                           | —     | ns         | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

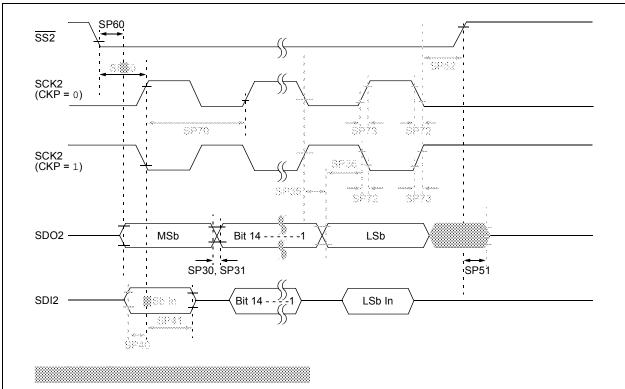

## FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

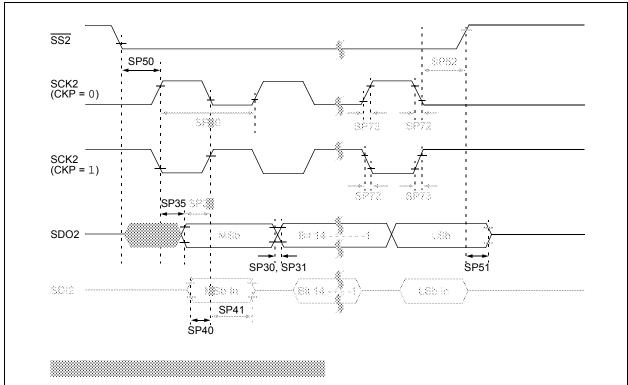

## FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-46:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                       |       |                                |  |

|--------------------|-----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max.                  | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCK1 Input<br>Frequency                 | —                                                                                                                                                                                                                                                                                     | _                   | Lesser of<br>FP or 11 | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCK1 Input Fall Time                            | _                                                                                                                                                                                                                                                                                     | _                   | _                     | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCK1 Input Rise Time                            | —                                                                                                                                                                                                                                                                                     | _                   | _                     | ns    | See Parameter DO31 (Note 4)    |  |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                      | —                                                                                                                                                                                                                                                                                     | —                   | —                     | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                      | —                                                                                                                                                                                                                                                                                     | _                   | —                     | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge       | —                                                                                                                                                                                                                                                                                     | 6                   | 20                    | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge    | 30                                                                                                                                                                                                                                                                                    | —                   | —                     | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge      | 30                                                                                                                                                                                                                                                                                    | —                   | —                     | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge       | 30                                                                                                                                                                                                                                                                                    | _                   | —                     | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS1}$ ↓ to SCK1 ↑ or SCK1 ↓<br>Input | 120                                                                                                                                                                                                                                                                                   | —                   | —                     | ns    |                                |  |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance          | 10                                                                                                                                                                                                                                                                                    | —                   | 50                    | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                           | 1.5 Tcy + 40                                                                                                                                                                                                                                                                          | _                   | _                     | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDO1 Data Output Valid after                    | —                                                                                                                                                                                                                                                                                     | —                   | 50                    | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| DC CHARACTERISTICS           |      |                                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |           |     |       |                                                                    |  |

|------------------------------|------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------|--------------------------------------------------------------------|--|

| Param. Symbol Characteristic |      |                                                             | Min.                                                                                                                                   | Тур. Мах. |     | Units | Conditions                                                         |  |

| HDO10                        | Vol  | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                        | —         | 0.4 | V     | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)                                 |  |

|                              |      | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | —                                                                                                                                      | —         | 0.4 | V     | IOL ≤ 8 mA, VDD = 3.3V<br>(Note 1)                                 |  |

| HDO20                        | Vон  | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                    | —         | —   | V     | IOH ≥ -10 mA, VDD = 3.3V<br>(Note 1)                               |  |

|                              |      | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                    | —         | —   | V     | ІОн ≥ 15 mA, VDD = 3.3V<br>(Note 1)                                |  |

| HDO20A                       | Vон1 | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5                                                                                                                                    | —         | —   | V     | IOH ≥ -3.9 mA, VDD = 3.3V<br>(Note 1)                              |  |

|                              |      |                                                             | 2.0                                                                                                                                    | —         | —   |       | $IOH \ge -3.7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>(Note 1)  |  |

|                              |      |                                                             | 3.0                                                                                                                                    | —         | —   |       | IOH ≥ -2 mA, VDD = 3.3V<br>(Note 1)                                |  |

|                              |      | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5                                                                                                                                    | _         | _   | V     | IOH ≥ -7.5 mA, VDD = 3.3V<br>(Note 1)                              |  |

|                              |      |                                                             | 2.0                                                                                                                                    | _         | _   |       | $IOH \ge -6.8 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$<br>(Note 1) |  |

|                              |      |                                                             | 3.0                                                                                                                                    | _         | —   |       | IOH ≥ -3 mA, VDD = 3.3V<br>(Note 1)                                |  |

## TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

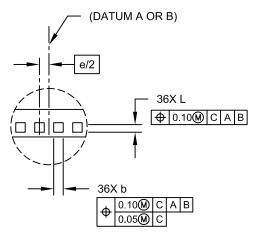

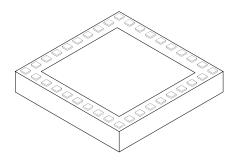

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | Units | N        | <b>ILLIMETER</b> | s     |  |  |  |

|-------------------------|-------|----------|------------------|-------|--|--|--|

| Dimension               | MIN   | NOM      | MAX              |       |  |  |  |

| Number of Pins          | Ν     | 36       |                  |       |  |  |  |

| Number of Pins per Side | ND    |          | 10               |       |  |  |  |

| Number of Pins per Side | NE    |          | 8                |       |  |  |  |

| Pitch                   | е     |          | 0.50 BSC         |       |  |  |  |

| Overall Height          | Α     | 0.80     | 0.90             | 1.00  |  |  |  |

| Standoff                | A1    | 0.025    | -                | 0.075 |  |  |  |

| Overall Width           | E     | 5.00 BSC |                  |       |  |  |  |

| Exposed Pad Width       | E2    | 3.60     | 3.75             | 3.90  |  |  |  |

| Overall Length          | D     | 5.00 BSC |                  |       |  |  |  |

| Exposed Pad Length      | D2    | 3.60     | 3.75             | 3.90  |  |  |  |

| Contact Width           | b     | 0.20     | 0.25             | 0.30  |  |  |  |

| Contact Length          | L     | 0.20     | 0.25             | 0.30  |  |  |  |

| Contact-to-Exposed Pad  | К     | 0.20     | -                | -     |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2