Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K × 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

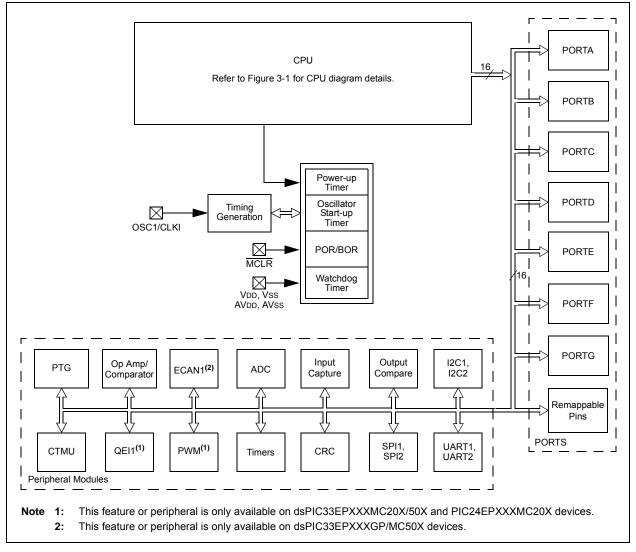

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

| TABLE 1-1:         PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |  |  |

|--------------------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name <sup>(4)</sup>                                | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |  |  |

| U2CTS                                                  | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |  |  |

| U2RTS                                                  | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |  |  |

| U2RX                                                   | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |  |  |

| U2TX                                                   | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |  |  |

| BCLK2                                                  | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |  |  |

| SCK1                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |  |  |

| SDI1                                                   | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |  |  |

| SDO1                                                   | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |  |  |

| SS1                                                    | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |  |

| SCK2                                                   | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |  |  |

| SDI2                                                   | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |  |  |

| SDO2                                                   | 0           | _              | Yes | SPI2 data out.                                                                   |  |  |  |  |  |  |

| SS2                                                    | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |  |

| SCL1                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |  |  |

| SDA1                                                   | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |  |  |

| ASCL1                                                  | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |  |  |

| ASDA1                                                  | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |  |  |

| SCL2                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |  |  |

| SDA2                                                   | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |  |  |

| ASCL2                                                  | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |  |  |

| ASDA2                                                  | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |  |  |

| TMS <sup>(5)</sup>                                     | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |  |  |

| TCK                                                    | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |  |  |

| TDI                                                    | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |  |  |

| TDO                                                    | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |  |  |

| C1RX <sup>(2)</sup>                                    | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |  |  |

| C1TX <sup>(2)</sup>                                    | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>              | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>              | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                                 | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                           | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                             | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                             | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                                  | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                                  | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |  |  |

| INDX1 <sup>(1)</sup>                                   | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |  |  |

| HOME1 <sup>(1)</sup>                                   | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |  |  |

| QEA1 <sup>(1)</sup>                                    | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |  |

| QEB1 <sup>(1)</sup>                                    | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |  |  |

|                                                        | Ι           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                                 | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |  |  |

|                                                        | 0           | <br>ompatible  | 162 |                                                                                  |  |  |  |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4         | -16:  | QEI1   | REGR              |          | P FOR d    | SPIC33E    | PXXXMO   | 20X/50)  | ( AND PI    | C24EP) |        | 20X DE     | VICES O  | NLY    | 1      |        |        | r             |

|-----------------|-------|--------|-------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  | —                 | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2  | QCAPEN | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4  | _      | _                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6  |        |                   |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8  |        | POSCNT<31:16> 000 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| POS1HLD         | 01CA  |        | POSHLD<15:0> 000  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| VEL1CNT         | 01CC  |        | VELCNT<15:0> 000  |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1TMRL        | 01CE  |        | INTTMR<15:0> 00   |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1TMRH        | 01D0  |        |                   |          |            |            |          |          | INTTMR<31:  | 6>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDL        | 01D2  |        |                   |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4  |        |                   |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6  |        |                   |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8  |        |                   |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA  |        |                   |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC  |        |                   |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                   |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE  |        | QEIGEC<31:16> 000 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1ICH         | 01DE  |        |                   |          |            |            |          |          | QEIIC<31:16 | š>     |        |            |          |        |        |        |        | 0000          |

| QEI1LECL        | 01E0  |        |                   |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2  |        |                   |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11       | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-----------|--------|--------------|--------|-------|-------|-------|-------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |        |           |        | NT1R<6:0>    |        |       |       |       |             |       |       |            |       |       | _     | 0000          |

| RPINR1       | 06A2  |        | —      | —         | -      |              | -      |       |       | -     | INT2R<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR3       | 06A6  | -      | _      | _         | _      | _            | _      | _     | _     | _     | T2CKR<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR7       | 06AE  | _      |        | IC2R<6:0> |        |              |        |       |       | —     |             |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |        |           |        | IC4R<6:0>    |        |       |       | —     |             |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _      | _         | —      | _            | _      | _     | _     | —     |             |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8  | _      |        |           | l      | =LT2R<6:0>   |        |       |       | —     | FLT1R<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR14      | 06BC  | _      |        |           | (      | QEB1R<6:0    | >      |       |       | —     | QEA1R<6:0>  |       |       |            |       |       |       | 0000          |

| RPINR15      | 06BE  | _      |        |           | Н      | OME1R<6:0    | )>     |       |       | —     | INDX1R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR18      | 06C4  | _      | _      | _         | —      | —            | _      | _     | _     | —     | U1RXR<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR19      | 06C6  | _      | _      | _         | _      | _            | _      | _     | _     | —     |             |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |        | •         | S      | CK2INR<6:0   | )>     |       |       | _     |             |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      |           | _      | _            | _      | _     | _     | _     |             |       |       |            |       |       | 0000  |               |

| RPINR37      | 06EA  | _      |        |           | S      | SYNCI1R<6:0> |        |       |       |       |             | _     | 0000  |            |       |       |       |               |

| RPINR38      | 06EC  | _      |        |           | DI     | CMP1R<6:     | 0>     |       |       | _     |             |       |       |            |       | _     | 0000  |               |

| RPINR39      | 06EE  | _      |        |           | DT     | CMP3R<6:     | 0>     |       |       | —     |             |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

## 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

## 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

# 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

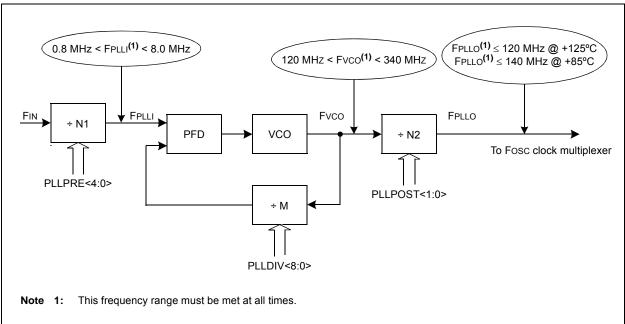

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

## EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

# FIGURE 9-2: PLL BLOCK DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER                    | TU-5: PIVID6                       | . PERIPHER       |                           | DISABLE C         | UNIROL RE             | GISIER 6              |                       |

|-----------------------------|------------------------------------|------------------|---------------------------|-------------------|-----------------------|-----------------------|-----------------------|

| U-0                         | U-0                                | U-0              | U-0                       | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| —                           | —                                  | —                | —                         | —                 | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15                      |                                    |                  |                           |                   |                       |                       | bit 8                 |

|                             |                                    |                  |                           |                   |                       |                       |                       |

| U-0                         | U-0                                | U-0              | U-0                       | U-0               | U-0                   | U-0                   | U-0                   |

|                             |                                    |                  |                           |                   |                       |                       |                       |

| bit 7                       |                                    |                  |                           |                   |                       |                       | bit 0                 |

|                             |                                    |                  |                           |                   |                       |                       |                       |

| Legend:                     |                                    |                  |                           |                   |                       |                       |                       |

| R = Readab                  | R = Readable bit W = Writable bit  |                  |                           | U = Unimplen      | nented bit, read      | l as '0'              |                       |

| -n = Value a                | -n = Value at POR '1' = Bit is set |                  |                           | '0' = Bit is clea | ared                  | x = Bit is unkr       | iown                  |

|                             |                                    |                  |                           |                   |                       |                       |                       |

| bit 15-11                   | Unimplement                        | ted: Read as '   | כ'                        |                   |                       |                       |                       |

| bit 10                      | PWM3MD: P\                         | NM3 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|                             | 1 = PWM3 mo                        | odule is disable | ed                        |                   |                       |                       |                       |

|                             | 0 = PWM3 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 9                       | PWM2MD: P\                         | NM2 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

| 1 = PWM2 module is disabled |                                    |                  |                           |                   |                       |                       |                       |

|                             | 0 = PWM2 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 8                       | PWM1MD: P\                         | NM1 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|                             |                                    | odule is disable |                           |                   |                       |                       |                       |

|                             | 0 = PWM1 mo                        | odule is enable  | d                         |                   |                       |                       |                       |

| bit 7-0                     | Unimplement                        | ted: Read as '   | כ'                        |                   |                       |                       |                       |

# REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | TRGC  | MP<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | TRGC  | MP<7:0>           |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

# REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | R/W-x                             | U-0                                     | U-0             | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |  |  |

|---------------|-----------------------------------|-----------------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| _             | WAKFIL                            | _                                       | —               |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |  |  |

| bit 15        |                                   |                                         |                 |                  |                  |                 | bit     |  |  |  |  |  |  |

| R/W-x         | R/W-x                             | R/W-x                                   | R/W-x           | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |  |  |

|               |                                   |                                         |                 | 1                |                  | 1               |         |  |  |  |  |  |  |

| SEG2PHTS      | SAM                               | SEG1PH2                                 | SEG1PH1         | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |  |  |

| bit 7         |                                   |                                         |                 |                  |                  |                 | bit     |  |  |  |  |  |  |

| Legend:       |                                   |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

| R = Readable  | e bit                             | W = Writable                            | bit             | U = Unimpler     | nented bit, read | l as '0'        |         |  |  |  |  |  |  |

| -n = Value at | POR                               | '1' = Bit is set                        |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

|               |                                   |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 15        | Unimplemer                        | nted: Read as '                         | 0'              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 14        |                                   | lect CAN Bus L                          |                 | Vake-up bit      |                  |                 |         |  |  |  |  |  |  |

|               |                                   | N bus line filter<br>line filter is not |                 | e-up             |                  |                 |         |  |  |  |  |  |  |

| bit 13-11     | Unimplemer                        | nted: Read as '                         | 0'              |                  |                  |                 |         |  |  |  |  |  |  |

| bit 10-8      | SEG2PH<2:0>: Phase Segment 2 bits |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 111 = Length                      | -                                       |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               |                                   |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 000 = Length                      | n is 1 x Tq                             |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 7         |                                   | Phase Segmer                            | nt 2 Time Sele  | ct bit           |                  |                 |         |  |  |  |  |  |  |

|               | 1 = Freely pr<br>0 = Maximun      | ogrammable<br>n of SEG1PHx I            | oits or Informa | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |  |  |  |  |  |  |

| bit 6         | SAM: Sample                       | e of the CAN B                          | us Line bit     |                  |                  | -               |         |  |  |  |  |  |  |

|               |                                   | is sampled three<br>is sampled once     |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 5-3       | SEG1PH<2:0                        | 0>: Phase Segr                          | nent 1 bits     | -                |                  |                 |         |  |  |  |  |  |  |

|               | 111 = Length                      | n is 8 x Tq                             |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 000 = Length                      |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 2-0       |                                   | >: Propagation                          | Time Segmen     | t bits           |                  |                 |         |  |  |  |  |  |  |

|               | 111 = Length                      | n is 8 x Tq                             |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               |                                   |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | •                                 |                                         |                 |                  |                  |                 |         |  |  |  |  |  |  |

## REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------|------|------|------|----------|----------|---------|

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _    |      |      |      | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |      |      |      |      |          |          | bit 8   |

|        |      |      |      |      |          |          |         |

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | 0-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | _   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

# Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |

|-----------------|-------------|-------|-------|

| value           | CH1         | CH2   | CH3   |

| 11              | AN9         | AN10  | AN11  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |

| 0x              | Vrefl       | Vrefl | VREFL |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |

|----------------|-------------|---------|---------|

|                | CH1         | CH2     | CH3     |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           |         | ADC Channel |       |

|-----------------|---------|-------------|-------|

| value           | CH1     | CH2         | CH3   |

| 11              | AN9     | AN10        | AN11  |

| 10 <b>(1,2)</b> | OA3/AN6 | AN7         | AN8   |

| 0x              | VREFL   | VREFL       | Vrefl |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# APPENDIX A: REVISION HISTORY

## **Revision A (April 2011)**

This is the initial released version of the document.

## Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory<br>Organization"                                             | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program<br>Memory"                                            | Updated "one word" to "two words" in the first paragraph of <b>Section 5.2 "RTSP Operation"</b> .                                                                                                                                                                                                                       |

| Section 9.0 "Oscillator<br>Configuration"                                        | Updated the PLL Block Diagram (see Figure 9-2).<br>Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL<br>(FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                 |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                            | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |