#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (10.7K × 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | (s)                            |                               |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

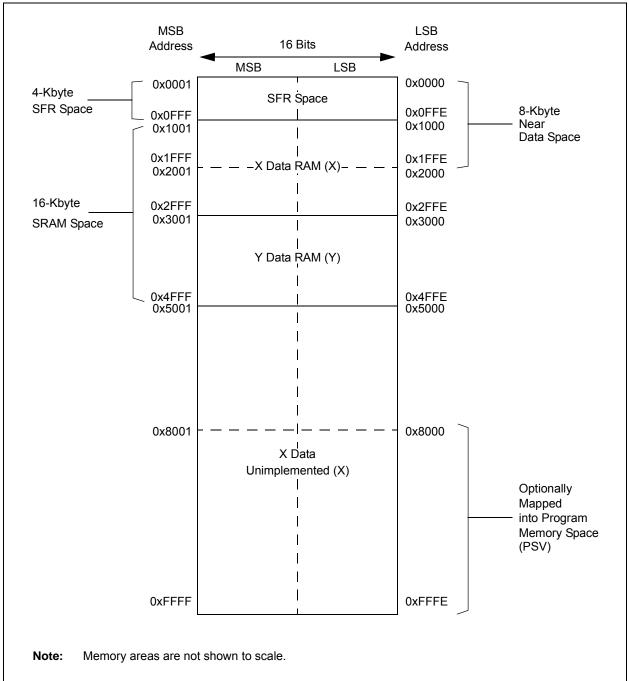

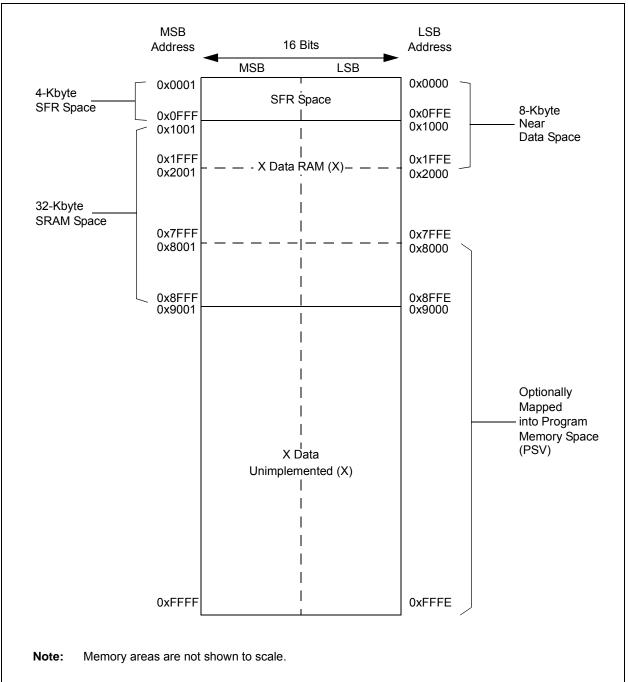

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

# TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | —     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | -      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

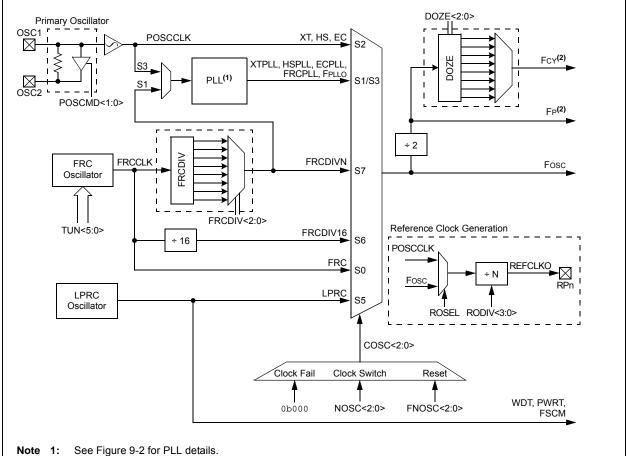

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

# FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

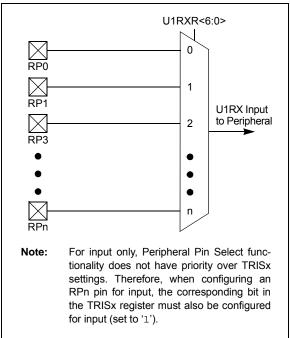

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         | _   | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         | _   | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

## TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

## REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ole bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

# bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

# REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

# REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6 | RXOVF5         | RXOVF4            | RXOVF3         | RXOVF2             | RXOVF1 | RXOVF0 |

|---------|--------|----------------|-------------------|----------------|--------------------|--------|--------|

| bit 7   |        |                |                   |                |                    |        | bit 0  |

|         |        |                |                   |                |                    |        |        |

| Legend: |        | C = Writable b | oit, but only '0' | can be writter | n to clear the bit |        |        |

| Legend:           | C = Writable bit, but only '0' | can be written to clear the bit |                    |

|-------------------|--------------------------------|---------------------------------|--------------------|

| R = Readable bit  | W = Writable bit               | U = Unimplemented bit, read     | l as '0'           |

| -n = Value at POR | '1' = Bit is set               | '0' = Bit is cleared            | x = Bit is unknown |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                       |                    |  |  |  |

|-------------------|----------------------------------------------------------------|-----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit | t, read as '0'     |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                                          | ,_, ., ., ., .,                     | -,-,-,                |                          |                  |                 |                 |  |  |  |  |

|---------------|--------------------------------------------|-------------------------------------|-----------------------|--------------------------|------------------|-----------------|-----------------|--|--|--|--|

| R/W-0         | R-0                                        | R-0                                 | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENn         | TXABTn                                     | TXLARBn                             | TXERRn                | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |  |

| bit 15        |                                            |                                     |                       |                          |                  |                 | bit 8           |  |  |  |  |

| R/W-0         | R-0                                        | R-0                                 | R-0                   | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                      | TXLARBm <sup>(1)</sup>              | TXERRm <sup>(1)</sup> | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |  |

| bit 7         |                                            |                                     |                       |                          |                  |                 | bit C           |  |  |  |  |

| Legend:       |                                            |                                     |                       |                          |                  |                 |                 |  |  |  |  |

| R = Readabl   | le bit                                     | W = Writable                        | bit                   | U = Unimpler             | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value at | t POR                                      | '1' = Bit is set                    |                       | '0' = Bit is cle         | ared             | x = Bit is unki | nown            |  |  |  |  |

| bit 15-8      | See Definitio                              | n for bits<7:0>,                    | Controls Buffe        | <u>er n</u>              |                  |                 |                 |  |  |  |  |

| bit 7         |                                            | RX Buffer Sele                      |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            | RBn is a transm                     |                       |                          |                  |                 |                 |  |  |  |  |

|               | 0 = Buffer TR                              | 0 = Buffer TRBn is a receive buffer |                       |                          |                  |                 |                 |  |  |  |  |

| bit 6         | TXABTm: Message Aborted bit <sup>(1)</sup> |                                     |                       |                          |                  |                 |                 |  |  |  |  |

|               | 1 = Message was aborted                    |                                     |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            | completed tran                      |                       |                          |                  |                 |                 |  |  |  |  |

| bit 5         |                                            | Message Lost A                      |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            | lost arbitration did not lose ar    |                       |                          |                  |                 |                 |  |  |  |  |

| bit 4         | TXERRm: Er                                 | ror Detected D                      | uring Transmis        | ssion bit <sup>(1)</sup> |                  |                 |                 |  |  |  |  |

|               |                                            | or occurred wh<br>or did not occu   |                       |                          |                  |                 |                 |  |  |  |  |

| bit 3         |                                            | essage Send F                       |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            | 0                                   | •                     | bit automatic            | ally clears wher | n the message   | is successfully |  |  |  |  |

|               | 0 = Clearing                               | the bit to '0' wh                   | nile set reques       | ts a message             | abort            |                 |                 |  |  |  |  |

| bit 2         | RTRENm: Au                                 | uto-Remote Tra                      | Insmit Enable         | bit                      |                  |                 |                 |  |  |  |  |

|               |                                            | emote transmit<br>emote transmit    |                       |                          |                  |                 |                 |  |  |  |  |

| bit 1-0       | TXmPRI<1:0                                 | >: Message Tra                      | ansmission Pri        | iority bits              |                  |                 |                 |  |  |  |  |

|               | 11 = Highest                               | message prior                       | ity                   |                          |                  |                 |                 |  |  |  |  |

|               | 0                                          | ermediate mes                       |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            | ermediate mess<br>message priori    |                       |                          |                  |                 |                 |  |  |  |  |

|               |                                            |                                     | -                     |                          |                  |                 |                 |  |  |  |  |

| Note 1: ⊤     | his bit is cleared                         | when TXREQ                          | s set.                |                          |                  |                 |                 |  |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x         | R/W-x         | R/W-x                                           | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

|---------------|---------------|-------------------------------------------------|---------------|------------------------------------|-------|--------------------|-------|--|--|--|--|

| EID5          | EID4          | EID3                                            | EID2          | EID1                               | EID0  | RTR                | RB1   |  |  |  |  |

| bit 15        |               |                                                 |               |                                    |       |                    | bit 8 |  |  |  |  |

|               |               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| U-x           | U-x           | U-x                                             | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

| —             | —             | —                                               | RB0           | DLC3                               | DLC2  | DLC1               | DLC0  |  |  |  |  |

| bit 7         |               |                                                 |               |                                    |       |                    | bit 0 |  |  |  |  |

| Lonondi       |               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| Legend:       | l. h.:.       |                                                 | L.11          |                                    |       | -l (O)             |       |  |  |  |  |

| R = Readab    |               | W = Writable                                    |               | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |  |

| -n = Value a  | t POR         | '1' = Bit is set                                |               | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |  |  |

|               |               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| bit 15-10     | EID<5:0>: E   | xtended Identifi                                | er bits       |                                    |       |                    |       |  |  |  |  |

| bit 9         | RTR: Remot    | RTR: Remote Transmission Request bit            |               |                                    |       |                    |       |  |  |  |  |

|               | When IDE = 1: |                                                 |               |                                    |       |                    |       |  |  |  |  |

|               | •             | 1 = Message will request remote transmission    |               |                                    |       |                    |       |  |  |  |  |

|               |               | 0 = Normal message                              |               |                                    |       |                    |       |  |  |  |  |

|               |               | <u>When IDE = 0:</u><br>The RTR bit is ignored. |               |                                    |       |                    |       |  |  |  |  |

| <b>h</b> :+ 0 |               |                                                 |               |                                    |       |                    |       |  |  |  |  |

| bit 8         |               | RB1: Reserved Bit 1                             |               |                                    |       |                    |       |  |  |  |  |

|               |               | User must set this bit to '0' per CAN protocol. |               |                                    |       |                    |       |  |  |  |  |

| bit 7-5       | •             | Unimplemented: Read as '0'                      |               |                                    |       |                    |       |  |  |  |  |

| bit 4         | RB0: Reserv   |                                                 | <b></b>       |                                    |       |                    |       |  |  |  |  |

|               | User must se  | et this bit to '0' p                            | per CAN proto | ocol.                              |       |                    |       |  |  |  |  |

| hit 2 0       |               | Jota Longth Co.                                 | da hita       |                                    |       |                    |       |  |  |  |  |

### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

# BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|-------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                   |       |                  | Ву    | /te 1                              |       |                 |       |  |

| bit 15            |       |                  |       |                                    |       |                 | bit 8 |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                   |       |                  | Ву    | rte 0                              |       |                 |       |  |

| bit 7             |       |                  |       |                                    |       |                 | bit 0 |  |

| Legend:           |       |                  |       |                                    |       |                 |       |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unkr | nown  |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

# TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

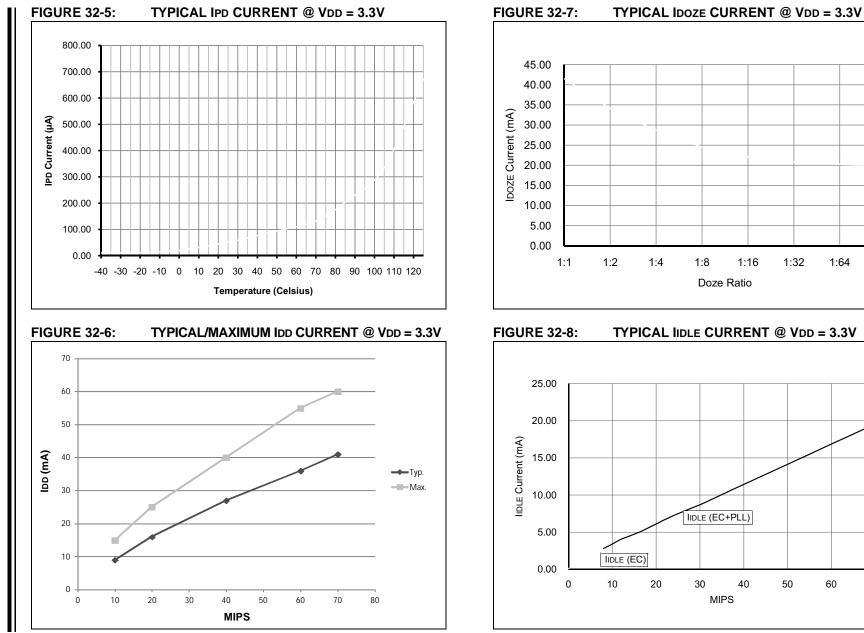

# **30.1 DC Characteristics**

|                |                         |                       | Maximum MIPS                                                          |  |

|----------------|-------------------------|-----------------------|-----------------------------------------------------------------------|--|

| Characteristic | VDD Range<br>(in Volts) | Temp Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |  |

|                |                         |                       | 70                                                                    |  |

| —              |                         |                       | 60                                                                    |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min.        | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | _           | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O |             |      | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                   | Symbol | Тур. | Max. | Unit | Notes |

|--------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN           | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10 mm | θJA    | 48.3 | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN 6x6 mm   | θJA    | 41   | -    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN           | θJA    | 29.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10 mm | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin VTLA 6x6 mm   | θJA    | 25.2 | _    | °C/W | 1     |

| Package Thermal Resistance, 36-Pin VTLA 5x5 mm   | θJA    | 28.5 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S         | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP          | θJA    | 71.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC          | θJA    | 69.7 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP         | θJA    | 60.0 | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

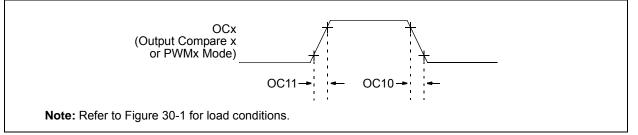

# FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

## TABLE 30-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------|-------------------------------------------------------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                  | Тур. | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                     |      | _    | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                     | _    | —    | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

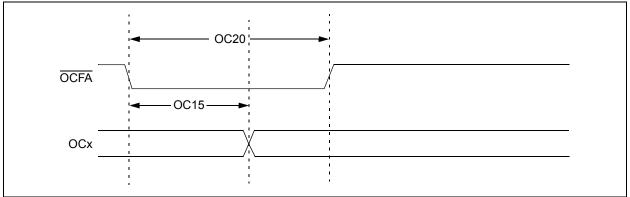

## FIGURE 30-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |          |       |            |  |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|------|----------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                  | Тур. | Max.     | Units | Conditions |  |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change | —                                                     | _    | Tcy + 20 | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | TCY + 20                                              |      | —        | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

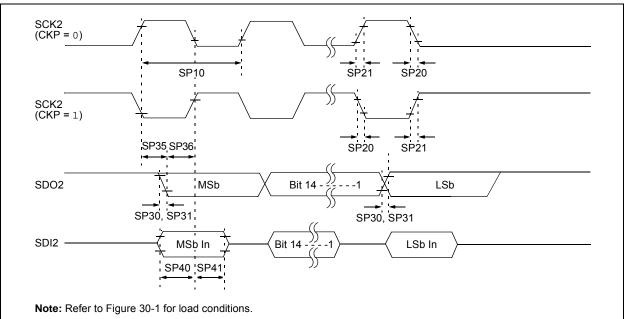

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |  |

|--------------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                       | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |  |  |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                     | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | _                                                     | 6                   | 20   | ns    |                             |  |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                    | —                   | _    | ns    |                             |  |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                    | —                   | _    | ns    |                             |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                    | —                   |      | ns    |                             |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

# TABLE 30-38:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |                          |       |                             |  |

|--------------------|-----------------------|-------------------------------------------------|-------------------------------------------------------|---------------------|--------------------------|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                  | Typ. <sup>(2)</sup> | Max.                     | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency                 | -                                                     | —                   | Lesser<br>of FP<br>or 11 | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCK2 Input Fall Time                            |                                                       | _                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCK2 Input Rise Time                            | _                                                     | _                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | _                                                     | —                   | —                        | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                     | —                   | —                        | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                     | 6                   | 20                       | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                    | —                   | _                        | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                    | —                   | _                        | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                    | _                   | —                        | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                   | —                   | —                        | ns    |                             |  |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                    | _                   | 50                       | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                          | —                   | —                        | ns    | (Note 4)                    |  |

| SP60               | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge        | —                                                     | _                   | 50                       | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

1:128

70