Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

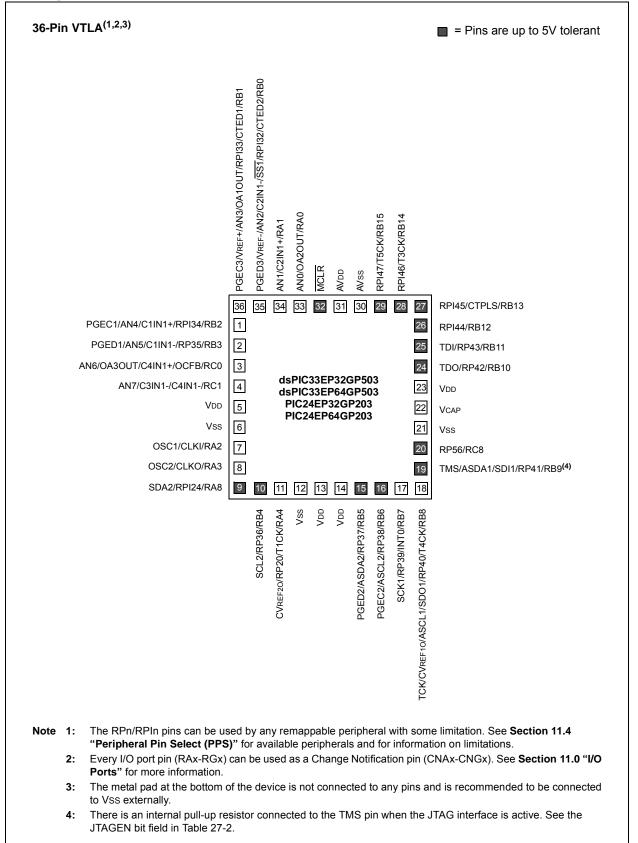

#### **Pin Diagrams (Continued)**

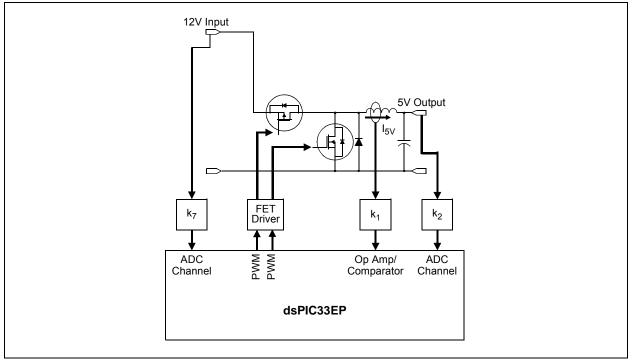

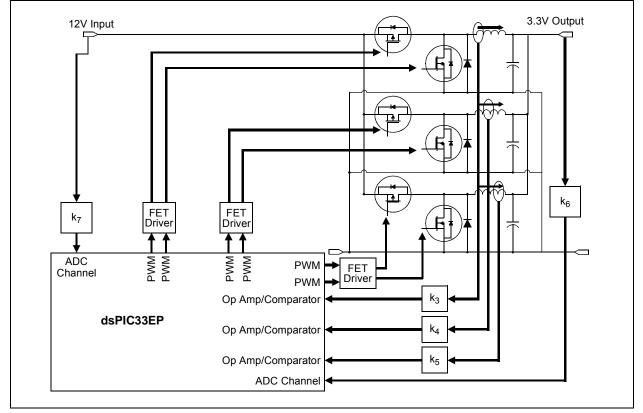

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

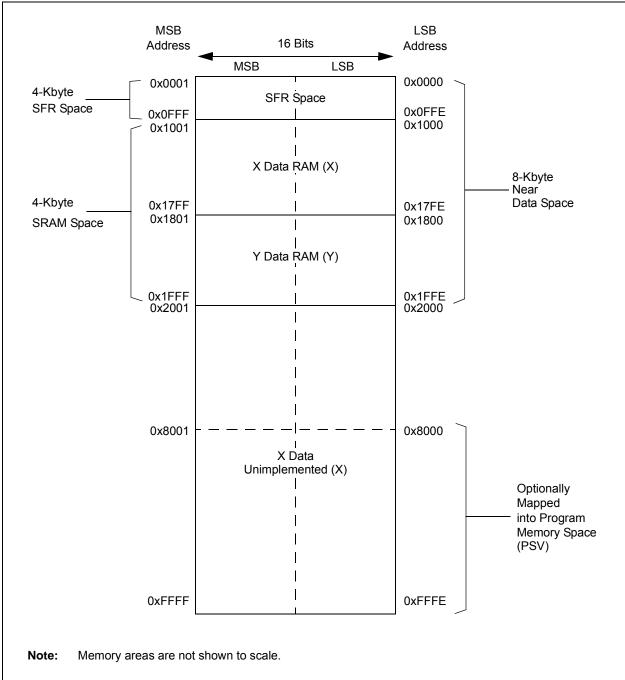

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

#### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                  | U-0        | U-0              | U-0 | U-0                                | U-0                     | U-0                     | U-0         |  |

|----------------------|------------|------------------|-----|------------------------------------|-------------------------|-------------------------|-------------|--|

| —                    | —          | —                | _   | —                                  | —                       | —                       | _           |  |

| bit 15               |            |                  |     |                                    |                         |                         | bit 8       |  |

|                      |            |                  |     |                                    |                         |                         |             |  |

| U-0                  | U-0        | U-0              | U-0 | U-0                                | R/W-0                   | R/W-0                   | R/W-0       |  |

| —                    | —          | —                | _   | —                                  | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |  |

| bit 7                |            |                  |     |                                    |                         |                         | bit 0       |  |

|                      |            |                  |     |                                    |                         |                         |             |  |

| Legend:              |            |                  |     |                                    |                         |                         |             |  |

| R = Readable         | bit        | W = Writable     | bit | U = Unimplemented bit, read as '0' |                         |                         |             |  |

| -n = Value at POR '1 |            | '1' = Bit is set |     | '0' = Bit is cleared               |                         | x = Bit is unknown      |             |  |

|                      |            |                  |     |                                    |                         |                         |             |  |

| bit 15-3             | Unimplemen | ted: Read as '   | י'  |                                    |                         |                         |             |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |              |                                         |                                    |       |        |       |

|------------------------------------|-------|--------------|-----------------------------------------|------------------------------------|-------|--------|-------|

|                                    | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |

|                                    | F7BF  | P<3:0>       |                                         |                                    | F6BF  | P<3:0> |       |

| bit 15                             |       |              |                                         |                                    |       |        | bit 8 |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |

|                                    | F5BF  | °<3:0>       |                                         |                                    | F4BF  | P<3:0> |       |

| bit 7                              |       |              |                                         |                                    |       |        | bit 0 |

| Legend:                            |       |              |                                         |                                    |       |        |       |

| R = Readable bi                    | t     | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |       |        |       |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown   |       |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|-----------------|----------|-------|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                | F10BP<3:0>                              |                 |          |       |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                 |          | bit 8 |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                |                                         | F8B             | P<3:0>   |       |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                 |          | bit 0 |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                 |          |       |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplen                            | nented bit, rea | d as '0' |       |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                 |          |       |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1   | 5:12>)   |       |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1  | 2>)      |       |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1  | 2>)      |       |  |

|               |                                                    |                                                                                               |                                                |                                         |                 |          |       |  |

© 2011-2013 Microchip Technology Inc.

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15MSK<1:0>                                    |                                                                                                                      | F14MSK<1:0>                                                                                                           |                                                                                                                                                      | F13MSK<1:0>                                                                                                               |                                                                         | F12MSK<1:0>                  |        |

| bit 15                                         |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

|                                                |                                                                                                                      | 54446                                                                                                                 | 5444                                                                                                                                                 |                                                                                                                           |                                                                         | 5444.0                       |        |

| R/W-0 R/W-0                                    |                                                                                                                      | R/W-0 R/W-0                                                                                                           |                                                                                                                                                      | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

| F11M                                           | ISK<1:0>                                                                                                             | F10MS                                                                                                                 | K<1:0>                                                                                                                                               | F9MS                                                                                                                      | K<1:0>                                                                  | F8MSI                        | <<1:0> |

| bit 7                                          |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                                |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                        |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readable                                   | e bit                                                                                                                | W = Writable                                                                                                          | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                  | POR                                                                                                                  | '1' = Bit is set                                                                                                      |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unkr              | nown   |

| bit 15 14                                      | ELEMOK A                                                                                                             | n. Maak Saura                                                                                                         | o for Filtor 15                                                                                                                                      | hita                                                                                                                      |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                 | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                              | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12                                      | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                           | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |

| bit 15-14<br>bit 13-12<br>bit 11-10<br>bit 9-8 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source                              | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12<br>bit 11-10                         | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0                | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source<br><b>0&gt;:</b> Mask Source | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0<br>F11MSK<1:0  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6   | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |

| R/W-x         | R/W-x                            | R/W-x                                        | R/W-x                                     | R/W-x            | R/W-x            | R/W-x              | R/W-x |  |  |  |  |  |

|---------------|----------------------------------|----------------------------------------------|-------------------------------------------|------------------|------------------|--------------------|-------|--|--|--|--|--|

| EID5          | EID4                             | EID3                                         | EID2                                      | EID1             | EID0             | RTR                | RB1   |  |  |  |  |  |

| bit 15        |                                  |                                              |                                           |                  |                  |                    | bit 8 |  |  |  |  |  |

|               |                                  |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

| U-x           | U-x                              | U-x                                          | R/W-x                                     | R/W-x            | R/W-x            | R/W-x              | R/W-x |  |  |  |  |  |

| —             | —                                | _                                            | RB0                                       | DLC3             | DLC2             | DLC1               | DLC0  |  |  |  |  |  |

| bit 7         |                                  |                                              |                                           |                  |                  |                    | bit 0 |  |  |  |  |  |

| Lonondi       |                                  |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

| Legend:       | l. h.:.                          |                                              | L.11                                      |                  |                  | -l (O)             |       |  |  |  |  |  |

| R = Readab    |                                  | W = Writable                                 |                                           | •                | mented bit, read |                    |       |  |  |  |  |  |

| -n = Value a  | t POR                            | '1' = Bit is set                             |                                           | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |  |  |

|               |                                  |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

| bit 15-10     | EID<5:0>: E                      | xtended Identifi                             | er bits                                   |                  |                  |                    |       |  |  |  |  |  |

| bit 9         | RTR: Remot                       | RTR: Remote Transmission Request bit         |                                           |                  |                  |                    |       |  |  |  |  |  |

|               | <u>When IDE = 1:</u>             |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

|               | •                                | 1 = Message will request remote transmission |                                           |                  |                  |                    |       |  |  |  |  |  |

|               | 0 = Normal n                     | 0                                            |                                           |                  |                  |                    |       |  |  |  |  |  |

|               | When IDE =<br>The RTR bit        |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

| <b>h</b> :+ 0 | RB1: Reserv                      |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

| bit 8         |                                  |                                              | Bit 1<br>his bit to '0' per CAN protocol. |                  |                  |                    |       |  |  |  |  |  |

|               |                                  |                                              | •                                         | 0001.            |                  |                    |       |  |  |  |  |  |

| bit 7-5       | •                                | nted: Read as '                              | 0                                         |                  |                  |                    |       |  |  |  |  |  |

| bit 4         | RB0: Reserv                      |                                              | <b></b>                                   |                  |                  |                    |       |  |  |  |  |  |

|               | User must se                     | et this bit to '0' p                         | per CAN proto                             | ocol.            |                  |                    |       |  |  |  |  |  |

| hit 2 0       | DIC -2:0 - Data Langth Cada hita |                                              |                                           |                  |                  |                    |       |  |  |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x                 | R/W-x | R/W-x |  |

|-------------------|-------|------------------|-------|------------------------------------|-----------------------|-------|-------|--|

|                   |       |                  | Ву    | /te 1                              |                       |       |       |  |

| bit 15            |       |                  |       |                                    |                       |       | bit 8 |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x                 | R/W-x | R/W-x |  |

|                   |       |                  | Ву    | rte 0                              |                       |       |       |  |

| bit 7             |       |                  |       |                                    |                       |       | bit 0 |  |

| Legend:           |       |                  |       |                                    |                       |       |       |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |                       |       |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle                   | eared x = Bit is unkn |       | nown  |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

| R/W-0      | U-0                                                                                         | U-0                                                                                            | R/W-0                        | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

|------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|

| CH0NB      | _                                                                                           | —                                                                                              | CH0SB4 <sup>(1)</sup>        | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |

| bit 15     | •                                                                                           |                                                                                                |                              | •                     |                          |                       | bit 8                 |  |  |  |

|            |                                                                                             |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

| R/W-0      | U-0                                                                                         | U-0                                                                                            | R/W-0                        | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

| CH0NA      |                                                                                             |                                                                                                | CH0SA4 <sup>(1)</sup>        | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |

| bit 7      |                                                                                             |                                                                                                |                              |                       |                          |                       | bit (                 |  |  |  |

|            |                                                                                             |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

| Legend:    |                                                                                             |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

| R = Read   |                                                                                             | W = Writable                                                                                   |                              | •                     | nented bit, read         |                       |                       |  |  |  |

| -n = Value | e at POR                                                                                    | '1' = Bit is set                                                                               |                              | '0' = Bit is cle      | ared                     | x = Bit is unkr       | lown                  |  |  |  |

| bit 15     |                                                                                             | nannel 0 Negative                                                                              | Input Soloot fo              | r Samala MUV          | 'D hit                   |                       |                       |  |  |  |

| DIL 15     |                                                                                             | el 0 negative input                                                                            |                              |                       |                          |                       |                       |  |  |  |

|            |                                                                                             | el 0 negative input                                                                            |                              |                       |                          |                       |                       |  |  |  |

| bit 14-13  | Unimplem                                                                                    | ented: Read as 'o                                                                              | )'                           |                       |                          |                       |                       |  |  |  |

| bit 12-8   | CH0SB<4:                                                                                    | 0>: Channel 0 Po                                                                               | sitive Input Sele            | ect for Sample        | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |

|            |                                                                                             | pen; use this sele                                                                             |                              |                       |                          | ement                 |                       |  |  |  |

|            | 11110 <b>= C</b>                                                                            | nannel 0 positive in                                                                           | put is connected             | to the CTMU te        | emperature mea           | surement diode        | (CTMU TEMF            |  |  |  |

|            |                                                                                             | 11101 = Reserved                                                                               |                              |                       |                          |                       |                       |  |  |  |

|            |                                                                                             | 11100 = Reserved<br>11011 = Reserved                                                           |                              |                       |                          |                       |                       |  |  |  |

|            |                                                                                             | 11011 – Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup> |                              |                       |                          |                       |                       |  |  |  |

|            |                                                                                             | hannel 0 positive                                                                              |                              |                       |                          |                       |                       |  |  |  |

|            | 11000 <b>= C</b>                                                                            | hannel 0 positive                                                                              | input is the outp            | out of OA1/AN3        | <sub>3</sub> (2)         |                       |                       |  |  |  |

|            | 10111 <b>= R</b>                                                                            | eserved                                                                                        |                              |                       |                          |                       |                       |  |  |  |

|            | •                                                                                           |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

|            | •                                                                                           |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

|            | 10000 <b>= R</b>                                                                            | eserved                                                                                        |                              |                       |                          |                       |                       |  |  |  |

|            | 01111 <b>= C</b>                                                                            | hannel 0 positive                                                                              | input is AN15 <sup>(3)</sup> |                       |                          |                       |                       |  |  |  |

|            | 01110 = C                                                                                   | hannel 0 positive                                                                              | input is AN14 <sup>(3)</sup> |                       |                          |                       |                       |  |  |  |

|            | 01101 = C                                                                                   | hannel 0 positive                                                                              | Input is AN130               |                       |                          |                       |                       |  |  |  |

|            | •                                                                                           |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

|            | •                                                                                           | •                                                                                              |                              |                       |                          |                       |                       |  |  |  |

|            | 00010 <b>= C</b>                                                                            | hannel 0 positive                                                                              | input is AN2 <sup>(3)</sup>  |                       |                          |                       |                       |  |  |  |

|            |                                                                                             | hannel 0 positive<br>hannel 0 positive                                                         |                              |                       |                          |                       |                       |  |  |  |

| L:1 7      |                                                                                             | •                                                                                              | •                            |                       | A 64                     |                       |                       |  |  |  |

| bit 7      | CH0NA: Channel 0 Negative Input Select for Sample MUXA bit                                  |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

|            | 1 = Channel 0 negative input is AN1 <sup>(1)</sup><br>0 = Channel 0 negative input is VREFL |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

| bit 6-5    |                                                                                             | ented: Read as '                                                                               |                              |                       |                          |                       |                       |  |  |  |

| Note 1:    | to determine I                                                                              | AN7 are repurpos<br>now enabling a pa                                                          |                              |                       |                          |                       |                       |  |  |  |

| -          | and 3.                                                                                      |                                                                                                |                              |                       |                          |                       | - >                   |  |  |  |

| 2:         | The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1);    |                                                                                                |                              |                       |                          |                       |                       |  |  |  |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

#### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | R = Read-Only bit |   |         | U = Unimplem          |   |   |        |

|--------|-------------------|---|---------|-----------------------|---|---|--------|

|        |                   |   |         |                       |   |   |        |

| bit 7  |                   |   |         |                       |   |   | bit 0  |

|        |                   |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 15 |                   |   |         |                       |   |   | bit 8  |

|        |                   |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 23 |                   |   |         |                       |   |   | bit 16 |

|        |                   |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

#### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0> <sup>(1)</sup>  |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

#### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|--------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53                 | NEG                  | NEG    | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG    | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP    | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR   |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP    | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP    | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D  | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S  |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH   | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH   | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL  | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL  | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET  |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW  | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC    | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC   | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC    | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC    | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |

| 07                 |                      | RRC    | Ws,Wd                                                          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                           |

| 67                 | RRNC                 | RRNC   | f                                                              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                             |

|                    |                      | RRNC   | f,WREG                                                         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                             |

| <u></u>            | ~~~~                 | RRNC   | Ws,Wd                                                          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                             |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo <sup>(1)</sup><br>Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                 | 1             | 1                             | None                            |

| 60                 | CE                   | SAC.R  |                                                                | Store Rounded Accumulator                         | 1             | 1                             | None                            |

| 69<br>70           | SE                   | SE     | Ws,Wnd                                                         | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1                             | C,N,Z<br>None                   |

| 10                 | SETM                 | SETM   | f                                                              |                                                   | -             | 1                             |                                 |

|                    |                      | SETM   | WREG                                                           | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1                             | None                            |

| 71                 | SFTAC                | SETM   | Ws<br>Acc, Wn <sup>(1)</sup>                                   | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | None<br>OA,OB,OAB,<br>SA,SB,SAB |

|                    |                      | SFTAC  | Acc,#Slit6 <sup>(1)</sup>                                      | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| DC CHARACTERISTICS |        |                                                             |                    | s otherv | rating Co<br>vise stat<br>perature | <b>ed)</b><br>-40°C | s: 3.0V to 3.6V<br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended                                                                                           |

|--------------------|--------|-------------------------------------------------------------|--------------------|----------|------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                              | Min.               | Тур.     | Max.                               | Units               | Conditions                                                                                                                                                                                 |

| DO10               | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                    |          | 0.4                                | V                   | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}$ , $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}$ , $+85^{\circ}\text{C} < \text{TA} \le +125^{\circ}\text{C}$ |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                  |          | 0.4                                | V                   |                                                                                                                                                                                            |