Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/S-0                | U-0                                                                           | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |

|----------------------|-------------------------------------------------------------------------------|------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|

| FORCE <sup>(1)</sup> |                                                                               | _                | _                     | —                |                  | _               |         |  |  |  |

| bit 15               |                                                                               |                  |                       |                  |                  |                 | bit 8   |  |  |  |

|                      |                                                                               |                  |                       |                  |                  |                 |         |  |  |  |

| R/W-0                | R/W-0                                                                         | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| IRQSEL7              | IRQSEL6                                                                       | IRQSEL5          | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |

| bit 7                |                                                                               |                  |                       |                  |                  |                 | bit     |  |  |  |

| Legend:              |                                                                               | S = Settable b   | oit                   |                  |                  |                 |         |  |  |  |

| R = Readable         | bit                                                                           | W = Writable     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |

| -n = Value at F      | POR                                                                           | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |

|                      |                                                                               |                  |                       |                  |                  |                 |         |  |  |  |

| bit 15               | FORCE: Force                                                                  | e DMA Transfe    | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |

|                      | 1 = Forces a                                                                  | single DMA tra   | insfer (Manua         | l mode)          |                  |                 |         |  |  |  |

|                      | 0 = Automati                                                                  | c DMA transfer   | initiation by D       | DMA request      |                  |                 |         |  |  |  |

| bit 14-8             | Unimplemen                                                                    | ted: Read as 'd  | )'                    |                  |                  |                 |         |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                            |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                             |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                                              |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00100101 = IC3 - Input Capture 3                                              |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00100010 = ECAN1 - RX Data Ready(2)                                           |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00100001 = SPI2 Transfer Done<br>00011111 = UART2TX – UART2 Transmitter       |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00011111 = UART2TX - UART2 Transmitter $00011110 = UART2RX - UART2 Receiver$  |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00011100 = TMR5 - Timer5                                                      |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00011011 = TMR4 - Timer4                                                      |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                             |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                             |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done<br>00001100 = UART1TX – UART1 Transmitter |                  |                       |                  |                  |                 |         |  |  |  |

|                      |                                                                               |                  |                       |                  |                  |                 |         |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver<br>00001010 = SPI1 – Transfer Done        |                  |                       |                  |                  |                 |         |  |  |  |

|                      |                                                                               | TMR3 – Timer3    |                       |                  |                  |                 |         |  |  |  |

|                      |                                                                               | TMR2 – Timer2    |                       |                  |                  |                 |         |  |  |  |

|                      |                                                                               | OC2 – Output (   |                       |                  |                  |                 |         |  |  |  |

|                      |                                                                               | IC2 – Input Ca   |                       |                  |                  |                 |         |  |  |  |

|                      | 00000010 =                                                                    | OC1 – Output (   | Compare 1             |                  |                  |                 |         |  |  |  |

|                      |                                                                               | IC1 – Input Ca   |                       |                  |                  |                 |         |  |  |  |

|                      | 00000000 =                                                                    | INT0 – Externa   | I Interrupt 0         |                  |                  |                 |         |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

NOTES:

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                    |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is cleared               |               | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b     | its   |  |

## 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| Legend:C = Writable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |             |       |      |        |        |       |       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|------|--------|--------|-------|-------|--|--|

| bit 7                                                                                                                                   | bit 7 bit 0 |       |      |        |        |       |       |  |  |

| IVRIF                                                                                                                                   | WAKIF       | ERRIF | _    | FIFOIF | RBOVIF | RBIF  | TBIF  |  |  |

| R/C-0                                                                                                                                   | R/C-0       | R/C-0 | U-0  | R/C-0  | R/C-0  | R/C-0 | R/C-0 |  |  |

|                                                                                                                                         |             |       |      |        |        |       | 2 0   |  |  |

| bit 15                                                                                                                                  |             |       |      |        |        |       | bit 8 |  |  |

| _                                                                                                                                       | —           | ТХВО  | TXBP | RXBP   | TXWAR  | RXWAR | EWARN |  |  |

| U-0                                                                                                                                     | U-0         | R-0   | R-0  | R-0    | R-0    | R-0   | R-0   |  |  |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                                                          |

|           | 1 = Transmitter is in Bus Off state                                                                                                          |

|           | 0 = Transmitter is not in Bus Off state                                                                                                      |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                                                      |

|           | <ul><li>1 = Transmitter is in Bus Passive state</li><li>0 = Transmitter is not in Bus Passive state</li></ul>                                |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                                                         |

|           | 1 = Receiver is in Bus Passive state<br>0 = Receiver is not in Bus Passive state                                                             |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                                                                |

|           | 1 = Transmitter is in Error Warning state<br>0 = Transmitter is not in Error Warning state                                                   |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                                                                   |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                                                         |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                                                                    |

|           | <ul> <li>1 = Transmitter or receiver is in Error Warning state</li> <li>0 = Transmitter or receiver is not in Error Warning state</li> </ul> |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                                                                    |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                                                               |

|           | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                                                           |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 4     | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                                                                  |

|           | 1 = Interrupt request has occurred                                                                                                           |

|           | 0 = Interrupt request has not occurred                                                                                                       |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                                                                |

|           | 1 = Interrupt request has occurred                                                                                                           |

-n = Value at POR

# REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |              |       |                                         |           |        |       |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-----------|--------|-------|--|--|

|                                    | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0     | R/W-0  | R/W-0 |  |  |

|                                    | F7BF  | P<3:0>       |       |                                         | F6BF      | P<3:0> |       |  |  |

| bit 15                             |       |              |       |                                         |           |        | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0     | R/W-0  | R/W-0 |  |  |

|                                    | F5BF  | °<3:0>       |       |                                         | F4BP<3:0> |        |       |  |  |

| bit 7                              |       |              |       |                                         |           |        | bit 0 |  |  |

| Legend:                            |       |              |       |                                         |           |        |       |  |  |

| R = Readable bi                    | t     | W = Writable | bit   | U = Unimplemented bit, read as '0'      |           |        |       |  |  |

| -n = Value at POR (1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |           |        | nown  |  |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|--|

|               | F11BP<3:0>                                         |                                                                                               |                                                |                                         | F10BP<3:0>     |        |       |  |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                |        | bit 8 |  |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                |                                         | F8B            | P<3:0> |       |  |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                |        | bit 0 |  |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                |        |       |  |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplemented bit, read as '0'      |                |        |       |  |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                |        |       |  |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1  | 5:12>) |       |  |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |  |

|               |                                                    |                                                                                               |                                                |                                         |                |        |       |  |  |

© 2011-2013 Microchip Technology Inc.

| R/W-0         | R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0           | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |  |  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------|----------------|--------------------|--------|--|--|--|

|               | F15B                         | P<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | F14BP<3:0>                         |                |                    |        |  |  |  |

| bit 15        | bit 15                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                    |                |                    | bit 8  |  |  |  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0           | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |  |  |

| 1011 0        |                              | P<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10110           |                                    |                | P<3:0>             | 1010 0 |  |  |  |

| bit 7         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                    |                |                    | bit 0  |  |  |  |

| Legend:       |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                                    |                |                    |        |  |  |  |

| R = Readabl   | e bit                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit             | U = Unimplemented bit, read as '0' |                |                    |        |  |  |  |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | '0' = Bit is cleared               |                | x = Bit is unknown |        |  |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         F15BP<3:0>: RX Buffer Mask for Filter 15 bits         1111 = Filter hits received in RX FIFO buffer         1110 = Filter hits received in RX Buffer 14         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         •         • |                 |                                    |                |                    |        |  |  |  |

| bit 11-8      | F14BP<3:0;                   | RX Buffer Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sk for Filter 1 | 4 bits (same val                   | ues as bits<15 | :12>)              |        |  |  |  |

| bit 7-4       | F13BP<3:0;                   | RX Buffer Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sk for Filter 1 | 3 bits (same val                   | ues as bits<15 | :12>)              |        |  |  |  |

| bit 3-0       | F12BP<3:0:                   | RX Buffer Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ues as bits<15  | :12>)                              |                |                    |        |  |  |  |

## REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

NOTES:

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|

|                                    |       |                | PTGSD | LIM<15:8>                               |       |       |       |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |

|                                    |       |                |       |                                         |       |       |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                | PTGSE | )LIM<7:0>                               |       |       |       |

| bit 7                              |       |                |       |                                         |       |       | bit 0 |

|                                    |       |                |       |                                         |       |       |       |

| Legend:                            |       |                |       |                                         |       |       |       |

| R = Readable                       | bit   | W = Writable b | it    | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                         | R/W-0 | R/W-0            | R/W-0 | R/W-0                               | R/W-0           | R/W-0     | R/W-0 |

|-------------------------------|-------|------------------|-------|-------------------------------------|-----------------|-----------|-------|

|                               |       |                  | PTGC0 | LIM<15:8>                           |                 |           |       |

| bit 15                        |       |                  |       |                                     |                 |           | bit 8 |

|                               |       |                  |       |                                     |                 |           |       |

| R/W-0                         | R/W-0 | R/W-0            | R/W-0 | R/W-0                               | R/W-0           | R/W-0     | R/W-0 |

|                               |       |                  | PTGC  | )LIM<7:0>                           |                 |           |       |

| bit 7                         |       |                  |       |                                     |                 |           | bit 0 |

|                               |       |                  |       |                                     |                 |           |       |

| Legend:                       |       |                  |       |                                     |                 |           |       |

| R = Readable bit W = Writable |       | W = Writable bi  | it    | U = Unimplem                        | nented bit, rea | ad as '0' |       |

| -n = Value at POR             |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unk |                 |           | nown  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### 25.1.2 OP AMP CONFIGURATION B

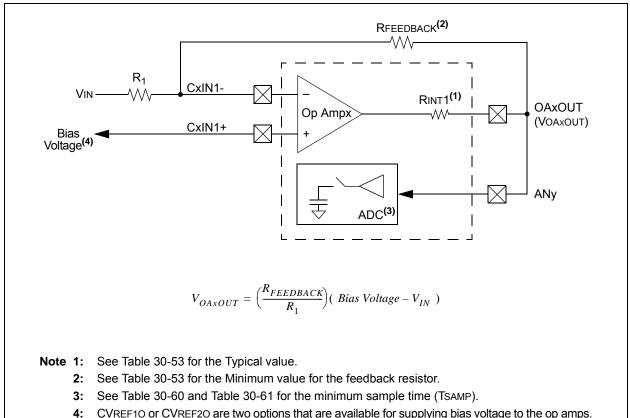

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

# 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | product page using the link above, enter    |  |  |  |  |  |

|       | this URL in your browser:                   |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/       |  |  |  |  |  |

|       | Devices.aspx?dDocName=en555464              |  |  |  |  |  |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

| DC CHARACTERISTICS |        |                                                     | (unless             |      | ise state | <b>d)</b><br>-40°C :                     | s: 3.0V to 3.6V<br>≤ TA ≤ +85°C for Industrial                 |  |  |  |

|--------------------|--------|-----------------------------------------------------|---------------------|------|-----------|------------------------------------------|----------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Min.                                                | Тур. <sup>(1)</sup> | Max. | Units     | ≤ TA ≤ +125°C for Extended<br>Conditions |                                                                |  |  |  |

|                    |        | Program Flash Memory                                |                     |      |           |                                          |                                                                |  |  |  |

| D130               | Eр     | Cell Endurance                                      | 10,000              | —    | _         | E/W                                      | -40°C to +125°C                                                |  |  |  |

| D131               | Vpr    | VDD for Read                                        | 3.0                 | —    | 3.6       | V                                        |                                                                |  |  |  |

| D132b              | VPEW   | VDD for Self-Timed Write                            | 3.0                 | —    | 3.6       | V                                        |                                                                |  |  |  |

| D134               | TRETD  | Characteristic Retention                            | 20                  | _    |           | Year                                     | Provided no other specifications are violated, -40°C to +125°C |  |  |  |

| D135               | IDDP   | Supply Current during<br>Programming <sup>(2)</sup> | —                   | 10   |           | mA                                       |                                                                |  |  |  |

| D136               | IPEAK  | Instantaneous Peak Current<br>During Start-up       | —                   | —    | 150       | mA                                       |                                                                |  |  |  |

| D137a              | Тре    | Page Erase Time                                     | 17.7                | —    | 22.9      | ms                                       | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |  |  |

| D137b              | Тре    | Page Erase Time                                     | 17.5                | —    | 23.1      | ms                                       | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |  |  |

| D138a              | Tww    | Word Write Cycle Time                               | 41.7                | —    | 53.8      | μs                                       | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |  |  |

| D138b              | Tww    | Word Write Cycle Time                               | 41.2                | —    | 54.4      | μs                                       | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |  |  |

#### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

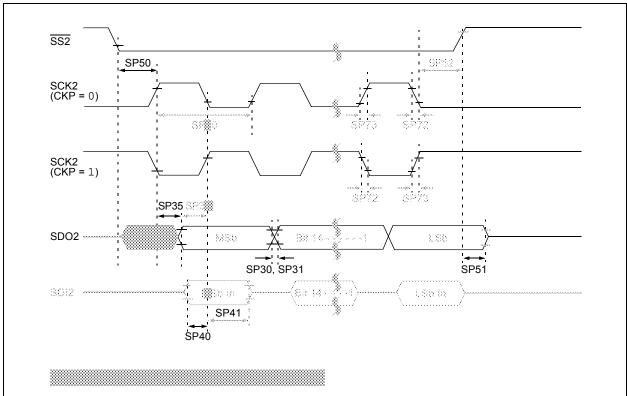

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

#### TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS                                                                                                  |      |               | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 2): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |            |    |          |

|---------------------------------------------------------------------------------------------------------------------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|----|----------|

| Param.         Symbol         Characteristic         Min.         Typ.         Max.         Units         Condition |      |               |                                                                                                                                                                                                                                                                                                      |   | Conditions |    |          |

| VR310                                                                                                               | TSET | Settling Time | —                                                                                                                                                                                                                                                                                                    | 1 | 10         | μS | (Note 1) |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | Standard O<br>(unless oth<br>Operating te | erwise st | 1          |     |               |  |  |

|--------------------|--------|--------------------------------------------|-------------------------------------------|-----------|------------|-----|---------------|--|--|

| Param<br>No.       | Symbol | I Characteristics Min. Typ. Max. Units     |                                           |           |            |     | Conditions    |  |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                 | _         | CVRSRC/32  | LSb |               |  |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | —                                         | ±25       | _          | mV  | CVRSRC = 3.3V |  |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                         | _         | AVDD + 0.3 | V   |               |  |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                         | 1.5k      | _          | Ω   |               |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        |                                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |   |       |            |                                                                    |  |

|--------------------|--------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------|--------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic Min.                                         | Min. Typ. Max.                                                                                                                         |   | Units | Conditions |                                                                    |  |

| HDO10              | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                        | — | 0.4   | V          | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)                                 |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | —                                                                                                                                      | — | 0.4   | V          | IOL ≤ 8 mA, VDD = 3.3V<br>(Note 1)                                 |  |

| HDO20 V            | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                    | — | —     | V          | IOH ≥ -10 mA, VDD = 3.3V<br>(Note 1)                               |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                    | — | —     | V          | ІОн ≥ 15 mA, VDD = 3.3V<br>(Note 1)                                |  |

| HDO20A             | Vон1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5                                                                                                                                    | — | —     | V          | IOH ≥ -3.9 mA, VDD = 3.3V<br>(Note 1)                              |  |

|                    |        |                                                             | 2.0                                                                                                                                    | — | —     |            | $IOH \ge -3.7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>(Note 1)  |  |

|                    |        |                                                             | 3.0                                                                                                                                    | — | —     |            | IOH ≥ -2 mA, VDD = 3.3V<br>(Note 1)                                |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5                                                                                                                                    | _ | _     | V          | IOH ≥ -7.5 mA, VDD = 3.3V<br>(Note 1)                              |  |

|                    |        |                                                             | 2.0                                                                                                                                    | — | —     |            | $IOH \ge -6.8 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$<br>(Note 1) |  |

|                    |        |                                                             | 3.0                                                                                                                                    | — | —     |            | IOH ≥ -3 mA, VDD = 3.3V<br>(Note 1)                                |  |

# TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

## 33.1 Package Marking Information (Continued)

48-Lead UQFN (6x6x0.5 mm)

Example 33EP64GP 504-I/MV (3) 1310017

64-Lead QFN (9x9x0.9 mm)

Example dsPIC33EP 64GP506 -I/MR® 1310017

64-Lead TQFP (10x10x1 mm)

Example

© 2011-2013 Microchip Technology Inc.

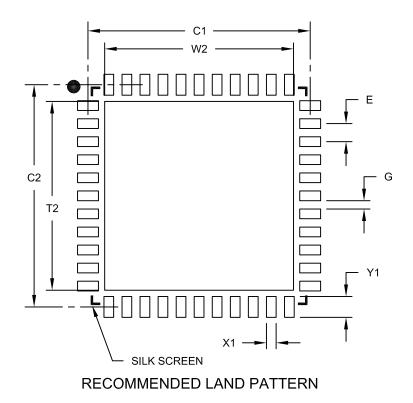

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Ν               | <b>ILLIMETER</b> | S    |          |  |  |  |

|----------------------------|-----------------|------------------|------|----------|--|--|--|

| Dimension                  | MIN             | NOM              | MAX  |          |  |  |  |

| Contact Pitch              | Contact Pitch E |                  |      | 0.65 BSC |  |  |  |

| Optional Center Pad Width  | W2              | 6.6              |      |          |  |  |  |

| Optional Center Pad Length | T2              |                  |      | 6.60     |  |  |  |

| Contact Pad Spacing        | C1              |                  | 8.00 |          |  |  |  |

| Contact Pad Spacing        | C2              |                  | 8.00 |          |  |  |  |

| Contact Pad Width (X44)    | X1              |                  |      | 0.35     |  |  |  |

| Contact Pad Length (X44)   | Y1              |                  |      | 0.85     |  |  |  |

| Distance Between Pads      | G               | 0.25             |      |          |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

NOTES: