#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

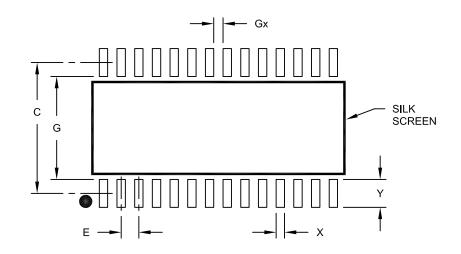

| Mounting Type              | Surface Mount                                                                    |

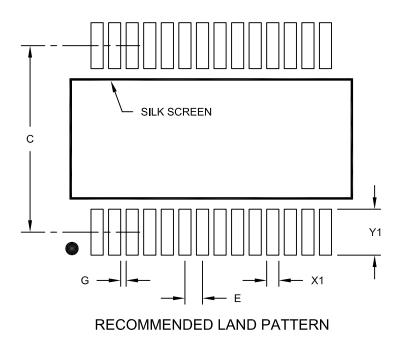

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | <i>•</i>                       | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

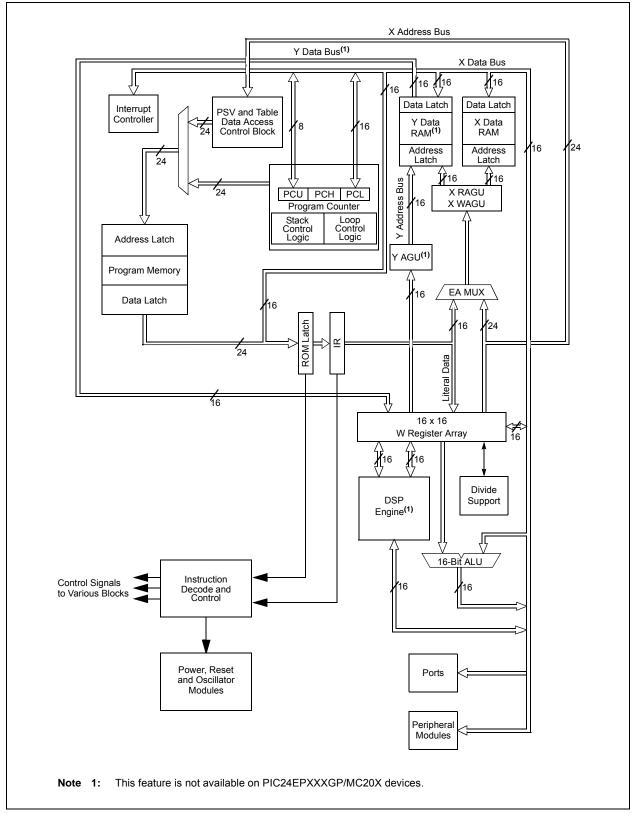

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                     | SV SI ACE BOON |              |                        |                |              |                        |  |  |

|-------------|-----------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|

| 0/11        |                       |                | Before       |                        | After          |              |                        |  |  |

| O/U,<br>R/W | Operation             | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |

| O,<br>Read  |                       | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |

| O,<br>Read  | [++Wn]                | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++]   | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |

| O,<br>Write |                       | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |

| U,<br>Read  |                       | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |

| U,<br>Read  | [Wn ]<br>Or<br>[ Wn ] | or page        |              | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |

| U,<br>Read  | [ //11 - ]            | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |  |  |  |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |  |  |  |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |  |

| bit 13        | Unimplemented: Read as '0'<br>ROSSLP: Reference Oscillator Run in Sleep bit                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |  |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |  |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |  |  |  |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |  |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |  |  |  |

## REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

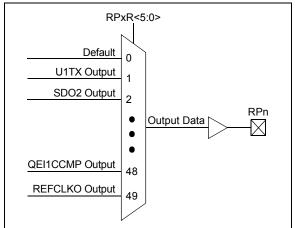

#### 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0          | R/W-x          | U-0                           | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x   |

|--------------|----------------|-------------------------------|------------------|------------------|------------------|-----------------|---------|

| —            | WAKFIL         |                               | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |

| bit 15       |                |                               |                  |                  |                  |                 | bit     |

|              |                |                               |                  |                  |                  |                 |         |

| R/W-x        | R/W-x          | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x   |

| SEG2PHTS     | S SAM          | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |

| bit 7        |                |                               |                  |                  |                  |                 | bit     |

| Legend:      |                |                               |                  |                  |                  |                 |         |

| R = Readab   | le bit         | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'        |         |

| -n = Value a |                | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |

|              |                |                               |                  |                  |                  |                 |         |

| bit 15       | Unimplemen     | nted: Read as '               | 0'               |                  |                  |                 |         |

| bit 14       | WAKFIL: Sel    | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                 |         |

|              |                | N bus line filter             |                  |                  |                  |                 |         |

|              |                | line filter is not            |                  | e-up             |                  |                 |         |

| bit 13-11    | -              | nted: Read as '               |                  |                  |                  |                 |         |

| bit 10-8     |                | 0>: Phase Segr                | nent 2 bits      |                  |                  |                 |         |

|              | 111 = Length   | IIS 8 X IQ                    |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | 000 = Length   | n is 1 x To                   |                  |                  |                  |                 |         |

| bit 7        | -              | Phase Segmer                  | nt 2 Time Sele   | ct bit           |                  |                 |         |

|              | 1 = Freely pro | -                             |                  |                  |                  |                 |         |

|              |                | n of SEG1PHx I                | bits or Informa  | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |

| bit 6        | SAM: Sample    | e of the CAN B                | us Line bit      |                  |                  |                 |         |

|              |                | s sampled threes sampled once |                  |                  |                  |                 |         |

| bit 5-3      | SEG1PH<2:0     | <b>0&gt;:</b> Phase Segr      | nent 1 bits      |                  |                  |                 |         |

|              | 111 = Length   | n is 8 x Tq                   |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | 000 = Length   |                               |                  |                  |                  |                 |         |

| bit 2-0      |                | >: Propagation                | Time Segmen      | t bits           |                  |                 |         |

|              | 111 = Length   | IIS8XIQ                       |                  |                  |                  |                 |         |

|              |                |                               |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

|              | •              |                               |                  |                  |                  |                 |         |

## REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

## 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

## 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

## 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

| _                    |                              |                                 |                         |                        |                      |                      |                      |

|----------------------|------------------------------|---------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|

| R/W-0                | U-0                          | U-0                             | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADRC                 | —                            | —                               | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15               |                              |                                 |                         |                        |                      |                      | bit 8                |

|                      |                              |                                 |                         |                        |                      |                      |                      |

| R/W-0                | R/W-0                        | R/W-0                           | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>         | ADCS5 <sup>(2)</sup>            | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                |                              |                                 |                         |                        |                      |                      | bit 0                |

| r                    |                              |                                 |                         |                        |                      |                      |                      |

| Legend:              |                              |                                 |                         |                        |                      |                      |                      |

| R = Readable b       |                              | W = Writable k                  | bit                     | •                      | nented bit, read     | l as '0'             |                      |

| -n = Value at P      | OR                           | '1' = Bit is set                |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |

| bit 15               | 1 = ADC inter                |                                 |                         |                        |                      |                      |                      |

|                      |                              | ved from syste                  |                         |                        |                      |                      |                      |

| bit 14-13            | •                            | ted: Read as '0                 |                         |                        |                      |                      |                      |

| bit 12-8             |                              | Auto-Sample T                   | ime bits <sup>(1)</sup> |                        |                      |                      |                      |

|                      | 11111 = <b>31</b> T          | AD                              |                         |                        |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | 00001 = 1 TA<br>00000 = 0 TA |                                 |                         |                        |                      |                      |                      |

| bit 7-0              | ADCS<7:0>:                   | ADC1 Convers                    | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |

|                      | 11111111 = <sup>-</sup><br>• | TP • (ADCS<7:                   | 0> + 1) = TP •          | 256 = Tad              |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | 00000010 = -                 | TP • (ADCS<7:                   | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |

|                      | 0000001 =                    | TP • (ADCS<7:<br>TP • (ADCS<7:  | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |

|                      | •                            | d if SSRC<2:0><br>if ADRC (AD10 | •                       | ,                      | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |

## REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

|------------|---------------------------------------|------------------------------------|----------------|------------------|------------------------------|-----------------|--------|

| ADCTS4     | ADCTS3                                | ADCTS2                             | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |

| bit 15     |                                       |                                    |                |                  |                              |                 | bit 8  |

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

| OC4CS      |                                       | OC2CS                              | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |

| bit 7      |                                       | 00100                              |                |                  |                              |                 | bit (  |

| Legend:    |                                       |                                    |                |                  |                              |                 |        |

| R = Reada  | ble bit                               | W = Writable                       | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |

| -n = Value | at POR                                | '1' = Bit is set                   |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |

|            |                                       |                                    |                |                  |                              |                 |        |

| bit 15     | ADCTS4: Sa                            | mple Trigger P                     | TGO15 for AE   | OC bit           |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            | 0 = Does not                          | generate Trigg                     | er when the b  | roadcast com     | mand is execute              | ed              |        |

| bit 14     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            |                                       | es Trigger wher                    |                |                  |                              | al              |        |

| bit 13     |                                       |                                    |                |                  | mand is execute              | a               |        |

| DIE 13     |                                       | mple Trigger P<br>es Trigger wher  |                |                  | evecuted                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 12     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 11     | -                                     | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 10     | IC3TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC3 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 9      | IC2TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC2 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 8      |                                       | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 7      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>generate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 6      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>aenerate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 5      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            | 1 = Generate                          | es clock pulse v                   | when the broad |                  | d is executed command is exe | cuted           |        |

|            | This register is rea<br>PTGSTRT = 1). | -                                  |                |                  |                              |                 | and    |

|            | This register is on                   | lv used with the                   | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |

|            |                                       | .,                                 |                |                  | c.op commune                 | •               |        |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|--------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53 NEG             |                      | NEG    | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG    | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP    | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR   |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP    | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP    | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D  | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S  |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH   | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH   | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL  | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL  | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET  |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW  | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC    | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC   | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC    | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC    | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |

| 07                 |                      | RRC    | Ws,Wd                                                          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                           |

| 67                 | RRNC                 | RRNC   | f                                                              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                             |

|                    |                      | RRNC   | f,WREG                                                         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                             |

| <u></u>            | ~~~                  | RRNC   | Ws,Wd                                                          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                             |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo <sup>(1)</sup><br>Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                 | 1             | 1                             | None                            |

| 60                 | CE                   | SAC.R  |                                                                | Store Rounded Accumulator                         | 1             | 1                             | None                            |

| 69<br>70           | SE                   | SE     | Ws,Wnd                                                         | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1                             | C,N,Z<br>None                   |

| 10                 | SETM                 | SETM   | f                                                              |                                                   | -             | 1                             |                                 |

|                    |                      | SETM   | WREG                                                           | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1                             | None                            |

| 71                 | SFTAC                | SETM   | Ws<br>Acc, Wn <sup>(1)</sup>                                   | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | None<br>OA,OB,OAB,<br>SA,SB,SAB |

|                    |                      | SFTAC  | Acc,#Slit6 <sup>(1)</sup>                                      | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| АС СН        | ARACTERIS | TICS                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                             |  |  |  |  |

|--------------|-----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |  |  |  |

| SY00         | Τρυ       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                       | 400                 | 600  | μS    |                                                                                                             |  |  |  |  |

| SY10         | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                                                         | 1024 Tosc           |      |       | Tosc = OSC1 period                                                                                          |  |  |  |  |

| SY12         | Twdt      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                    | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |  |  |

|              |           |                                                                | 3.26                                                                                                                                                                                                                                                                                    | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |  |  |

| SY13         | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                                                                                                             |  |  |  |  |

| SY20         | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |  |  |  |  |

| SY30         | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |  |  |  |  |

| SY35         | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _                                                                                                                                                                                                                                                                                       | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |  |  |  |  |

| SY36         | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time | _                                                                                                                                                                                                                                                                                       | —                   | 30   | μS    |                                                                                                             |  |  |  |  |

| SY37         | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | 46                                                                                                                                                                                                                                                                                      | 48                  | 54   | μS    |                                                                                                             |  |  |  |  |