Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

# TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

# 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                      | 2: PERIPHER                                                                                  | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |

|--------------|-------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| U-0          | U-0                                       | U-0                                                                                          | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                           | _                                                                                            |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |

| bit 15       |                                           |                                                                                              |                 |                   |                 |                 | bit   |  |  |  |  |

| U-0          | U-0                                       | U-0                                                                                          | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                           |                                                                                              |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |

| bit 7        |                                           |                                                                                              |                 |                   |                 |                 | bit   |  |  |  |  |

|              |                                           |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

| Legend:      | 1.1.1                                     |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

| R = Readab   |                                           | W = Writable b                                                                               | Dit             | •                 | nented bit, rea |                 |       |  |  |  |  |

| -n = Value a | at POR                                    | '1' = Bit is set                                                                             |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |

| bit 15-12    | Unimplemen                                | ted: Read as '0                                                                              | ,               |                   |                 |                 |       |  |  |  |  |

| bit 11       | -                                         |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

|              | •                                         | IC4MD: Input Capture 4 Module Disable bit<br>1 = Input Capture 4 module is disabled          |                 |                   |                 |                 |       |  |  |  |  |

|              | 0 = Input Cap                             | 0 = Input Capture 4 module is enabled                                                        |                 |                   |                 |                 |       |  |  |  |  |

| bit 10       | IC3MD: Input Capture 3 Module Disable bit |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

|              | 1 = Input Capture 3 module is disabled    |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

|              |                                           | oture 3 module is                                                                            |                 |                   |                 |                 |       |  |  |  |  |

| bit 9        |                                           | IC2MD: Input Capture 2 Module Disable bit                                                    |                 |                   |                 |                 |       |  |  |  |  |

|              |                                           | oture 2 module is<br>oture 2 module is                                                       |                 |                   |                 |                 |       |  |  |  |  |

| bit 8        | IC1MD: Input                              | t Capture 1 Mod                                                                              | ule Disable bit |                   |                 |                 |       |  |  |  |  |

|              | 1 = Input Cap                             | oture 1 module is<br>oture 1 module is                                                       | s disabled      |                   |                 |                 |       |  |  |  |  |

| bit 7-4      |                                           | ted: Read as '0                                                                              |                 |                   |                 |                 |       |  |  |  |  |

| bit 3        | OC4MD: Out                                | put Compare 4                                                                                | Module Disable  | e bit             |                 |                 |       |  |  |  |  |

|              |                                           | ompare 4 modul                                                                               |                 |                   |                 |                 |       |  |  |  |  |

|              | 0 = Output Compare 4 module is enabled    |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

| bit 2        |                                           | OC3MD: Output Compare 3 Module Disable bit                                                   |                 |                   |                 |                 |       |  |  |  |  |

|              | 1 = Output Compare 3 module is disabled   |                                                                                              |                 |                   |                 |                 |       |  |  |  |  |

| L:1 4        | -                                         | 0 = Output Compare 3 module is enabled                                                       |                 |                   |                 |                 |       |  |  |  |  |

| bit 1        |                                           | <b>OC2MD:</b> Output Compare 2 Module Disable bit<br>1 = Output Compare 2 module is disabled |                 |                   |                 |                 |       |  |  |  |  |

|              | $\perp$ – Output Co                       | ompare z mouu                                                                                |                 |                   |                 |                 |       |  |  |  |  |

|              | 0 = Output Co                             | ompare 2 modul                                                                               | le is enabled   |                   |                 |                 |       |  |  |  |  |

| bit 0        |                                           | ompare 2 modul<br>put Compare 1                                                              |                 | e bit             |                 |                 |       |  |  |  |  |

| bit 0        | OC1MD: Out                                | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                                          | Module Disable  | e bit             |                 |                 |       |  |  |  |  |

#### ~

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0        | R/W-0           | R/W-0                                                          | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |  |

|------------------------------------|------------|-----------------|----------------------------------------------------------------|-----------------------------------------|------------------|----------|-------|--|--|--|

| _                                  | —          |                 | RP39R<5:0>                                                     |                                         |                  |          |       |  |  |  |

| bit 15                             |            |                 |                                                                |                                         |                  |          | bit 8 |  |  |  |

|                                    |            |                 |                                                                |                                         |                  |          |       |  |  |  |

| U-0                                | U-0        | R/W-0           | R/W-0                                                          | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |  |

| —                                  | —          |                 |                                                                | RP38                                    | R<5:0>           |          |       |  |  |  |

| bit 7                              |            |                 |                                                                |                                         |                  |          | bit 0 |  |  |  |

|                                    |            |                 |                                                                |                                         |                  |          |       |  |  |  |

| Legend:                            |            |                 |                                                                |                                         |                  |          |       |  |  |  |

| R = Readable                       | e bit      | W = Writable    | bit                                                            | U = Unimplen                            | nented bit, read | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set |            |                 |                                                                | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |  |

|                                    |            |                 |                                                                |                                         |                  |          |       |  |  |  |

| bit 15-14                          | Unimplemer | nted: Read as ' | 0'                                                             |                                         |                  |          |       |  |  |  |

| bit 13-8                           | RP39R<5:0> | : Peripheral Ou | Peripheral Output Function is Assigned to RP39 Output Pin bits |                                         |                  |          |       |  |  |  |

### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|------------|-------|-------|-------|-------|-------|

| —      | —   | RP41R<5:0> |       |       |       |       |       |

| bit 15 |     |            |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

## 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

| R/W-0         | R/W-0                               | R/W-0                                          | U-0        | U-0              | U-0             | U-0                | U-0    |  |  |  |

|---------------|-------------------------------------|------------------------------------------------|------------|------------------|-----------------|--------------------|--------|--|--|--|

| FRMEN         | SPIFSD                              | FRMPOL                                         | —          | —                | _               | —                  | _      |  |  |  |

| bit 15        |                                     |                                                |            |                  |                 |                    | bit 8  |  |  |  |

|               |                                     |                                                |            |                  |                 |                    |        |  |  |  |

| U-0           | U-0                                 | U-0                                            | U-0        | U-0              | U-0             | R/W-0              | R/W-0  |  |  |  |

| _             | <u> </u>                            | —                                              | _          |                  | _               | FRMDLY             | SPIBEN |  |  |  |

| bit 7         |                                     |                                                |            |                  |                 |                    | bit 0  |  |  |  |

|               |                                     |                                                |            |                  |                 |                    |        |  |  |  |

| Legend:       |                                     |                                                |            |                  |                 |                    |        |  |  |  |

| R = Readable  | e bit                               | W = Writable b                                 | pit        | U = Unimpler     | nented bit, rea | ad as '0'          |        |  |  |  |

| -n = Value at | POR                                 | '1' = Bit is set                               |            | '0' = Bit is cle | ared            | x = Bit is unknown |        |  |  |  |

|               |                                     |                                                |            |                  |                 |                    |        |  |  |  |

| bit 15        | FRMEN: Fra                          | FRMEN: Framed SPIx Support bit                 |            |                  |                 |                    |        |  |  |  |

|               |                                     | SPIx support is e<br>SPIx support is d         |            | x pin is used as | Frame Sync      | oulse input/outpu  | it)    |  |  |  |

| bit 14        | SPIFSD: Fra                         | SPIFSD: Frame Sync Pulse Direction Control bit |            |                  |                 |                    |        |  |  |  |

|               |                                     | ync pulse input (<br>ync pulse output          |            |                  |                 |                    |        |  |  |  |

| bit 13        | FRMPOL: Fr                          | FRMPOL: Frame Sync Pulse Polarity bit          |            |                  |                 |                    |        |  |  |  |

|               | 1 = Frame Sync pulse is active-high |                                                |            |                  |                 |                    |        |  |  |  |

|               |                                     | ync pulse is activ                             |            |                  |                 |                    |        |  |  |  |

| bit 12-2      | -                                   | nted: Read as '0                               |            |                  |                 |                    |        |  |  |  |

| bit 1         |                                     | FRMDLY: Frame Sync Pulse Edge Select bit       |            |                  |                 |                    |        |  |  |  |

|               |                                     | ync pulse coincio<br>ync pulse preceo          |            |                  |                 |                    |        |  |  |  |

| bit 0         | SPIBEN: En                          | hanced Buffer Er                               | nable bit  |                  |                 |                    |        |  |  |  |

|               |                                     | d buffer is enable                             |            |                  |                 |                    |        |  |  |  |

|               | 0 = Enhance                         | d buffer is disabl                             | ed (Standa | rd mode)         |                 |                    |        |  |  |  |

|               |                                     |                                                |            |                  |                 |                    |        |  |  |  |

### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

## REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

| R/W-0                             | R/W-0 | R/W-0 | R/W-0          | R/W-0           | R/W-0    | R/W-0 | R/W-0 |

|-----------------------------------|-------|-------|----------------|-----------------|----------|-------|-------|

| CSS15                             | CSS14 | CSS13 | CSS12          | CSS11           | CSS10    | CSS9  | CSS8  |

| bit 15                            |       |       |                | ·               | •        | ·     | bit 8 |

|                                   |       |       |                |                 |          |       |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0          | R/W-0           | R/W-0    | R/W-0 | R/W-0 |

| CSS7                              | CSS6  | CSS5  | CSS4           | CSS3            | CSS2     | CSS1  | CSS0  |

| bit 7                             |       |       |                | •               |          | bit ( |       |

|                                   |       |       |                |                 |          |       |       |

| Legend:                           |       |       |                |                 |          |       |       |

| R = Readable bit W = Writable bit |       | bit   | U = Unimple    | mented bit, rea | d as '0' |       |       |

| -n = Value at F                   |       |       | x = Bit is unk | nown            |          |       |       |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

# REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

| R/W-0            | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | R/W-0                                                                                                        | R/W-0            | R/W-0           | R/W-0   |

|------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------|

| PTGCLK2          | PTGCLK1                                                                                                                    | PTGCLK0                                                                           | PTGDIV4                                                                                                                                           | PTGDIV3                                                                                                      | PTGDIV2          | PTGDIV1         | PTGDIV0 |

| bit 15           | 1                                                                                                                          | 1                                                                                 | 1                                                                                                                                                 |                                                                                                              |                  |                 | bit     |

| R/W-0            | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | U-0                                                                                                          | R/W-0            | R/W-0           | R/W-0   |

| PTGPWD3          | PTGPWD2                                                                                                                    | PTGPWD1                                                                           | PTGPWD0                                                                                                                                           | _                                                                                                            | PTGWDT2          | PTGWDT1         | PTGWDTC |

| bit 7            |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 | bit     |

| Legend:          |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 |         |

| R = Readable bit |                                                                                                                            | W = Writable                                                                      | bit                                                                                                                                               | U = Unimpler                                                                                                 | mented bit, read | l as '0'        |         |

| -n = Value at F  | POR                                                                                                                        | '1' = Bit is set                                                                  |                                                                                                                                                   | '0' = Bit is cle                                                                                             | ared             | x = Bit is unkr | nown    |

| bit 15-13        | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                    |                                                                                   | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc                                                       | BCLK<br>PCLK<br>ICLK<br>D<br>DSC                                                                             |                  |                 |         |

| bit 12-8         | PTGDIV<4:0> 11111 = Divic 11110 = Divic                                                                                    | de-by-31<br>de-by-2                                                               | Clock Presca                                                                                                                                      | ler (divider) bi                                                                                             | ts               |                 |         |

| bit 7-4          | PTGPWD<3:0<br>1111 = All trig<br>1110 = All trig<br>0001 = All trig                                                        | <b>D&gt;:</b> PTG Trigge<br>gger outputs ar<br>gger outputs ar<br>gger outputs ar | e 16 PTG cloc<br>e 15 PTG cloc<br>e 2 PTG clock                                                                                                   | k cycles wide<br>k cycles wide<br>cycles wide                                                                |                  |                 |         |

| bit 3            | -                                                                                                                          | ted: Read as '                                                                    |                                                                                                                                                   |                                                                                                              |                  |                 |         |

| bit 2-0          | PTGWDT<2:0<br>111 = Watcho<br>110 = Watcho<br>101 = Watcho<br>011 = Watcho<br>011 = Watcho<br>010 = Watcho<br>010 = Watcho |                                                                                   | Watchdog Tir<br>ime-out after 5<br>ime-out after 2<br>ime-out after 1<br>ime-out after 3<br>ime-out after 3<br>ime-out after 1<br>ime-out after 8 | 12 PTG clock<br>56 PTG clock<br>28 PTG clock<br>4 PTG clocks<br>2 PTG clocks<br>6 PTG clocks<br>6 PTG clocks | S<br>S           | 5               |         |

# REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                                                  | U-0              | U-0                                    | U-0              | R/W-0                        | U-0              | U-0            |  |  |

|-----------------|--------------------------------------------------------|------------------|----------------------------------------|------------------|------------------------------|------------------|----------------|--|--|

|                 | CVR2OE <sup>(1)</sup>                                  | _                |                                        | _                | VREFSEL                      |                  | _              |  |  |

| bit 15          |                                                        |                  |                                        |                  |                              |                  | bit            |  |  |

| <b>D</b> 444 0  | DANIO                                                  |                  | <b>D</b> 444.0                         | <b>D</b> 444 0   | DAALO                        | DAMA             | <b>D</b> 444 0 |  |  |

| R/W-0           | R/W-0                                                  | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0            | R/W-0          |  |  |

| CVREN           | CVR10E <sup>(1)</sup>                                  | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1             | CVR0           |  |  |

| bit 7           |                                                        |                  |                                        |                  |                              |                  | bit            |  |  |

| Legend:         |                                                        |                  |                                        |                  |                              |                  |                |  |  |

| R = Readable    | bit                                                    | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'           |                |  |  |

| -n = Value at F | POR                                                    | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn  | iown           |  |  |

|                 |                                                        |                  |                                        |                  |                              |                  |                |  |  |

| bit 15          | Unimplement                                            |                  |                                        |                  |                              |                  |                |  |  |

| bit 14          |                                                        | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                  |                |  |  |

|                 |                                                        |                  | nected to the C<br>onnected from       |                  | nin                          |                  |                |  |  |

| bit 13-11       | Unimplement                                            |                  |                                        |                  | <b>F</b>                     |                  |                |  |  |

| bit 10          | -                                                      |                  | age Reference                          | e Select bit     |                              |                  |                |  |  |

|                 | 1 = CVREFIN = VREF+                                    |                  |                                        |                  |                              |                  |                |  |  |

|                 | 0 = CVREFIN is                                         | s generated by   | y the resistor ne                      | etwork           |                              |                  |                |  |  |

| bit 9-8         | Unimplement                                            | ed: Read as '    | 0'                                     |                  |                              |                  |                |  |  |

| bit 7           | CVREN: Comparator Voltage Reference Enable bit         |                  |                                        |                  |                              |                  |                |  |  |

|                 |                                                        |                  | erence circuit is<br>erence circuit is |                  | wn                           |                  |                |  |  |

| bit 6           | CVR1OE: Co                                             | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                  |                |  |  |

|                 |                                                        |                  | n the CVREF1C                          |                  | n                            |                  |                |  |  |

| bit 5           | CVRR: Comparator Voltage Reference Range Selection bit |                  |                                        |                  |                              |                  |                |  |  |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3                           | •                |                                        |                  |                              |                  |                |  |  |

| bit 4           | CVRSS: Com                                             | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                  |                |  |  |

|                 |                                                        | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                  |                |  |  |

| bit 3-0         | CVR<3:0> Co                                            | mparator Volt    | age Reference                          | Value Select     | ion $0 \leq CVR < 3$ :       | $0> \le 15$ bits |                |  |  |

|                 | When CVRR =                                            |                  | (CVRSRC)                               |                  |                              |                  |                |  |  |

|                 | When CVRR = CVREFIN = (CV                              | = 0:             |                                        | $(\mathbf{C})$   |                              |                  |                |  |  |

## REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       | N         | <b>IILLIMETER</b> | S    |

|--------------------------|-------------|-----------|-------------------|------|

| Dimension                | Limits      | MIN       | NOM               | MAX  |

| Number of Pins           | N           |           | 28                |      |

| Pitch                    | е           |           | 1.27 BSC          |      |

| Overall Height           | Α           | -         | -                 | 2.65 |

| Molded Package Thickness | A2          | 2.05      | -                 | -    |

| Standoff §               | A1          | 0.10      | -                 | 0.30 |

| Overall Width            | E           |           | 10.30 BSC         |      |

| Molded Package Width     | E1 7.50 BSC |           |                   |      |

| Overall Length           | D           | 17.90 BSC |                   |      |

| Chamfer (Optional)       | h           | 0.25      | -                 | 0.75 |

| Foot Length              | L           | 0.40      | -                 | 1.27 |

| Footprint                | L1          | 1.40 REF  |                   |      |

| Lead Angle               | Θ           | 0°        | -                 | -    |

| Foot Angle               | $\varphi$   | 0°        | -                 | 8°   |

| Lead Thickness           | С           | 0.18      | -                 | 0.33 |

| Lead Width               | b           | 0.31      | -                 | 0.51 |

| Mold Draft Angle Top     | α           | 5°        | -                 | 15°  |

| Mold Draft Angle Bottom  | β           | 5°        | -                 | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

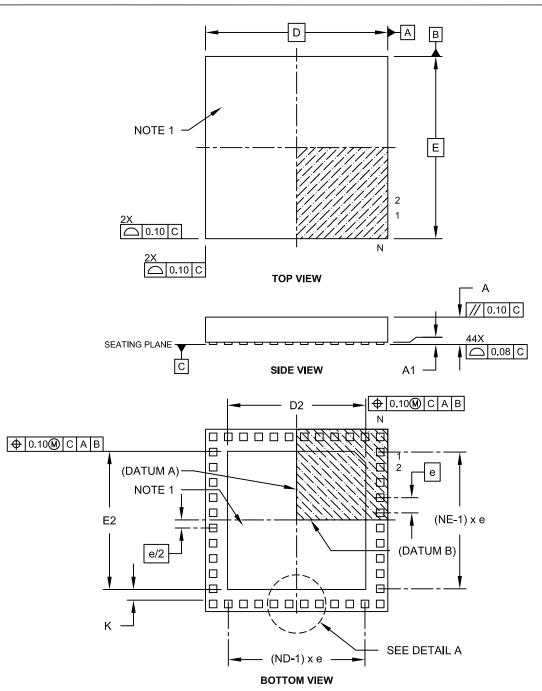

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

# **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).<br>Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

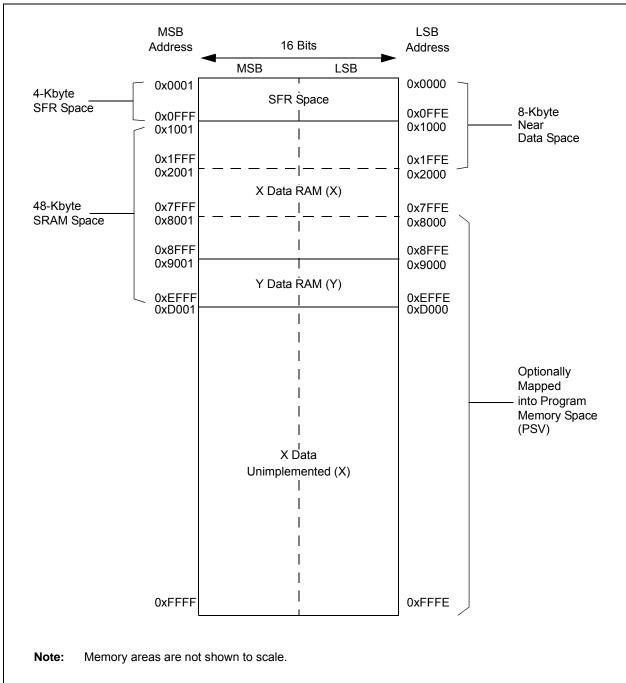

| Section 4.0 "Memory<br>Organization"                                                                                                                                    | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).<br>Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and<br>OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register<br>Map (see Table 4-10).<br>Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map<br>(see Table 4-13).<br>Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map<br>(see Table 4-14).<br>Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map<br>(see Table 4-15).<br>Updated the second note in Section 4.7.1 "Bit-Reversed Addressing<br>Implementation". |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).<br>Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                                                                                                                                                                                                                                                                        |

TABLE A-2: MAJOR SECTION UPDATES

| DMAxSTAH (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start Address A, High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 144                                                                                                                                                                                                            |

| DMAxSTAL (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

| Start Address A, Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 144                                                                                                                                                                                                            |

| DMAxSTBH (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

| Start Address B, High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 145                                                                                                                                                                                                            |

| DMAxSTBL (DMA Channel x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |