Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K × 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

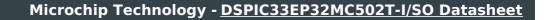

#### **Pin Diagrams (Continued)**

#### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: CI                                          | PU STATUS I                                                                                                    | REGISTER                    |                          |                    |                   |               |  |  |  |  |  |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|--|--|--|--|--|

| R/W-0                  | R/W-0                                                | R/W-0                                                                                                          | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |  |  |  |  |  |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                                                                                            | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |  |  |  |  |  |

| bit 15                 |                                                      |                                                                                                                |                             |                          |                    |                   | bit 8         |  |  |  |  |  |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                                                                                         | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |  |  |  |  |  |

| IPL2                   | IPL1                                                 | IPL0                                                                                                           | RA                          | N                        | OV                 | Z                 | С             |  |  |  |  |  |

| bit 7                  | ·                                                    | •                                                                                                              |                             | •                        |                    |                   | bit (         |  |  |  |  |  |

| Legend:                |                                                      | C = Clearable                                                                                                  | e bit                       |                          |                    |                   |               |  |  |  |  |  |

| R = Readab             | le bit                                               | W = Writable                                                                                                   | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |  |  |  |  |  |

| -n = Value a           | t POR                                                | '1'= Bit is set                                                                                                |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |  |  |  |  |  |

|                        |                                                      |                                                                                                                |                             |                          |                    |                   |               |  |  |  |  |  |

| bit 15                 | OA: Accumul                                          | ator A Overflov                                                                                                | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |  |

|                        | 1 = Accumula                                         | ator A has over                                                                                                | flowed                      |                          |                    |                   |               |  |  |  |  |  |

|                        | 0 = Accumula                                         | ator A has not o                                                                                               | verflowed                   |                          |                    |                   |               |  |  |  |  |  |

| bit 14                 | OB: Accumul                                          | ator B Overflov                                                                                                | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |  |

|                        | 1 = Accumula                                         | 1 = Accumulator B has overflowed                                                                               |                             |                          |                    |                   |               |  |  |  |  |  |

|                        |                                                      | ator B has not c                                                                                               |                             |                          |                    |                   |               |  |  |  |  |  |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                                                                                               | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |  |  |  |

|                        |                                                      | ator A is saturat<br>ator A is not sat                                                                         |                             | en saturated at          | some time          |                   |               |  |  |  |  |  |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                                                                                               | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |  |  |  |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat                                                                         | ted or has bee              |                          | some time          |                   |               |  |  |  |  |  |

| bit 11                 |                                                      |                                                                                                                |                             | vorflow Status           | ы#(1)              |                   |               |  |  |  |  |  |

|                        |                                                      | DAB: OA    OB Combined Accumulator Overflow Status bit <sup>(1)</sup><br>= Accumulators A or B have overflowed |                             |                          |                    |                   |               |  |  |  |  |  |

|                        |                                                      | ccumulators A                                                                                                  |                             | erflowed                 |                    |                   |               |  |  |  |  |  |

| bit 10                 |                                                      | B Combined Ad                                                                                                  |                             |                          | (1)                |                   |               |  |  |  |  |  |

|                        |                                                      |                                                                                                                |                             |                          | urated at some     | time              |               |  |  |  |  |  |

|                        | 0 = Neither A                                        | ccumulators A                                                                                                  | or B are satur              | ated                     |                    |                   |               |  |  |  |  |  |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>                                                                                      |                             |                          |                    |                   |               |  |  |  |  |  |

|                        | 1 = DO <b>loop is</b>                                | s in progress                                                                                                  |                             |                          |                    |                   |               |  |  |  |  |  |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                                                                                               | S                           |                          |                    |                   |               |  |  |  |  |  |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                                                                                                | orrow bit                   |                          |                    |                   |               |  |  |  |  |  |

|                        |                                                      | out from the 4th sult occurred                                                                                 | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |  |  |  |  |  |

|                        | 0 = No carry                                         |                                                                                                                |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |  |  |  |  |  |

|                        | his bit is available                                 |                                                                                                                |                             |                          |                    |                   | -             |  |  |  |  |  |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                                                                                                |                             |                          |                    |                   |               |  |  |  |  |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| IABLE 4-2  | 23: E | CAN1 I         | REGIST    | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|----------------|-----------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15         | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  | 046E EID<15:8> |           |        |        |        |        |               | EID<7:0>  |          |          |        |        |        |        | xxxx  |       |               |

| C1RXF12SID | 0470  |                | SID<10:3> |        |        |        |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472  |                | EID<15:8> |        |        |        |        |               | EID<7:0>  |          |          |        |        |        | xxxx   |       |       |               |

| C1RXF13SID | 0474  |                |           |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |                |           |        | EID<   | :15:8> |        |               |           | EID<7:0> |          |        |        |        |        |       | xxxx  |               |

| C1RXF14SID | 0478  |                |           |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  | EID<15:8>      |           |        |        |        |        |               |           |          | EID<     | 7:0>   |        |        |        | xxxx  |       |               |

| C1RXF15SID | 047C  | SID<10:3>      |           |        |        |        |        |               | SID<2:0>  |          | _        | EXIDE  | _      | EID<1  | 7:16>  | xxxx  |       |               |

| C1RXF15EID | 047E  | E EID<15:8>    |           |        |        |        |        |               |           |          | EID<     | 7:0>   |        |        |        | xxxx  |       |               |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | —      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | —     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | -      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0                                                                                                                                               | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|-------|

| —                                  | —                                                                                                                                                 |                  |       | RP57              | R<5:0>           |                 |       |

| bit 15                             |                                                                                                                                                   |                  |       |                   |                  |                 | bit 8 |

|                                    |                                                                                                                                                   |                  |       |                   |                  |                 |       |

| U-0                                | U-0                                                                                                                                               | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| _                                  | —                                                                                                                                                 |                  |       | RP56              | R<5:0>           |                 |       |

| bit 7                              |                                                                                                                                                   |                  |       |                   |                  |                 | bit 0 |

|                                    |                                                                                                                                                   |                  |       |                   |                  |                 |       |

| Legend:                            |                                                                                                                                                   |                  |       |                   |                  |                 |       |

| R = Readable I                     | bit                                                                                                                                               | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P                    | OR                                                                                                                                                | '1' = Bit is set | :     | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

|                                    |                                                                                                                                                   |                  |       |                   |                  |                 |       |

| bit 15-14                          | Unimplemen                                                                                                                                        | ted: Read as '   | 0'    |                   |                  |                 |       |

| bit 13-8                           | bit 13-8 <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |       |                   |                  |                 |       |

| bit 7-6 Unimplemented: Read as '0' |                                                                                                                                                   |                  |       |                   |                  |                 |       |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

#### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|               | 23-2: Al | DICONZ. ADCI                                         | CONTROL REG           | ISIER Z         |                   |                  |                 |

|---------------|----------|------------------------------------------------------|-----------------------|-----------------|-------------------|------------------|-----------------|

| R/W-0         | R/W-     | 0 R/W-0                                              | U-0                   | U-0             | R/W-0             | R/W-0            | R/W-0           |

| VCFG2         | VCFO     | G1 VCFG0                                             | —                     | —               | CSCNA             | CHPS1            | CHPS0           |

| bit 15        |          |                                                      |                       |                 |                   |                  | bit             |

| R-0           | R/W-     | 0 R/W-0                                              | R/W-0                 | R/W-0           | R/W-0             | R/W-0            | R/W-0           |

| BUFS          | SMP      |                                                      | SMPI2                 | SMPI1           | SMPI0             | BUFM             | ALTS            |

| bit 7         | OWIT     |                                                      |                       |                 |                   | Borim            | bit             |

| Legend:       |          |                                                      |                       |                 |                   |                  |                 |

| R = Readable  | , hit    | W = Writable                                         | bit I                 | l – Llnimolo    | monted hit rea    | d oo 'O'         |                 |

|               |          |                                                      |                       |                 | mented bit, read  |                  |                 |

| -n = Value at | POR      | '1' = Bit is se                                      | t 't                  | )' = Bit is cle | eared             | x = Bit is unkr  | nown            |

| bit 15-13     | VCFG<2   | 2:0>: Converter Vol                                  | tage Reference C      | onfiguration    | bits              |                  |                 |

|               | Value    | VREFH                                                | VREFL                 |                 |                   |                  |                 |

|               | 000      | Avdd                                                 | Avss                  |                 |                   |                  |                 |

|               | 001      | External VREF+                                       | Avss                  |                 |                   |                  |                 |

|               | 010      | Avdd                                                 | External VREF-        |                 |                   |                  |                 |

|               | 011      | External VREF+                                       | External VREF-        |                 |                   |                  |                 |

|               | 1xx      | Avdd                                                 | Avss                  |                 |                   |                  |                 |

| bit 12-11     | Unimple  | emented: Read as                                     | ʻ0'                   |                 |                   |                  |                 |

| bit 10        | CSCNA    | Input Scan Select                                    | bit                   |                 |                   |                  |                 |

|               |          | ns inputs for CH0+                                   |                       | JXA             |                   |                  |                 |

|               | 0 = Does | s not scan inputs                                    | <b>C</b> .            |                 |                   |                  |                 |

| bit 9-8       | CHPS<1   | :0>: Channel Sele                                    | ct bits               |                 |                   |                  |                 |

|               |          | mode (AD21B = 1)                                     |                       | bits are Uni    | mplemented ar     | id are Read as   | <u>'0':</u>     |

|               |          | nverts CH0, CH1, C                                   |                       |                 |                   |                  |                 |

|               |          | nverts CH0 and CH<br>nverts CH0                      | 11                    |                 |                   |                  |                 |

| bit 7         |          | Buffer Fill Status bit                               | (oply valid when F    |                 |                   |                  |                 |

|               |          | C is currently filling t                             |                       |                 | ne user applicat  | ion should acco  | ee data in th   |

|               |          | half of the buffer                                   | ne second hall of     | ule bullet, u   | ie usei applicat  |                  | 555 Uala III li |

|               |          | C is currently filling                               | the first half of the | e buffer; the   | e user applicatio | on should acce   | ss data in th   |

|               | seco     | ond half of the buffe                                | er                    |                 |                   |                  |                 |

| bit 6-2       | SMPI<4   | :0>: Increment Rate                                  | e bits                |                 |                   |                  |                 |

|               |          | DDMAEN = 0:                                          |                       |                 |                   |                  |                 |

|               |          | Generates interrup                                   |                       |                 |                   |                  |                 |

|               | x1110 =  | Generates interrup                                   | ot after completion   | of every 18     | oth sample/conv   | ersion operation | on              |

|               | •        |                                                      |                       |                 |                   |                  |                 |

|               | •        |                                                      |                       |                 |                   |                  |                 |

|               |          | Generates interrup                                   |                       |                 |                   |                  | n               |

|               |          | Generates interrup                                   | ot after completion   | of every sa     | imple/conversion  | on operation     |                 |

|               |          | $\frac{\text{DDMAEN} = 1}{\text{Increments the DN}}$ | 1A address after a    | omplotion o     | of overy 32nd s   | mplo/convorsi    | on operation    |

|               |          | Increments the DN                                    |                       |                 |                   |                  |                 |

|               | •        |                                                      |                       |                 |                   |                  |                 |

|               | •        |                                                      |                       |                 |                   |                  |                 |

|               | •        |                                                      |                       |                 |                   | ., .             |                 |

|               | 00001 -  | Increments the DI                                    | "A address offer a    | omplation o     | t avany 2nd aar   |                  |                 |

#### . . ACOND. ADCA CONTROL DECISTED 2

#### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | CREF: Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                             |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

- 1111 = FLT4 1110 = FLT2 1101 = PTGO19 1100 = PTGO18 1011 = Reserved 1010 = Reserved 1001 = Reserved 1000 = Reserved 0111 = Reserved 0110 = Reserved 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L 0001 = PWM1H 0000 = PWM1L

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                        | U-0              | U-0                                    | U-0              | R/W-0                        | U-0              | U-0            |

|-----------------|------------------------------|------------------|----------------------------------------|------------------|------------------------------|------------------|----------------|

|                 | CVR2OE <sup>(1)</sup>        | _                |                                        | _                | VREFSEL                      | _                | _              |

| bit 15          |                              |                  |                                        |                  |                              |                  | bit            |

| <b>D</b> 444 0  | DANIO                        |                  | <b>D</b> 444.0                         | <b>D</b> 444 0   | DAALO                        | DAMA             | <b>D</b> 444 0 |

| R/W-0           | R/W-0                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0            | R/W-0          |

| CVREN           | CVR10E <sup>(1)</sup>        | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1             | CVR0           |

| bit 7           |                              |                  |                                        |                  |                              |                  | bit            |

| Legend:         |                              |                  |                                        |                  |                              |                  |                |

| R = Readable    | bit                          | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'           |                |

| -n = Value at F | POR                          | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn  | iown           |

|                 |                              |                  |                                        |                  |                              |                  |                |

| bit 15          | Unimplement                  |                  |                                        |                  |                              |                  |                |

| bit 14          |                              | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | nected to the C<br>onnected from       |                  | nin                          |                  |                |

| bit 13-11       | Unimplement                  |                  |                                        |                  | <b>F</b>                     |                  |                |

| bit 10          | -                            |                  | age Reference                          | e Select bit     |                              |                  |                |

|                 | 1 = CVREFIN =                | -                | U                                      |                  |                              |                  |                |

|                 | 0 = CVREFIN is               | s generated by   | y the resistor ne                      | etwork           |                              |                  |                |

| bit 9-8         | Unimplement                  | ed: Read as '    | 0'                                     |                  |                              |                  |                |

| bit 7           |                              |                  | e Reference E                          |                  |                              |                  |                |

|                 |                              |                  | erence circuit is<br>erence circuit is |                  | wn                           |                  |                |

| bit 6           | CVR1OE: Co                   | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | n the CVREF1C                          |                  | n                            |                  |                |

| bit 5           | CVRR: Comp                   | arator Voltage   | Reference Ra                           | nge Selection    | n bit                        |                  |                |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3 | •                |                                        |                  |                              |                  |                |

| bit 4           | CVRSS: Com                   | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                  |                |

|                 |                              | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                  |                |

| bit 3-0         | CVR<3:0> Co                  | mparator Volt    | age Reference                          | Value Select     | ion $0 \leq CVR < 3$ :       | $0> \le 15$ bits |                |

|                 | When CVRR =                  |                  | (CVRSRC)                               |                  |                              |                  |                |

|                 | When CVRR = CVREFIN = (CV    | = 0:             |                                        | $(\mathbf{C})$   |                              |                  |                |

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

| Base<br>Instr<br># Assembly<br>Mnemonic<br>9 BTG |        |             | Assembly Syntax               | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------------------------------------|--------|-------------|-------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

|                                                  |        | BTG f,#bit4 |                               | Bit Toggle f                                               | 1             | 1                             | None                     |

|                                                  |        | BTG         | Ws,#bit4                      | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                                               | BTSC   | BTSC        | f,#bit4                       | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  |        | BTSC        | Ws,#bit4                      | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                                               | BTSS   | BTSS        | f,#bit4                       | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  |        | BTSS        | Ws,#bit4                      | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                                               | BTST   | BTST        | f,#bit4                       | Bit Test f                                                 | 1             | 1                             | Z                        |

|                                                  |        | BTST.C      | Ws,#bit4                      | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                                                  |        | BTST.Z      | Ws,#bit4                      | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                                                  |        | BTST.C      | Ws,Wb                         | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                                                  |        | BTST.Z      | Ws,Wb                         | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                                               | BTSTS  | BTSTS       | f,#bit4                       | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                                                  |        | BTSTS.C     | Ws,#bit4                      | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                                                  |        | BTSTS.Z     | Ws,#bit4                      | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                                               | CALL   | CALL        | lit23                         | Call subroutine                                            | 2             | 4                             | SFA                      |

|                                                  |        | CALL        | Wn                            | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                                                  |        | CALL.L      | Wn                            | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                                               | CLR    | CLR         | f                             | f = 0x0000                                                 | 1             | 1                             | None                     |

|                                                  |        | CLR         | WREG                          | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                                                  |        | CLR         | Ws                            | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                                                  |        | CLR         | Acc, Wx, Wxd, Wy, Wyd, AWB(1) | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                                               | CLRWDT | CLRWDT      |                               | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17                                               | COM    | СОМ         | f                             | $f = \bar{f}$                                              | 1             | 1                             | N,Z                      |

|                                                  |        | COM         | f,WREG                        | WREG = $\overline{f}$                                      | 1             | 1                             | N,Z                      |

|                                                  |        | СОМ         | Ws,Wd                         | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                                               | CP     | CP          | f                             | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                                                  | 01     | CP          | Wb,#lit8                      | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                                                  |        | CP          | Wb,Ws                         | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                                               | CP0    | CPO         | f                             | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

| 10                                               | 010    | CPO         | Ws                            | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                                               | CPB    | CPB         | f                             | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                                                  | 012    | CPB         | Wb,#lit8                      | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                                                  |        | CPB         | Wb,Ws                         | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                                               | CPSEQ  | CPSEQ       | Wb,Wn                         | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  | CPBEQ  | CPBEQ       | Wb,Wn,Expr                    | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                                               | CPSGT  | CPSGT       | Wb,Wn                         | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  | CPBGT  | CPBGT       | Wb,Wn,Expr                    | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                                               | CPSLT  | CPSLT       | Wb,Wn                         | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  | CPBLT  | CPBLT       | Wb,Wn,Expr                    | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                                               | CPSNE  | CPSNE       | Wb,Wn                         | Compare Wb with Wn, skip if $\neq$                         | 1             | 1<br>(2 or 3)                 | None                     |

|                                                  | CPBNE  | CPBNE       | Wb,Wn,Expr                    | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| <b>TABLE 28-2:</b> | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED | ) |

|--------------------|-----------------------------------|-----------|---|

|                    |                                   | CONTINUED | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

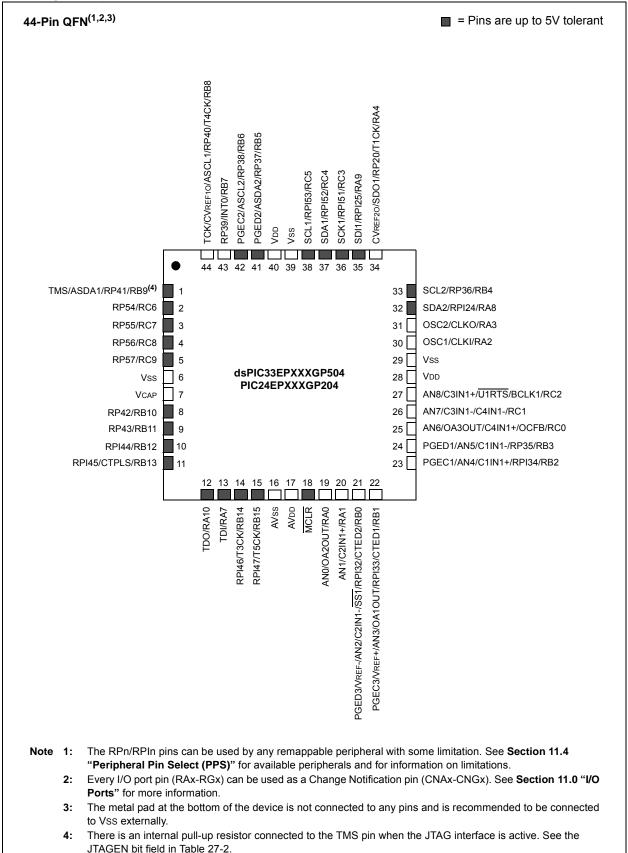

#### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHAR      | ACTERIST | rics                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                                         |

|--------------|----------|----------------------------------------------------|-------------------------------------------------------|------|-------|---------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic <sup>(1)</sup>                      | Тур. <sup>(2)</sup>                                   | Max. | Units | Conditions                                              |

| TQ30         | TQUL     | Quadrature Input Low Time                          | 6 Tcy                                                 |      | ns    |                                                         |

| TQ31         | TQUH     | Quadrature Input High Time                         | 6 Tcy                                                 | —    | ns    |                                                         |

| TQ35         | TQUIN    | Quadrature Input Period                            | 12 TCY                                                | _    | ns    |                                                         |

| TQ36         | TQUP     | Quadrature Phase Period                            | 3 TCY                                                 | —    | ns    |                                                         |

| TQ40         | TQUFL    | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy                                           | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

| TQ41         | TQUFH    | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy                                           | —    | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                    |       |                                |  |

|--------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------|--------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max.               | Units | Conditions                     |  |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                                                                                                                                                                                                                                                                       |                     | Lesser of FP or 15 | MHz   | (Note 3)                       |  |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —                                                                                                                                                                                                                                                                                       |                     |                    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                                                                                                       |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       |                     | _                  | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20                 | ns    |                                |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                      |                     | _                  | ns    |                                |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                                                                                                      |                     |                    | ns    |                                |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                                                                                                      |                     | —                  | ns    |                                |  |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     |                     | —                  | ns    |                                |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | _                   | 50                 | ns    | (Note 4)                       |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            | _                   | _                  | ns    | (Note 4)                       |  |