#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc502t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

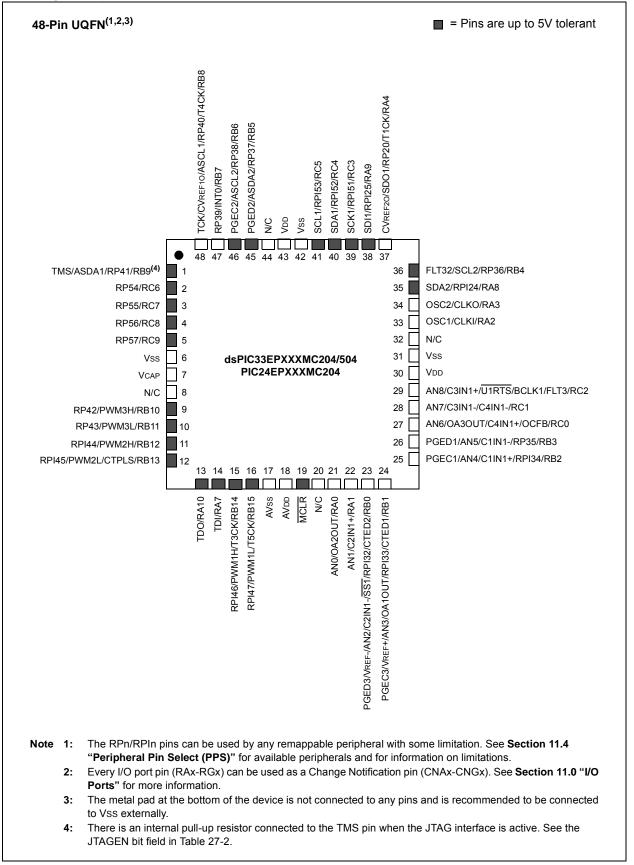

## Pin Diagrams (Continued)

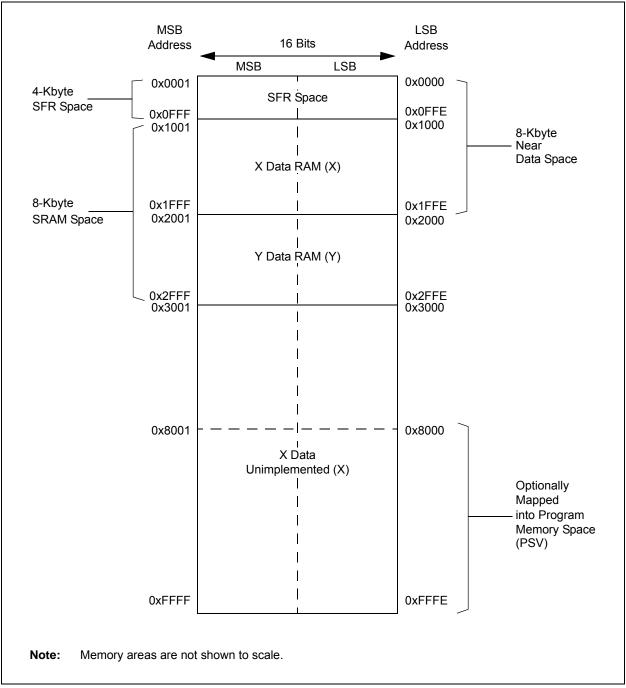

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                         |                                   |  |  |  |  |  |

|--------------|------------------------|-------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|--|--|--|--|--|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit, read as '0'      |                                   |  |  |  |  |  |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                    | x = Bit is unknown                |  |  |  |  |  |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                         |                                   |  |  |  |  |  |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                         |                                   |  |  |  |  |  |

| bit 14       | •                      | mented: Read as '0'                                                           |                                         |                                   |  |  |  |  |  |

| bit 13       | -                      | imery Stop in Idle Mode bit <sup>(2</sup>                                     | 2)                                      |                                   |  |  |  |  |  |

|              |                        | ontinues module operation winues module operation in Id                       | hen device enters Idle mode<br>lle mode |                                   |  |  |  |  |  |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                         |                                   |  |  |  |  |  |

| bit 6        | TGATE:                 | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup>        |                                         |                                   |  |  |  |  |  |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                         |                                   |  |  |  |  |  |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                         |                                   |  |  |  |  |  |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>       |                                   |  |  |  |  |  |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                         |                                   |  |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                         |                                   |  |  |  |  |  |

|              | 01 = 1.8               |                                                                               |                                         |                                   |  |  |  |  |  |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                         |                                   |  |  |  |  |  |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                   |                                   |  |  |  |  |  |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                    |                                   |  |  |  |  |  |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                         |                                   |  |  |  |  |  |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e          | ffect on Timery operation; all ti |  |  |  |  |  |

|              |                        |                                                                               |                                         |                                   |  |  |  |  |  |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ole bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

## bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

## 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

## 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

| U-0                 | U-0                                                                                                                                | U-0                                      | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

|                     | —                                                                                                                                  | _                                        | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                                                                                                                    | •                                        |                                       | •                    | •                    | •                    | bit                  |  |  |  |

| R/W-0               | R/W-0                                                                                                                              | R/W-0                                    | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                | MSTEN                                    | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7               | CKF                                                                                                                                | WISTEN                                   | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |

|                     |                                                                                                                                    |                                          |                                       |                      |                      |                      |                      |  |  |  |

| Legend:             |                                                                                                                                    |                                          |                                       |                      |                      |                      |                      |  |  |  |

| R = Readabl         | le bit                                                                                                                             | W = Writable                             | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at       | t POR                                                                                                                              | '1' = Bit is se                          | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |

|                     |                                                                                                                                    |                                          |                                       |                      |                      |                      |                      |  |  |  |

| bit 15-13           | Unimplemen                                                                                                                         | ted: Read as                             | 0'                                    |                      |                      |                      |                      |  |  |  |

| bit 12              |                                                                                                                                    |                                          | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |

|                     |                                                                                                                                    | PIx clock is di                          | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |

| oit 11              |                                                                                                                                    | able SDOx Pir                            |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          |                                       | oin functions as     | s I/O                |                      |                      |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by the module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul> |                                          |                                       |                      |                      |                      |                      |  |  |  |

| bit 10              | MODE16: Wo                                                                                                                         | ord/Byte Comn                            | nunication Sele                       | ect bit              |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    | 1 = Communication is word-wide (16 bits) |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    | ication is byte-                         | . ,                                   |                      |                      |                      |                      |  |  |  |

| bit 9               |                                                                                                                                    | ata Input Sam                            | ole Phase bit                         |                      |                      |                      |                      |  |  |  |

|                     | Master mode                                                                                                                        | -                                        | end of data o                         | utout time           |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          | middle of data                        |                      |                      |                      |                      |  |  |  |

|                     | Slave mode:                                                                                                                        | ·                                        |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          | SPIx is used i                        | n Slave mode.        |                      |                      |                      |  |  |  |

| bit 8               |                                                                                                                                    | lock Edge Sele                           |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          |                                       |                      |                      | lle clock state (r   |                      |  |  |  |

| bit 7               |                                                                                                                                    |                                          | bit (Slave mo                         |                      |                      | ve clock state (i    |                      |  |  |  |

|                     |                                                                                                                                    | sused for Slav                           |                                       |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          |                                       | is controlled b      | by port function     |                      |                      |  |  |  |

| bit 6               | CKP: Clock F                                                                                                                       | Polarity Select                          | bit                                   |                      |                      |                      |                      |  |  |  |

|                     |                                                                                                                                    |                                          | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                                         | ter Mode Enat                            | ole bit                               |                      |                      |                      |                      |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                       |                                          |                                       |                      |                      |                      |                      |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                                                  | used in Frame                            | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |

|                     | his bit must be cl                                                                                                                 |                                          |                                       |                      |                      |                      |                      |  |  |  |

| <b>0</b>            |                                                                                                                                    |                                          |                                       |                      |                      |                      |                      |  |  |  |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R-0, HSC      | R-0, HSC                  | U-0             | U-0                                                            | U-0                                     | R/C-0, HS | R-0, HSC | R-0, HSC |

|---------------|---------------------------|-----------------|----------------------------------------------------------------|-----------------------------------------|-----------|----------|----------|

| ACKSTAT       | TRSTAT                    | _               | _                                                              | —                                       | BCL       | GCSTAT   | ADD10    |

| bit 15        |                           |                 |                                                                |                                         |           |          | bit 8    |

|               |                           |                 |                                                                |                                         |           |          |          |

| R/C-0, HS     | R/C-0, HS                 | R-0, HSC        | R/C-0, HSC                                                     | R/C-0, HSC                              | R-0, HSC  | R-0, HSC | R-0, HSC |

| IWCOL         | I2COV                     | D_A             | Р                                                              | S                                       | R_W       | RBF      | TBF      |

| bit 7         |                           |                 |                                                                |                                         |           |          | bit 0    |

|               |                           |                 |                                                                |                                         |           |          |          |

| Legend:       | Legend: C = Clearable bit |                 | HS = Hardware Settable bit HSC = Hardware Settable/Clearable I |                                         |           |          |          |

| R = Readabl   | e bit                     | W = Writable    | e bit                                                          | U = Unimplemented bit, read as '0'      |           |          |          |

| -n = Value at | POR                       | '1' = Bit is se | et                                                             | '0' = Bit is cleared x = Bit is unknown |           |          |          |

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

## 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0  | U-0  | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0   |

|--------|------|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | —    | PTGSIDL | PTGTOGL | _   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 | •    |         |         |     |                       | · · · · ·              | bit 8   |

|        |      |         |         |     |                       |                        |         |

| R/W-0  | HS-0 | U-0     | U-0     | U-0 | U-0                   | R/W-0                  |         |

| R/W-0   | HS-0    | U-0 | U-0 | U-0 | U-0 | R/V                    | V-0                    |

|---------|---------|-----|-----|-----|-----|------------------------|------------------------|

| PTGSTRT | PTGWDTO | —   | _   | —   | —   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7   |         |     |     |     |     |                        | bit 0                  |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  | PTGEN: Module Enable bit                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PTG module is enabled                                                                                                                                                                                                                                                                                    |

|         | 0 = PTG module is disabled                                                                                                                                                                                                                                                                                   |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| bit 13  | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                      |

| bit 12  | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul>                                                                                |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| bit 10  | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Triggers the PTG module</li> <li>0 = No action (clearing this bit will have no effect)</li> </ul>                                                                                                                                                                                               |

| bit 9   | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                                                                                                           |

|         | 1 = Enables Single-Step mode<br>0 = Disables Single-Step mode                                                                                                                                                                                                                                                |

| bit 8   | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)</li> <li>0 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written to those limit registers</li> </ul> |

| bit 7   | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                                                                                                             |

|         | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                                                                                                         |

| bit 6   | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = PTG Watchdog Timer has timed out</li> <li>0 = PTG Watchdog Timer has not timed out.</li> </ul>                                                                                                                                                                                                  |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| Note 1: | These bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                                                                                                     |

| 2:      | This bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                                                                                                 |

|         |                                                                                                                                                                                                                                                                                                              |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

#### 26.1 Overview

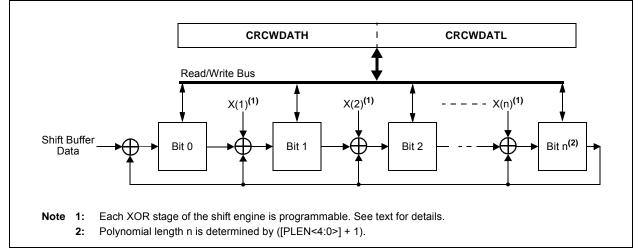

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

# TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |  |  |

## 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

NOTES:

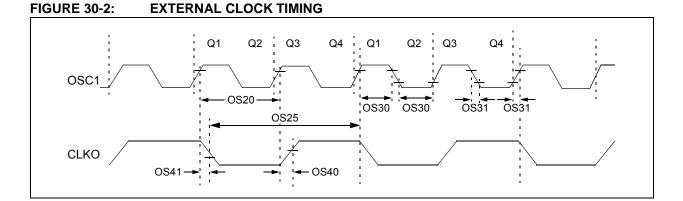

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |             |            |                               |

|--------------------|---------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|-------------------------------|

| Param<br>No.       | Symb          | Characteristic                                                                     | Min.                                                                                                                                                                                                                                                                                    | Conditions |             |            |                               |

| OS10               | Fin           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                                                                                                      | _          | 60          | MHz        | EC                            |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                                                                                                                                                               |            | 10<br>25    | MHz<br>MHz | XT<br>HS                      |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 8.33                                                                                                                                                                                                                                                                                    | _          | DC          | ns         | +125°C                        |

|                    |               | Tosc = 1/Fosc                                                                      | 7.14                                                                                                                                                                                                                                                                                    | _          | DC          | ns         | +85°C                         |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67                                                                                                                                                                                                                                                                                   | _          | DC          | ns         | +125°C                        |

|                    |               | Instruction Cycle Time <sup>(2)</sup>                                              | 14.28                                                                                                                                                                                                                                                                                   | _          | DC          | ns         | +85°C                         |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.45 x Tosc                                                                                                                                                                                                                                                                             | —          | 0.55 x Tosc | ns         | EC                            |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                                                                                                                                                                                                                                                       | —          | 20          | ns         | EC                            |

| OS40               | TckR          | CLKO Rise Time <sup>(3,4)</sup>                                                    | —                                                                                                                                                                                                                                                                                       | 5.2        | _           | ns         |                               |

| OS41               | TckF          | CLKO Fall Time <sup>(3,4)</sup>                                                    | —                                                                                                                                                                                                                                                                                       | 5.2        |             | ns         |                               |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —                                                                                                                                                                                                                                                                                       | 12         | _           | mA/V       | HS, VDD = 3.3V,<br>TA = +25°C |

|                    |               |                                                                                    | —                                                                                                                                                                                                                                                                                       | 6          | _           | mA/V       | XT, VDD = 3.3V,<br>TA = +25°C |

#### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized, but not tested in manufacturing.

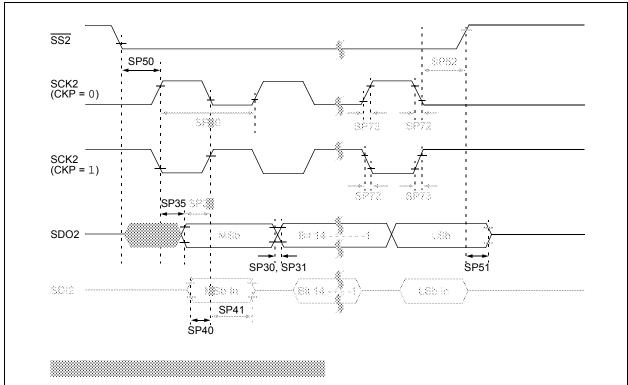

## FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        |                                                  |          |           |          |       |                                                 |

|--------------------|--------|--------------------------------------------------|----------|-----------|----------|-------|-------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                   | Min.     | Тур.      | Max.     | Units | Conditions                                      |

|                    |        | ADC A                                            | Accuracy | (12-Bit   | Mode)    |       |                                                 |

| AD20a              | Nr     | Resolution                                       | 12       | 2 Data Bi | its      | bits  |                                                 |

| AD21a              | INL    | Integral Nonlinearity                            | -2.5     |           | 2.5      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2) |

|                    |        |                                                  | -5.5     | —         | 5.5      | LSb   | +85°C $<$ TA $\leq$ +125°C (Note 2)             |

| AD22a              | DNL    | Differential Nonlinearity                        | -1       | _         | 1        | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)           |

|                    |        |                                                  | -1       | —         | 1        | LSb   | +85°C $<$ TA $\leq$ +125°C (Note 2)             |

| AD23a              | Gerr   | Gain Error <sup>(3)</sup>                        | -10      | _         | 10       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)           |

|                    |        |                                                  | -10      | _         | 10       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)               |

| AD24a              | EOFF   | Offset Error                                     | -5       | —         | 5        | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2) |

|                    |        |                                                  | -5       | —         | 5        | LSb   | +85°C < TA $\leq$ +125°C (Note 2)               |

| AD25a              | —      | Monotonicity                                     | —        |           |          |       | Guaranteed                                      |

|                    |        | Dynamic                                          | Performa | ance (12- | -Bit Mod | e)    |                                                 |

| AD30a              | THD    | Total Harmonic Distortion <sup>(3)</sup>         | _        | 75        |          | dB    |                                                 |

| AD31a              | SINAD  | Signal to Noise and<br>Distortion <sup>(3)</sup> | —        | 68        |          | dB    |                                                 |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup>    | —        | 80        | —        | dB    |                                                 |

| AD33a              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>            | —        | 250       | —        | kHz   |                                                 |

| AD34a              | ENOB   | Effective Number of Bits <sup>(3)</sup>          | 11.09    | 11.3      |          | bits  |                                                 |

## TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

3: Parameters are characterized but not tested in manufacturing.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

## 31.1 High-Temperature DC Characteristics

## TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                            |                              | Max MIPS                                                              |

|----------------|----------------------------|------------------------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)    | Temperature Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

| HDC5           | 3.0 to 3.6V <sup>(1)</sup> | -40°C to +150°C              | 40                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, may have degraded performance. Device functionality is tested but not characterized.

### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High-Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | _           | +150 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I   | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARA          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                |                              |     |     |   |                 |  |  |  |

|-------------------|-------------------------------------------------------|----------------|------------------------------|-----|-----|---|-----------------|--|--|--|

| Parameter<br>No.  | Symbol                                                | Characteristic | Min Typ Max Units Conditions |     |     |   |                 |  |  |  |

| Operating Voltage |                                                       |                |                              |     |     |   |                 |  |  |  |

| HDC10             | Supply Voltage                                        |                |                              |     |     |   |                 |  |  |  |

|                   | Vdd                                                   | _              | 3.0                          | 3.3 | 3.6 | V | -40°C to +150°C |  |  |  |

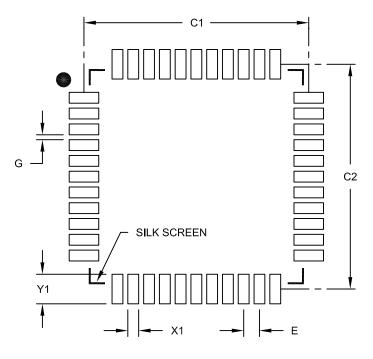

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## **RECOMMENDED LAND PATTERN**

|                          | N        | <b>ILLIMETER</b> | S        |      |

|--------------------------|----------|------------------|----------|------|

| Dimensior                | n Limits | MIN              | NOM      | MAX  |

| Contact Pitch            | E        |                  | 0.80 BSC |      |

| Contact Pad Spacing      | C1       |                  | 11.40    |      |

| Contact Pad Spacing      | C2       |                  | 11.40    |      |

| Contact Pad Width (X44)  | X1       |                  |          | 0.55 |

| Contact Pad Length (X44) | Y1       |                  |          | 1.50 |

| Distance Between Pads    | G        | 0.25             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

## **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                                                                                |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                       |

| Section 30.0 "Electrical<br>Characteristics"                                                                                                                            | Updated the VBOR specifications and/or its related note in the following electrical<br>characteristics tables:<br>• Table 30-1<br>• Table 30-4<br>• Table 30-12<br>• Table 30-14<br>• Table 30-15<br>• Table 30-16<br>• Table 30-56<br>• Table 30-57<br>• Table 30-58<br>• Table 30-59<br>• Table 30-60 |

| TyCON (Timer3 and Timer5 Control)    | 211    |

|--------------------------------------|--------|

| UxMODE (UARTx Mode)                  |        |

| UxSTA (UARTx Status and Control)     |        |

| VEL1CNT (Velocity Counter 1)         |        |

| Resets                               | 123    |

| Brown-out Reset (BOR)                |        |

| Configuration Mismatch Reset (CM)    | 123    |

| Illegal Condition Reset (IOPUWR)     | 123    |

| Illegal Opcode                       | 123    |

| Security                             |        |

| Uninitialized W Register             | 123    |

| Master Clear (MCLR) Pin Reset        | 123    |

| Power-on Reset (POR)                 |        |

| RESET Instruction (SWR)              |        |

| Resources                            |        |

| Trap Conflict Reset (TRAPR)          | 123    |

| Watchdog Timer Time-out Reset (WDTO) | 123    |

| Resources Required for Digital PFC   | 32, 34 |

| Revision History                     | 507    |

## S

| Serial Peripheral Interface (SPI)<br>Software Stack Pointer (SSP) |     |

|-------------------------------------------------------------------|-----|

| Special Features of the CPU                                       |     |

| SPI                                                               |     |

| Control Registers                                                 | 268 |

| Helpful Tips                                                      | 267 |

| Resources                                                         | 267 |

## т

| Temperature and Voltage Specifications |

|----------------------------------------|

| AC                                     |

| Thermal Operating Conditions           |

| Thermal Packaging Characteristics      |

| Timer1                                 |

| Control Register                       |

| Resources                              |

| Timer2/3 and Timer4/5                  |

| Control Registers                      |

| Resources                              |

| Timing Diagrams                        |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000, |

| SSRCG = 0)                             |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, |

| SSRCG = 0, SAMC<4:0> = 00010)          |

| 12-Bit ADC Conversion (ASAM = 0,       |

| SSRC<2:0> = 000, SSRCG = 0)            |

| BOR and Master Clear Reset             |

| ECANx I/O                              |

| External Clock414                      |

| High-Speed PWMx Fault422               |

| High-Speed PWMx Module                 |

| I/O Characteristics                    |

| I2Cx Bus Data (Master Mode)450         |

| I2Cx Bus Data (Slave Mode)             |

| I2Cx Bus Start/Stop Bits (Master Mode) |

| I2Cx Bus Start/Stop Bits (Slave Mode)  |

|                                        |

| Input Capture x (ICx)                         | . 420 |

|-----------------------------------------------|-------|

| OCx/PWMx                                      |       |

| Output Compare x (OCx)                        | . 421 |

| QEA/QEB Input                                 | . 424 |

| QEI Module Index Pulse                        | . 425 |

| SPI1 Master Mode (Full-Duplex, CKE = 0,       |       |

| CKP = x, SMP = 1)                             | . 441 |

| SPI1 Master Mode (Full-Duplex, CKE = 1,       |       |

| CKP = x, SMP = 1)                             | . 440 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 0)                                      | . 438 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 1)                                      | . 439 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 0, SMP = 0)                             | . 448 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |