Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K × 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

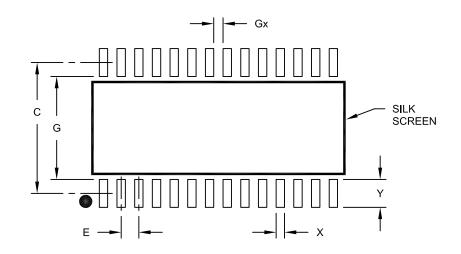

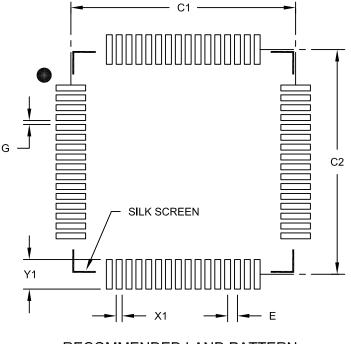

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name  | Addr          | Bit 15 | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9    | Bit 8      | Bit 7                         | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------------------|--------|--------|--------|----------|----------|------------|-------------------------------|----------|--------|--------|--------|-----------|--------|--------|---------------|

|            | 0400-<br>041E |        |                       |        |        |        |          |          | See defini | ion when W                    | 'IN = x  |        |        |        |           |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF                  | P<3:0> |        |        | F2BI     | ><3:0>   |            | F1BP<3:0>                     |          |        |        |        | F0BP<3:0> |        |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF                  | ><3:0> |        |        | F6BI     | ><3:0>   |            |                               | F5BP     | <3:0>  |        |        | F4BP      | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11BP<3:0> F10BP<3:0> |        |        |        |          | F9BP     | <3:0>      |                               |          | F8BP   | <3:0>  |        | 0000      |        |        |               |

| C1BUFPNT4  | 0426          |        | F15BP<3:0> F14BP<3:0> |        |        |        | F13B     | D<3:0>   |            |                               | F12BF    | P<3:0> |        | 0000   |           |        |        |               |

| C1RXM0SID  | 0430          |        | SID<10:3>             |        |        |        | SID<2:0> |          | _          | MIDE                          | _        | EID<   | 17:16> | xxxx   |           |        |        |               |

| C1RXM0EID  | 0432          |        | EID<15:8>             |        |        |        |          |          | EID<       | 7:0>                          |          |        |        | xxxx   |           |        |        |               |

| C1RXM1SID  | 0434          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | _      | MIDE   | —         | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |                       |        | EID<   | :15:8> |          |          |            |                               | EID<     |        |        | 7:0>   |           |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | MIDE   | —         | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |                       |        | EID<   | :15:8> |          |          |            |                               |          |        | EID<   | 7:0>   |           |        |        | xxxx          |

| C1RXF0SID  | 0440          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        | EID<15:8>             |        |        |        | EID<7:0> |          |            |                               |          |        | xxxx   |        |           |        |        |               |

| C1RXF1SID  | 0444          |        | SID<10:3>             |        |        |        |          | SID<2:0> |            | _                             | EXIDE    | —      | EID<   | 17:16> | xxxx      |        |        |               |

| C1RXF1EID  | 0446          |        | EID<15:8>             |        |        |        |          |          |            | EID<                          | 7:0>     |        |        |        | xxxx      |        |        |               |

| C1RXF2SID  | 0448          |        | SID<10:3>             |        |        |        |          | SID<2:0> |            | —                             | EXIDE    | —      | EID<   | 17:16> | xxxx      |        |        |               |

| C1RXF2EID  | 044A          |        |                       |        | EID<   | :15:8> |          |          |            | EID<7:0>                      |          |        |        |        |           | xxxx   |        |               |

| C1RXF3SID  | 044C          |        |                       |        | SID<   | :10:3> |          |          |            | SID<2:0> —                    |          |        |        | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |                       |        | EID<   | :15:8> |          |          |            | EID<7:0>                      |          |        |        |        |           | xxxx   |        |               |

| C1RXF4SID  | 0450          |        |                       |        | SID<   | :10:3> |          |          |            | SID<2:0> — EXIDE — EID<1      |          |        |        | 17:16> | xxxx      |        |        |               |

| C1RXF4EID  | 0452          |        |                       |        | EID<   | :15:8> |          |          |            | EID<7:0>                      |          |        |        |        |           | xxxx   |        |               |

| C1RXF5SID  | 0454          |        |                       |        | SID<   | :10:3> |          |          |            | SID<2:0> — EXIDE — EID<17:16> |          |        |        |        |           | 17:16> | xxxx   |               |

| C1RXF5EID  | 0456          |        |                       |        | EID<   | :15:8> |          |          |            |                               |          |        | EID<   | 7:0>   |           |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |                       |        | EID<   | :15:8> |          |          |            |                               |          |        | EID<   | 7:0>   |           |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |                       |        | EID<   | :15:8> |          |          |            |                               |          |        | EID<   | 7:0>   |           |        |        | xxxx          |

| C1RXF8SID  | 0460          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        |                       |        |        | :15:8> |          |          |            | EID                           |          |        | EID<   | )<7:0> |           |        |        | xxxx          |

| C1RXF9SID  | 0464          |        |                       |        |        | :10:3> |          |          |            | SID<2:0> — EXIDE — EID<17:16> |          |        |        |        | 17:16>    | xxxx   |        |               |

| C1RXF9EID  | 0466          |        |                       |        |        | :15:8> |          |          |            |                               |          |        | EID<   |        |           |        |        | xxxx          |

| C1RXF10SID | 0468          |        |                       |        |        | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | —         | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |                       |        |        | :15:8> |          |          |            |                               |          |        | EID<   | -      |           |        |        | xxxx          |

| C1RXF11SID | 046C          |        |                       |        | SID<   | :10:3> |          |          |            |                               | SID<2:0> |        | —      | EXIDE  | -         | EID<   | 17:16> | xxxx          |

# TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>                                                                                                    | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |  |  |  |

|------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|--|--|--|

| WR                           | WREN                                       | WRERR                                                                                                                   | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |  |  |  |

| bit 15                       | I                                          | 1                                                                                                                       | 1                             |                         |                         |                         | bit 8                  |  |  |  |

|                              |                                            |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

| U-0                          | U-0                                        | U-0                                                                                                                     | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |  |  |  |

| _                            | —                                          | —                                                                                                                       | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |  |  |  |

| bit 7                        |                                            |                                                                                                                         |                               |                         |                         |                         | bit (                  |  |  |  |

| lagandi                      |                                            | SO - Sottab                                                                                                             | la Only hit                   |                         |                         |                         |                        |  |  |  |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable                                                                                             | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |  |  |  |

| -n = Value                   |                                            | '1' = Bit is se                                                                                                         |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |  |  |  |

|                              |                                            | 1 - Dit 13 30                                                                                                           |                               |                         |                         |                         | lowin                  |  |  |  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)                                                                                                           |                               |                         |                         |                         |                        |  |  |  |

|                              |                                            |                                                                                                                         | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |  |  |  |

|                              | cleared b                                  | y hardware o                                                                                                            | nce the operati               | on is complete          |                         |                         |                        |  |  |  |

|                              | -                                          |                                                                                                                         | ration is comple              | ete and inactive        | 9                       |                         |                        |  |  |  |

| bit 14                       | WREN: Write                                |                                                                                                                         | n/erase operati               | 000                     |                         |                         |                        |  |  |  |

|                              |                                            |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

| oit 13                       |                                            | <ul> <li>Inhibits Flash program/erase operations</li> <li>WRERR: Write Sequence Error Flag bit<sup>(1)</sup></li> </ul> |                               |                         |                         |                         |                        |  |  |  |

|                              | 1 = An impro                               | per program o                                                                                                           | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |  |  |  |

|                              |                                            | et attempt of th                                                                                                        | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |  |  |  |

| bit 12                       |                                            |                                                                                                                         | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |  |  |  |

|                              |                                            |                                                                                                                         | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |  |  |  |

|                              |                                            |                                                                                                                         | r is active durin             |                         |                         |                         |                        |  |  |  |

| bit 11-4                     | Unimplemen                                 | ted: Read as                                                                                                            | '0'                           |                         |                         |                         |                        |  |  |  |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation                                                                                                           | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |  |  |  |

|                              | 1111 <b>= Rese</b>                         |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

|                              | 1110 = Rese<br>1101 = Rese                 |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

|                              | 1100 <b>= Rese</b>                         |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

|                              | 1011 <b>= Rese</b>                         |                                                                                                                         |                               |                         |                         |                         |                        |  |  |  |

|                              | 1010 = Rese<br>0011 = Memo                 |                                                                                                                         | e operation                   |                         |                         |                         |                        |  |  |  |

|                              | 0010 = Rese                                | rved                                                                                                                    | -                             |                         |                         |                         |                        |  |  |  |

|                              |                                            |                                                                                                                         | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |  |  |  |

|                              | 0000 <b>= Rese</b>                         | rvea                                                                                                                    |                               |                         |                         |                         |                        |  |  |  |

|                              | These bits can onl                         | -                                                                                                                       |                               |                         |                         |                         |                        |  |  |  |

|                              | If this bit is set, the (TVREG) before Fla |                                                                                                                         |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |  |  |  |

|                              | All other combinati                        |                                                                                                                         | •                             |                         |                         |                         |                        |  |  |  |

| <b>.</b> .                   |                                            |                                                                                                                         |                               | in ploinenteu.          |                         |                         |                        |  |  |  |

| 4:                           | Execution of the P                         | wrsav instruc                                                                                                           | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |  |  |  |

# REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| U-0                                                    | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0          | R-0              | R-0     | R-0     |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------|------------------|---------|---------|--|--|--|--|

|                                                        | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3         | ILR2             | ILR1    | ILR0    |  |  |  |  |

| bit 15                                                 |                                                                                              |                                                                                                                                                                         |                                                                                 |              |                  |         | bit 8   |  |  |  |  |

| R-0                                                    | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0          | R-0              | R-0     | R-0     |  |  |  |  |

| VECNUM7                                                | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3      | VECNUM2          | VECNUM1 | VECNUM0 |  |  |  |  |

| bit 7                                                  |                                                                                              |                                                                                                                                                                         |                                                                                 |              |                  |         | bit C   |  |  |  |  |

| Legend:                                                |                                                                                              |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

| R = Readable                                           | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen | nented bit, read | as '0'  |         |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleare |                                                                                              |                                                                                                                                                                         |                                                                                 | ared         | x = Bit is unkr  | nown    |         |  |  |  |  |

| bit 15-12                                              | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |              |                  |         |         |  |  |  |  |

| bit 11-8                                               | ILR<3:0>: New CPU Interrupt Priority Level bits                                              |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | 1111 = CPU Interrupt Priority Level is 15                                                    |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        |                                                                                              |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | •                                                                                            |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        |                                                                                              | Interrupt Priori<br>Interrupt Priori                                                                                                                                    |                                                                                 |              |                  |         |         |  |  |  |  |

| bit 7-0                                                | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                         |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | 11111111 = 255, Reserved; do not use                                                         |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | •                                                                                            |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | •                                                                                            |                                                                                                                                                                         |                                                                                 |              |                  |         |         |  |  |  |  |

|                                                        | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )            |                  |         |         |  |  |  |  |

# REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

# 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

# 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

## 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         | _   | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         | _   | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

## TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                    |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea                  | ared          | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b     | its   |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|        |     |       |            | DD20  |       |       |       |  |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |  |

|        |     |       | RP35R<5:0> |       |       |       |       |  |  |  |

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

# REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

## REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0           | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------------|-------|-------|-----------------|----------|-------|-------|-------|

|                                                                       |       |       | TRGC            | MP<15:8> |       |       |       |

| bit 15                                                                |       |       |                 |          |       |       | bit 8 |

|                                                                       |       |       |                 |          |       |       |       |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0           | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                       |       |       | TRGC            | MP<7:0>  |       |       |       |

| bit 7                                                                 |       |       |                 |          |       |       | bit 0 |

| Legend:                                                               |       |       |                 |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'  |       |       |                 |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is ur |       |       | x = Bit is unkr | nown     |       |       |       |

# REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

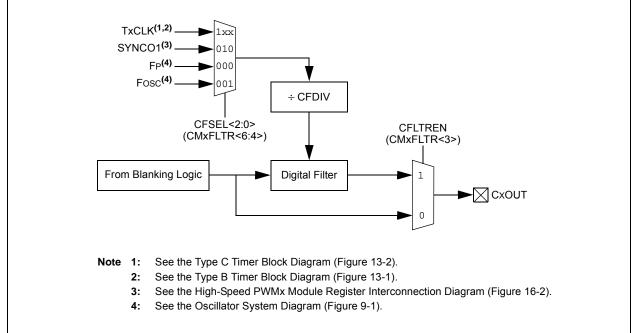

# DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

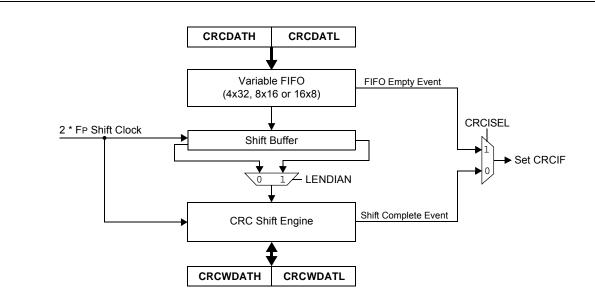

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

## FIGURE 26-1: CRC BLOCK DIAGRAM

# 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

# 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

# 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

# 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

## **30.1 DC Characteristics**

|                |                             |                       | Maximum MIPS                                                          |

|----------------|-----------------------------|-----------------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)     | Temp Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

|                | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                    |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

## TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | _           | +85  | °C   |

| Extended Temperature Devices                                                                |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | I    | Pint + Pi/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (    | TJ — TA)/θJ | IA   | W    |

## TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                   | Symbol | Тур. | Max. | Unit | Notes |

|--------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN           | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10 mm | θJA    | 48.3 | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN 6x6 mm   | θJA    | 41   | -    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN           | θJA    | 29.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10 mm | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin VTLA 6x6 mm   | θJA    | 25.2 | _    | °C/W | 1     |

| Package Thermal Resistance, 36-Pin VTLA 5x5 mm   | θJA    | 28.5 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S         | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP          | θJA    | 71.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC          | θJA    | 69.7 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP         | θJA    | 60.0 | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

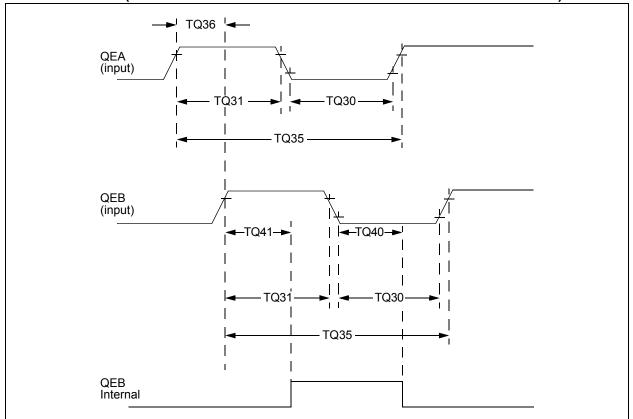

## FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

# TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |            |                                                         |

|--------------------|--------|----------------------------------------------------|-------------------------------------------------------|---|------------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Typ. <sup>(2)</sup> Max. Units                        |   | Conditions |                                                         |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy                                                 |   | ns         |                                                         |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy                                                 | — | ns         |                                                         |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY                                                | _ | ns         |                                                         |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY                                                 | — | ns         |                                                         |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy                                           | — | ns         | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy                                           | — | ns         | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b> |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

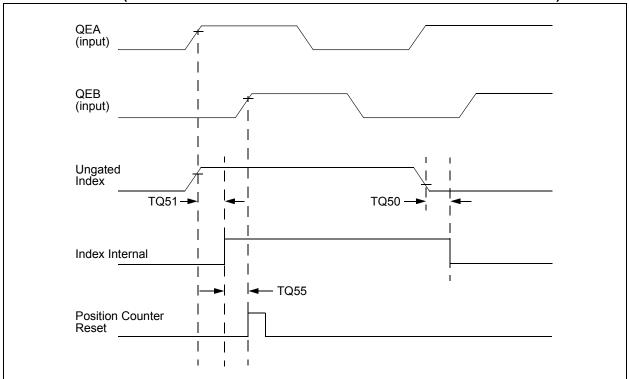

## FIGURE 30-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

# TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     | $ \begin{array}{ c c c c c } \hline Standard Operating Conditions: 3.0V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industria} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ for Extended} \\ \hline \end{array} $ |   |    |                                                         |

|--------------------|--------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                       | Min. Max. Units Conditions                                                                                                                                                                                                                                                                                   |   |    |                                                         |

| TQ50               | TqiL   | Filter Time to Recognize Low,<br>with Digital Filter                | 3 * N * Tcy                                                                                                                                                                                                                                                                                                  | _ | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ51               | TqiH   | Filter Time to Recognize High,<br>with Digital Filter               | 3 * N * Tcy                                                                                                                                                                                                                                                                                                  | _ | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |

| TQ55               | Tqidxr | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 TCY                                                                                                                                                                                                                                                                                                        | — | ns |                                                         |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

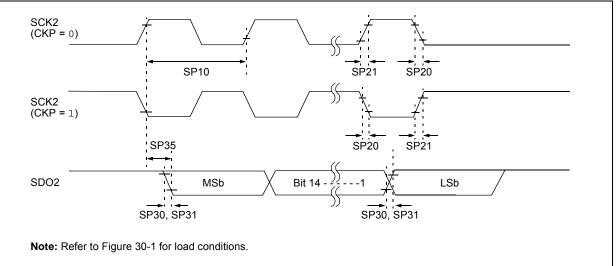

|                      |                                          |                                             | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indus<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for External |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                             | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-33                              | _                                           | _                                                                                                                                                                                                      | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                                                                                                                                                                      | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                                                                                                                                                                      | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-36                                                                                                                                                                                            | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-37                                                                                                                                                                                            | 1   | 1   | 0   |  |