Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504-h-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

# FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

# 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: CI                                          | PU STATUS I                            | REGISTER                    |                          |                    |                   |               |

|------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|

| R/W-0                  | R/W-0                                                | R/W-0                                  | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |

| bit 15                 |                                                      |                                        |                             |                          |                    |                   | bit 8         |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                 | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |

| IPL2                   | IPL1                                                 | IPL0                                   | RA                          | N                        | OV                 | Z                 | С             |

| bit 7                  | ·                                                    | •                                      |                             | •                        |                    |                   | bit (         |

| Legend:                |                                                      | C = Clearable                          | e bit                       |                          |                    |                   |               |

| R = Readab             | le bit                                               | W = Writable                           | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |

| -n = Value a           | t POR                                                | '1'= Bit is set                        |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |

|                        |                                                      |                                        |                             |                          |                    |                   |               |

| bit 15                 | OA: Accumul                                          | ator A Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator A has over                        | flowed                      |                          |                    |                   |               |

|                        | 0 = Accumula                                         | ator A has not o                       | verflowed                   |                          |                    |                   |               |

| bit 14                 | OB: Accumul                                          | ator B Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator B has over                        | flowed                      |                          |                    |                   |               |

|                        |                                                      | ator B has not c                       |                             |                          |                    |                   |               |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        |                                                      | ator A is saturat<br>ator A is not sat |                             | en saturated at          | some time          |                   |               |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat | ted or has bee              |                          | some time          |                   |               |

| bit 11                 |                                                      | B Combined A                           |                             | vorflow Status           | ы#(1)              |                   |               |

|                        |                                                      | ators A or B have                      |                             | vernow Status            | DIL                |                   |               |

|                        |                                                      | ccumulators A                          |                             | erflowed                 |                    |                   |               |

| bit 10                 |                                                      | B Combined Ad                          |                             |                          | (1)                |                   |               |

|                        |                                                      |                                        |                             |                          | urated at some     | time              |               |

|                        | 0 = Neither A                                        | ccumulators A                          | or B are satur              | ated                     |                    |                   |               |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>              |                             |                          |                    |                   |               |

|                        | 1 = DO <b>loop is</b>                                | s in progress                          |                             |                          |                    |                   |               |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                       | S                           |                          |                    |                   |               |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                        | orrow bit                   |                          |                    |                   |               |

|                        |                                                      | out from the 4th sult occurred         | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |

|                        | 0 = No carry                                         |                                        |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |

|                        | his bit is available                                 |                                        |                             |                          |                    |                   | -             |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                        |                             |                          |                    |                   |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

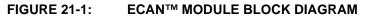

| IABLE 4-2  | ABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dSPIC33EPXXXMC/GP50X DEVICES ONLY |         |           |         |         |          |            |           |        |              |           |             |         |           |          |          |        |               |

|------------|----------------------------------------------------------------------------------------------------|---------|-----------|---------|---------|----------|------------|-----------|--------|--------------|-----------|-------------|---------|-----------|----------|----------|--------|---------------|

| File Name  | Addr.                                                                                              | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11   | Bit 10     | Bit 9     | Bit 8  | Bit 7        | Bit 6     | Bit 5       | Bit 4   | Bit 3     | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400                                                                                               | _       | —         | CSIDL   | ABAT    | CANCKS   | R          | EQOP<2:0  | >      | OPM          | /IODE<2:0 | >           | —       | CANCAP    | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402                                                                                               | _       | _         | —       | _       | _        | _          | —         | _      | —            | _         | _           |         | D         | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404                                                                                               | _       | —         | —       |         | F        | ILHIT<4:0> |           |        | —            |           |             | •       | ICODE<6:0 | >        |          |        | 0040          |

| C1FCTRL    | 0406                                                                                               | C       | DMABS<2:0 | >       |         | _        | —          | —         | _      | _            | _         | _           |         |           | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408                                                                                               |         | —         |         |         | FBP<5:0> |            |           |        | _            | _         | — FNRB<5:0> |         |           | 0000     |          |        |               |

| C1INTF     | 040A                                                                                               |         | —         | TXBO    | TXBP    | RXBP     | TXWAR      | RXWAR     | EWARN  | IVRIF        | WAKIF     | ERRIF       | _       | FIFOIF    | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C                                                                                               |         | —         | —       |         | _        | —          | —         | —      | IVRIE        | WAKIE     | ERRIE       | _       | FIFOIE    | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E                                                                                               |         |           |         | TERRCN  | T<7:0>   |            |           |        | RERRCNT<7:0> |           |             |         |           |          |          | 0000   |               |

| C1CFG1     | 0410                                                                                               | _       | _         | _       | _       | _        | _          | _         | _      | SJW<1        | :0>       |             |         | BRP       | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412                                                                                               | _       | WAKFIL    | _       | _       | _        | SI         | =G2PH<2:( | )>     | SEG2PHTS     | SAM       | S           | EG1PH<2 | :0>       | P        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414                                                                                               | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11  | FLTEN10    | FLTEN9    | FLTEN8 | FLTEN7       | FLTEN6    | FLTEN5      | FLTEN4  | FLTEN3    | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418                                                                                               | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS     | K<1:0>     | F4MS      | K<1:0> | F3MSK<       | <1:0>     | F2MS        | K<1:0>  | F1MSH     | <<1:0>   | F0MS     | <<1:0> | 0000          |

| C1FMSKSEL2 | 041A                                                                                               | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS    | K<1:0>     | F12MS     | K<1:0> | F11MSK       | <1:0>     | F10MS       | K<1:0>  | F9MSk     | <<1:0>   | F8MSI    | <<1:0> | 0000          |

### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14                      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8      | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-----------------------------|---------|---------|---------|---------|---------|------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         | See definition when WIN = x |         |         |         |         |         |            |              |         |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14                     | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30                     | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14                     | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8     | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30                     | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1                      | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>    | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3                      | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>    | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5                      | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>    | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7                      | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>    | TXEN6        | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |         |                             |         |         |         |         | E       | CAN1 Rece  | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |                             |         |         |         |         | E       | CAN1 Trans | smit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

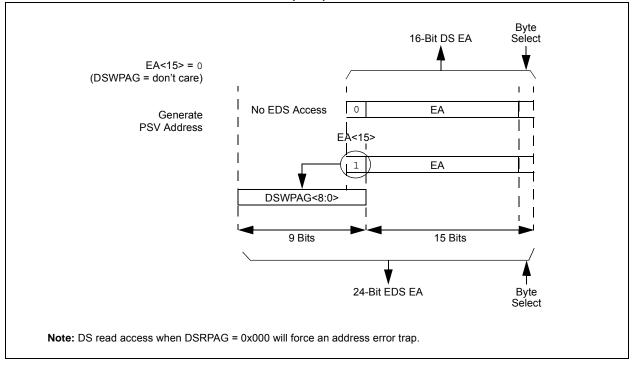

# EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

| R/W-1        | R/W-0         | R/W-0                                                            | U-0           | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|--------------|---------------|------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|--|--|

| GIE          | DISI          | SWTRAP                                                           |               |                  |                  | _               |        |  |  |  |  |

| bit 15       |               |                                                                  |               |                  |                  |                 | bit 8  |  |  |  |  |

|              |               |                                                                  |               |                  |                  |                 |        |  |  |  |  |

| U-0          | U-0           | U-0                                                              | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|              | —             |                                                                  |               |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7        |               |                                                                  |               |                  |                  |                 | bit C  |  |  |  |  |

| Legend:      |               |                                                                  |               |                  |                  |                 |        |  |  |  |  |

| R = Readab   | le bit        | W = Writable                                                     | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value a |               | '1' = Bit is set                                                 |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |

|              |               |                                                                  |               |                  |                  |                 |        |  |  |  |  |

| bit 15       | GIE: Global   | Interrupt Enable                                                 | e bit         |                  |                  |                 |        |  |  |  |  |

|              | 1 = Interrupt | s and associate                                                  | d IE bits are | enabled          |                  |                 |        |  |  |  |  |

|              |               | s are disabled, I                                                | •             | still enabled    |                  |                 |        |  |  |  |  |

| bit 14       | DISI: DISI    | nstruction Statu                                                 | s bit         |                  |                  |                 |        |  |  |  |  |

|              |               | struction is active<br>struction is not a                        | -             |                  |                  |                 |        |  |  |  |  |

| bit 13       | SWTRAP: S     | Software Trap St                                                 | atus bit      |                  |                  |                 |        |  |  |  |  |

|              |               | e trap is enabled<br>e trap is disabled                          |               |                  |                  |                 |        |  |  |  |  |

| bit 12-3     | Unimpleme     | nted: Read as '                                                  | 0'            |                  |                  |                 |        |  |  |  |  |

| bit 2        | INT2EP: Ext   | ternal Interrupt 2                                               | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |               | on negative edg                                                  |               |                  |                  |                 |        |  |  |  |  |

| bit 1        | INT1EP: Ext   | ternal Interrupt 1                                               | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |               | 1 = Interrupt on positive edge<br>0 = Interrupt on positive edge |               |                  |                  |                 |        |  |  |  |  |

| bit 0        | INTOEP: Ext   | ternal Interrupt C                                               | Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |               | on negative edg                                                  |               |                  |                  |                 |        |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

# REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0   | U-0          | U-0   | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-----------------|-----------|-------|--|--|

| —                                  | -     | —            | —     |                                         | LEB             | <11:8>    |       |  |  |

| bit 15                             |       |              |       |                                         |                 |           | bit 8 |  |  |

|                                    |       |              |       |                                         |                 |           |       |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

|                                    |       |              | LEE   | 3<7:0>                                  |                 |           |       |  |  |

| bit 7                              |       |              |       |                                         |                 |           | bit 0 |  |  |

|                                    |       |              |       |                                         |                 |           |       |  |  |

| Legend:                            |       |              |       |                                         |                 |           |       |  |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimplen                            | nented bit, rea | id as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |  |

# REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

# 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This insures          |  | that  | the            | first | fr | ame |

|-------|-----------------------|--|-------|----------------|-------|----|-----|

|       | transmission a        |  | after | initialization |       | is | not |

|       | shifted or corrupted. |  |       |                |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

# 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0                                                                                          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0    |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|--------|--|--|--|

| —             | —                                                                                            | —                | _              | —                | —                | —               | —      |  |  |  |

| bit 15        |                                                                                              |                  |                |                  |                  |                 | bit 8  |  |  |  |

|               |                                                                                              |                  |                |                  |                  |                 |        |  |  |  |

| U-0           | U-0 U-0 R-0                                                                                  |                  | R-0            | R-0              | R-0              | R-0             | R-0    |  |  |  |

| —             | — — DNCNT4                                                                                   |                  |                | DNCNT3           | DNCNT2           | DNCNT1          | DNCNT0 |  |  |  |

| bit 7         |                                                                                              |                  |                |                  |                  |                 | bit 0  |  |  |  |

|               |                                                                                              |                  |                |                  |                  |                 |        |  |  |  |

| Legend:       |                                                                                              |                  |                |                  |                  |                 |        |  |  |  |

| R = Readable  | e bit                                                                                        | W = Writable     | bit            | U = Unimpler     | mented bit, read | as '0'          |        |  |  |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |

|               |                                                                                              |                  |                |                  |                  |                 |        |  |  |  |

| bit 15-5      | Unimplemen                                                                                   | ted: Read as '   | 0'             |                  |                  |                 |        |  |  |  |

| bit 4-0       | DNCNT<4:0>                                                                                   | : DeviceNet™     | Filter Bit Num | iber bits        |                  |                 |        |  |  |  |

|               | 10010-11111 = Invalid selection<br>10001 = Compares up to Data Byte 3, bit 6 with EID<17>    |                  |                |                  |                  |                 |        |  |  |  |

|               | •                                                                                            |                  |                |                  |                  |                 |        |  |  |  |

|               | •                                                                                            |                  |                |                  |                  |                 |        |  |  |  |

|               | •                                                                                            |                  |                |                  |                  |                 |        |  |  |  |

|               | 00001 = Compares up to Data Byte 1, bit 7 with EID<0><br>00000 = Does not compare data bytes |                  |                |                  |                  |                 |        |  |  |  |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                   | U-0             | U-0                                                                                            | U-0    | U-0              | U-0              | U-0             | U-0   |  |  |  |  |  |

|-----------------------|-----------------|------------------------------------------------------------------------------------------------|--------|------------------|------------------|-----------------|-------|--|--|--|--|--|

| _                     | —               | —                                                                                              |        | —                | —                | —               | _     |  |  |  |  |  |

| bit 15                |                 |                                                                                                |        |                  |                  |                 | bit   |  |  |  |  |  |

|                       |                 |                                                                                                |        |                  |                  |                 |       |  |  |  |  |  |

| R/W-0                 | R/W-0           | R/W-0                                                                                          | U-0    | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| IVRIE                 | WAKIE           | ERRIE                                                                                          | —      | FIFOIE           | RBOVIE           | RBIE            | TBIE  |  |  |  |  |  |

| bit 7                 |                 |                                                                                                |        |                  |                  |                 | bit   |  |  |  |  |  |

| Lonondi               |                 |                                                                                                |        |                  |                  |                 |       |  |  |  |  |  |

| Legend:<br>R = Readab | la hit          | W = Writable t                                                                                 | .it    | II – Unimplor    | nented bit, read |                 |       |  |  |  |  |  |

| -n = Value a          |                 | '1' = Bit is set                                                                               | אנ     | '0' = Bit is cle |                  | x = Bit is unkr |       |  |  |  |  |  |

|                       | IL FOR          | I – DILIS SEL                                                                                  |        |                  | areu             |                 |       |  |  |  |  |  |

| bit 15-8              | Unimplemen      | ted: Read as '(                                                                                | )'     |                  |                  |                 |       |  |  |  |  |  |

| bit 7                 | -               | Unimplemented: Read as '0'<br>IVRIE: Invalid Message Interrupt Enable bit                      |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 1 = Interrupt request is enabled                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 0 = Interrupt request is not enabled                                                           |        |                  |                  |                 |       |  |  |  |  |  |

| bit 6                 | WAKIE: Bus      | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 1 = Interrupt request is enabled                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 0 = Interrupt request is not enabled                                                           |        |                  |                  |                 |       |  |  |  |  |  |

| bit 5                 |                 | ERRIE: Error Interrupt Enable bit                                                              |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |        |                  |                  |                 |       |  |  |  |  |  |

| L:1 4                 |                 | •                                                                                              |        |                  |                  |                 |       |  |  |  |  |  |

| bit 4                 | -               | ted: Read as '0                                                                                |        | - 64             |                  |                 |       |  |  |  |  |  |

| bit 3                 |                 | FIFOIE: FIFO Almost Full Interrupt Enable bit                                                  |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |        |                  |                  |                 |       |  |  |  |  |  |

| bit 2                 |                 | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit                                         |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 1 = Interrupt request is enabled                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 0 = Interrupt request is not enabled                                                           |        |                  |                  |                 |       |  |  |  |  |  |

| bit 1                 | RBIE: RX Bu     | RBIE: RX Buffer Interrupt Enable bit                                                           |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | 1 = Interrupt request is enabled                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       | •               | request is not e                                                                               |        |                  |                  |                 |       |  |  |  |  |  |

| bit 0                 |                 | fer Interrupt En                                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                 | request is enabl                                                                               |        |                  |                  |                 |       |  |  |  |  |  |

|                       | 0 = Interrupt i | request is not e                                                                               | napled |                  |                  |                 |       |  |  |  |  |  |

# REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

# 22.2 CTMU Control Registers

| REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1                                                                                                             |                                  |                  |       |                                         |                  |                        |        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------|-----------------------------------------|------------------|------------------------|--------|--|

| R/W-0                                                                                                                                                        | U-0                              | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0                  | R/W-0  |  |

| CTMUEN                                                                                                                                                       | _                                | CTMUSIDL         | TGEN  | EDGEN                                   | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15                                                                                                                                                       |                                  |                  |       |                                         |                  |                        | bit 8  |  |

|                                                                                                                                                              |                                  |                  |       |                                         |                  |                        |        |  |

| U-0                                                                                                                                                          | U-0                              | U-0              | U-0   | U-0                                     | U-0              | U-0                    | U-0    |  |

| _                                                                                                                                                            |                                  | —                | _     |                                         | <u> </u>         |                        | _      |  |

| bit 7                                                                                                                                                        |                                  |                  |       |                                         |                  |                        | bit 0  |  |

|                                                                                                                                                              |                                  |                  |       |                                         |                  |                        |        |  |

| Legend:                                                                                                                                                      |                                  |                  |       |                                         |                  |                        |        |  |

| R = Readable                                                                                                                                                 | e bit                            | W = Writable b   | oit   | U = Unimplen                            | nented bit, read | l as '0'               |        |  |

| -n = Value at                                                                                                                                                | POR                              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |                        |        |  |

| bit 15 <b>CTMUEN:</b> CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                     |                                  |                  |       |                                         |                  |                        |        |  |

| bit 14                                                                                                                                                       | Unimpleme                        | nted: Read as '0 | 3     |                                         |                  |                        |        |  |

| bit 13 CTMUSIDL: CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                                  |                  |       |                                         |                  |                        |        |  |

| bit 12                                                                                                                                                       | TGEN: Time Generation Enable bit |                  |       |                                         |                  |                        |        |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

# TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS                                                                                                  |      |               | Standard Operating Conditions (see Note 2): 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |   |            |    |          |

|---------------------------------------------------------------------------------------------------------------------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|----|----------|

| Param.         Symbol         Characteristic         Min.         Typ.         Max.         Units         Condition |      |               |                                                                                                                                                                                                                   |   | Conditions |    |          |

| VR310                                                                                                               | TSET | Settling Time | —                                                                                                                                                                                                                 | 1 | 10         | μS | (Note 1) |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |            |     |               |  |

|--------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-----|---------------|--|

| Param<br>No.       | Symbol | Characteristics                            | Min. Typ. Max. Units                                                                                                                                                                                                                                                                               |      |            |     | Conditions    |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                                                                                                                                                                                                                                                                          | _    | CVRSRC/32  | LSb |               |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | —                                                                                                                                                                                                                                                                                                  | ±25  | _          | mV  | CVRSRC = 3.3V |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                                                                                                                                                                                                                                                                                  | _    | AVDD + 0.3 | V   |               |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                                  | 1.5k | _          | Ω   |               |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

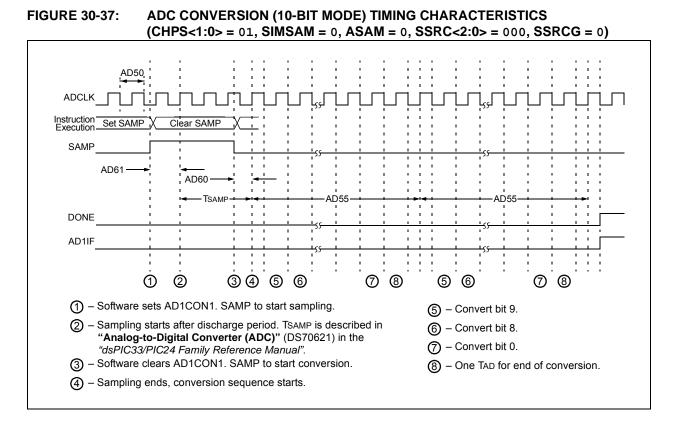

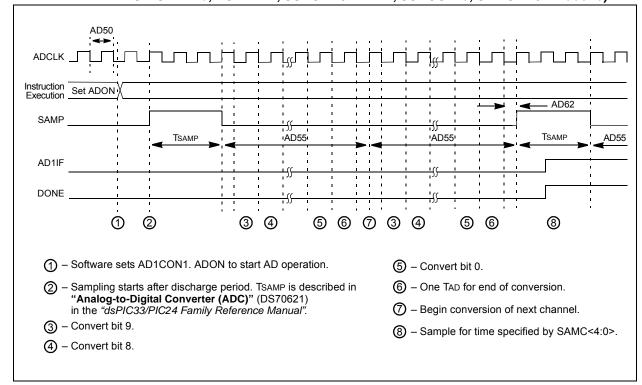

### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

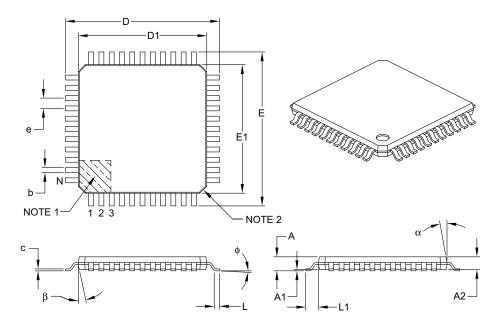

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |             |           |      |  |  |

|--------------------------|-------------|-------------|-----------|------|--|--|

| Dimens                   | sion Limits | MIN         | NOM       | MAX  |  |  |

| Number of Leads          | Ν           |             | 44        |      |  |  |

| Lead Pitch               | е           | 0.80 BSC    |           |      |  |  |

| Overall Height           | А           | -           | -         | 1.20 |  |  |

| Molded Package Thickness | A2          | 0.95        | 1.00      | 1.05 |  |  |

| Standoff                 | A1          | 0.05        | -         | 0.15 |  |  |

| Foot Length              | L           | 0.45        | 0.60      | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF    |           |      |  |  |

| Foot Angle               | φ           | 0°          | 3.5°      | 7°   |  |  |

| Overall Width            | E           | 12.00 BSC   |           |      |  |  |

| Overall Length           | D           | D 12.00 BSC |           |      |  |  |

| Molded Package Width     | E1          |             | 10.00 BSC |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC   |           |      |  |  |

| Lead Thickness           | с           | 0.09        | -         | 0.20 |  |  |

| Lead Width               | b           | 0.30        | 0.37      | 0.45 |  |  |

| Mold Draft Angle Top     | α           | 11°         | 12°       | 13°  |  |  |

| Mold Draft Angle Bottom  | β           | 11°         | 12°       | 13°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

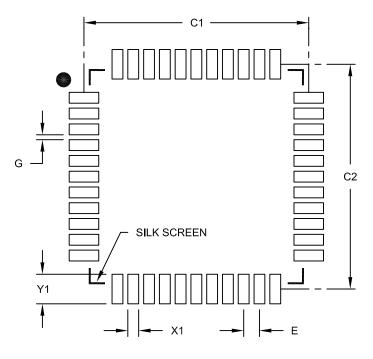

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# **RECOMMENDED LAND PATTERN**

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimensior                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | E           |      | 0.80 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.25 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |           |           |      |  |  |

|----------------------------|------------------|-----------|-----------|------|--|--|

| D                          | Dimension Limits |           |           | MAX  |  |  |

| Number of Leads            | N                | 64        |           |      |  |  |

| Lead Pitch                 | е                |           | 0.50 BSC  |      |  |  |

| Overall Height             | А                | -         | -         | 1.20 |  |  |

| Molded Package Thickness   | A2               | 0.95      | 1.00      | 1.05 |  |  |

| Standoff                   | A1               | 0.05      | -         | 0.15 |  |  |

| Foot Length                | L                | 0.45      | 0.60      | 0.75 |  |  |

| Footprint                  | L1               | 1.00 REF  |           |      |  |  |

| Foot Angle                 | φ                | 0°        | 3.5°      | 7°   |  |  |

| Overall Width              | E                |           | 12.00 BSC |      |  |  |

| Overall Length             | D                |           | 12.00 BSC |      |  |  |

| Molded Package Width       | E1               |           | 10.00 BSC |      |  |  |

| Molded Package Length      | D1               | 10.00 BSC |           |      |  |  |

| Lead Thickness             | С                | 0.09      | -         | 0.20 |  |  |

| Lead Width                 | b                | 0.17      | 0.22      | 0.27 |  |  |

| Mold Draft Angle Top α 11° |                  |           | 12°       | 13°  |  |  |

| Mold Draft Angle Bottom    | β                | 11°       | 12°       | 13°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B