Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

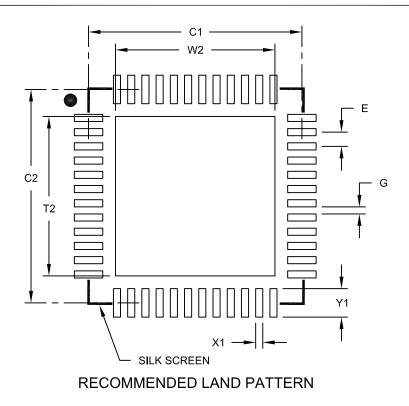

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504-h-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

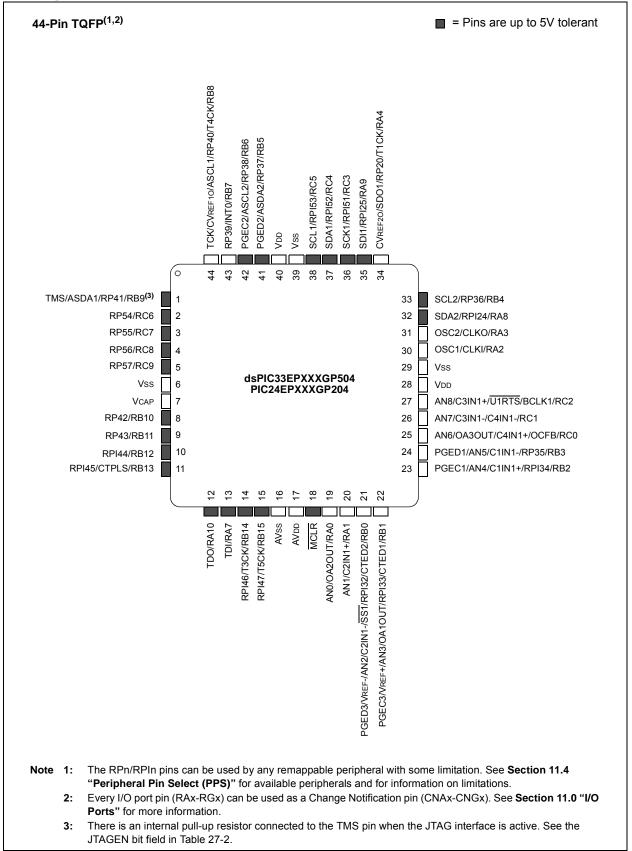

## **Pin Diagrams (Continued)**

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

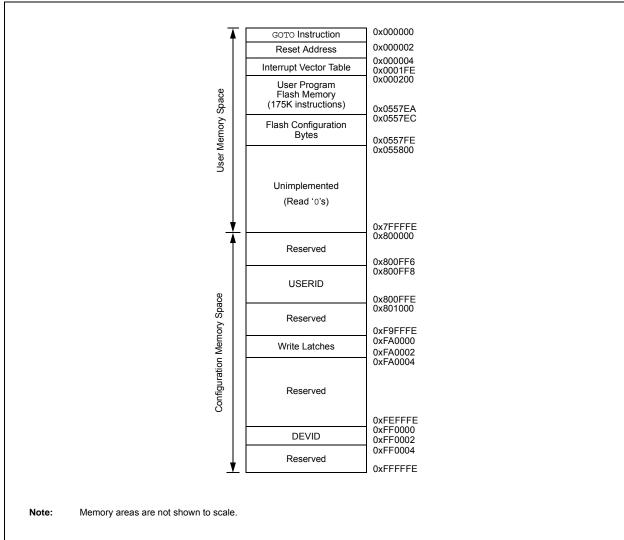

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | _        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       |               |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |                |         |                                                       |                                                          | I OIL U |        |           |          |        | 1102- |        |       |          |       |       |               |

|-----------|-------|---------|----------------|---------|-------------------------------------------------------|----------------------------------------------------------|---------|--------|-----------|----------|--------|-------|--------|-------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15  | Bit 14         | Bit 13  | Bit 12                                                | Bit 11                                                   | Bit 10  | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT         | TRGSTAT | FLTIEN                                                | CLIEN                                                    | TRGIEN  | ITB    | MDCS      | DTC<     | :1:0>  | DTCP  | _      | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL           | POLH    | POLL                                                  | PMOD                                                     | <1:0>   | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA | T<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | _       |                | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |                                                          |         |        |           |          |        |       | 0000   |       |          |       |       |               |

| PDC1      | 0C26  |         |                |         | PDC1<15:0>                                            |                                                          |         |        |           |          |        |       | FFF8   |       |          |       |       |               |

| PHASE1    | 0C28  |         | PHASE1<15:0> 0 |         |                                                       |                                                          |         |        |           |          |        |       | 0000   |       |          |       |       |               |

| DTR1      | 0C2A  | _       | _              |         |                                                       |                                                          |         |        |           | DTR1<13: | 0>     |       |        |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | _       | _              |         |                                                       |                                                          |         |        | А         | LTDTR1<1 | 3:0>   |       |        |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |                |         |                                                       |                                                          |         |        | TRGCMP<18 | 5:0>     |        |       |        |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI          | V<3:0>  |                                                       | _                                                        | _       | _      | _         | _        | _      |       |        | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF            | PLR     | PLF                                                   | PLF FLTLEBEN CLLEBEN — — — — BCH BCL BPHH BPHL BPLH BPLL |         |        |           |          |        |       | 0000   |       |          |       |       |               |

| LEBDLY1   | 0C3C  | _       | _              | —       | —                                                     |                                                          |         |        |           |          | LEB<11 | :0>   |        |       |          |       |       | 0000          |

| AUXCON1   | 0C3E  | —       | —              | _       |                                                       | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN 000       |         |        |           |          |        |       |        | 0000  |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | —     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | -      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | —      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | -      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

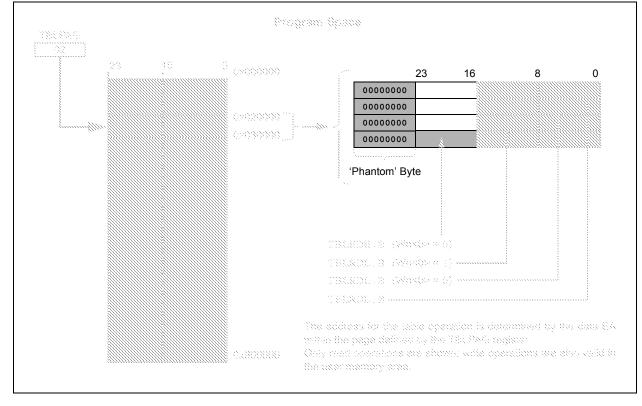

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| U-0          | U-0                                                                                                                         | U-0                     | U-0            | U-0             | U-0              | U-0      | U-0   |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|-----------------|------------------|----------|-------|--|--|--|--|--|--|

| -            | —                                                                                                                           | —                       | —              | —               | —                | —        | —     |  |  |  |  |  |  |

| bit 15       |                                                                                                                             |                         |                |                 |                  |          | bit 8 |  |  |  |  |  |  |

| U-0          | U-0                                                                                                                         | U-0                     | U-0            | R-1             | R-1              | R-1      | R-1   |  |  |  |  |  |  |

| _            | _                                                                                                                           | _                       | _              |                 | LSTC             | H<3:0>   |       |  |  |  |  |  |  |

| bit 7        |                                                                                                                             |                         |                |                 |                  |          | bit 0 |  |  |  |  |  |  |

| Legend:      |                                                                                                                             |                         |                |                 |                  |          |       |  |  |  |  |  |  |

| R = Readat   | ole bit                                                                                                                     | W = Writable            | bit            | U = Unimpler    | mented bit, read | 1 as '0' |       |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                      | '1' = Bit is set        |                | x = Bit is unkr | nown             |          |       |  |  |  |  |  |  |

|              |                                                                                                                             |                         |                |                 |                  |          |       |  |  |  |  |  |  |

| bit 15-4     | Unimplemen                                                                                                                  | ted: Read as '          | 0'             |                 |                  |          |       |  |  |  |  |  |  |

| bit 3-0      | LSTCH<3:0>                                                                                                                  | : Last DMAC C           | hannel Active  | e Status bits   |                  |          |       |  |  |  |  |  |  |

|              | 1111 = No DI<br>1110 = Rese                                                                                                 | MA transfer has<br>rved | s occurred sir | nce system Res  | set              |          |       |  |  |  |  |  |  |

|              | •                                                                                                                           |                         |                |                 |                  |          |       |  |  |  |  |  |  |

|              | •                                                                                                                           |                         |                |                 |                  |          |       |  |  |  |  |  |  |

|              | •                                                                                                                           |                         |                |                 |                  |          |       |  |  |  |  |  |  |

|              | 0100 = Reserved<br>0011 = Last data transfer was handled by Channel 3<br>0010 = Last data transfer was handled by Channel 2 |                         |                |                 |                  |          |       |  |  |  |  |  |  |

|              |                                                                                                                             | data transfer wa        |                |                 |                  |          |       |  |  |  |  |  |  |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| R/W-0         | R/W-0                                                                                                                          | R/W-0                                    | U-0        | U-0               | U-0             | U-0               | U-0    |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------|-------------------|-----------------|-------------------|--------|--|--|--|--|--|--|

| FRMEN         | SPIFSD                                                                                                                         | FRMPOL                                   | —          | —                 | _               | —                 | —      |  |  |  |  |  |  |

| bit 15        |                                                                                                                                |                                          |            |                   |                 |                   | bit 8  |  |  |  |  |  |  |

|               |                                                                                                                                |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

| U-0           | U-0                                                                                                                            | U-0                                      | U-0        | U-0               | U-0             | R/W-0             | R/W-0  |  |  |  |  |  |  |

| —             | —                                                                                                                              | —                                        | —          | —                 | _               | FRMDLY            | SPIBEN |  |  |  |  |  |  |

| bit 7         |                                                                                                                                |                                          |            |                   |                 |                   | bit 0  |  |  |  |  |  |  |

|               |                                                                                                                                |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

| Legend:       |                                                                                                                                |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                          | W = Writable b                           | pit        | U = Unimpler      | nented bit, rea | ad as '0'         |        |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                            | '1' = Bit is set                         |            | '0' = Bit is cle  | ared            | x = Bit is unkr   | nown   |  |  |  |  |  |  |

|               |                                                                                                                                |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

| bit 15        | <b>FRMEN:</b> Framed SPIx Support bit<br>1 = Framed SPIx support is enabled (SSx pin is used as Frame Sync pulse input/output) |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

|               |                                                                                                                                | SPIx support is e<br>SPIx support is d   |            | sx pin is used as | Frame Sync      | pulse input/outpu | ıt)    |  |  |  |  |  |  |

| bit 14        |                                                                                                                                | me Sync Pulse I                          |            | ontrol bit        |                 |                   |        |  |  |  |  |  |  |

|               | 1 = Frame S                                                                                                                    | ync pulse input (                        | slave)     |                   |                 |                   |        |  |  |  |  |  |  |

|               |                                                                                                                                | ync pulse output                         | . ,        |                   |                 |                   |        |  |  |  |  |  |  |

| bit 13        |                                                                                                                                | ame Sync Pulse                           |            | t                 |                 |                   |        |  |  |  |  |  |  |

|               |                                                                                                                                | ync pulse is activ<br>ync pulse is activ |            |                   |                 |                   |        |  |  |  |  |  |  |

| bit 12-2      | •                                                                                                                              | nted: Read as '0                         |            |                   |                 |                   |        |  |  |  |  |  |  |

| bit 1         | -                                                                                                                              | ame Sync Pulse                           |            | et hit            |                 |                   |        |  |  |  |  |  |  |

|               |                                                                                                                                | -                                        | -          |                   |                 |                   |        |  |  |  |  |  |  |

|               | <ul> <li>1 = Frame Sync pulse coincides with first bit clock</li> <li>0 = Frame Sync pulse precedes first bit clock</li> </ul> |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

| bit 0         | SPIBEN: Enhanced Buffer Enable bit                                                                                             |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

|               | 1 = Enhanced buffer is enabled                                                                                                 |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

|               | 0 = Enhance                                                                                                                    | d buffer is disabl                       | ed (Standa | rd mode)          |                 |                   |        |  |  |  |  |  |  |

|               |                                                                                                                                |                                          |            |                   |                 |                   |        |  |  |  |  |  |  |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0                | U-0                                           | R/W-0                                                                                          | R/W-0                                                    | R/W-0                              | U-0                                               | R/W-0                   | R/W-0                     |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|---------------------------------------------------|-------------------------|---------------------------|

| UARTEN <sup>(1</sup> | ) _                                           | USIDL                                                                                          | IREN <sup>(2)</sup>                                      | RTSMD                              |                                                   | UEN1                    | UEN0                      |

| bit 15               |                                               |                                                                                                |                                                          |                                    |                                                   |                         | bit 8                     |

|                      |                                               |                                                                                                |                                                          |                                    |                                                   |                         |                           |

| R/W-0, HC            |                                               | R/W-0, HC                                                                                      | R/W-0                                                    | R/W-0                              | R/W-0                                             | R/W-0                   | R/W-0                     |

| WAKE                 | LPBACK                                        | ABAUD                                                                                          | URXINV                                                   | BRGH                               | PDSEL1                                            | PDSEL0                  | STSEL                     |

| bit 7                |                                               |                                                                                                |                                                          |                                    |                                                   |                         | bit                       |

| Legend:              |                                               | HC = Hardwar                                                                                   | e Clearable b                                            | it                                 |                                                   |                         |                           |

| R = Readat           | ole bit                                       | W = Writable b                                                                                 | it                                                       | U = Unimplem                       | nented bit, read                                  | as '0'                  |                           |

| -n = Value a         | at POR                                        | '1' = Bit is set                                                                               |                                                          | '0' = Bit is clea                  |                                                   | x = Bit is unkn         | iown                      |

| bit 15               | 1 = UARTx is                                  | ARTx Enable bit<br>s enabled; all UA<br>s disabled; all UA                                     | ARTx pins are                                            |                                    |                                                   |                         |                           |

| bit 14               | Unimplemen                                    | ted: Read as '0                                                                                | ,                                                        |                                    |                                                   |                         |                           |

| bit 13               | USIDL: UAR                                    | Tx Stop in Idle M                                                                              | lode bit                                                 |                                    |                                                   |                         |                           |

|                      |                                               | nues module opera                                                                              |                                                          |                                    | le mode                                           |                         |                           |

| bit 12               | 1 = IrDA enc                                  | Encoder and De<br>oder and decod<br>oder and decod                                             | er are enable                                            | d                                  |                                                   |                         |                           |

| bit 11               | $1 = \overline{\text{UxRTS}} p$               | de Selection for<br>bin is in Simplex<br>bin is in Flow Co                                     | mode                                                     | t                                  |                                                   |                         |                           |

| bit 10               | Unimplemen                                    | ted: Read as '0                                                                                | 3                                                        |                                    |                                                   |                         |                           |

| bit 9-8              | 11 = UxTX, L<br>10 = UxTX, L<br>01 = UxTX, L  | JARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | ind used <sup>(4)</sup><br>UxCT <u>S pin is</u> c | controlled by PC        | ORT latches <sup>(4</sup> |

| bit 7                | WAKE: Wake                                    | e-up on Start bit                                                                              | Detect During                                            | Sleep Mode E                       | nable bit                                         |                         |                           |

|                      | in hardwa                                     | continues to sam<br>are on the follow<br>-up is enabled                                        |                                                          |                                    | generated on t                                    | he falling edge         | ; bit is cleare           |

| bit 6                | LPBACK: UA                                    | ARTx Loopback                                                                                  | Mode Select I                                            | oit                                |                                                   |                         |                           |

|                      |                                               | Loopback mode<br>k mode is disabl                                                              |                                                          |                                    |                                                   |                         |                           |

| e                    | Refer to the " <b>UAI</b><br>enabling the UAR | RTx module for re                                                                              | ceive or trans                                           | mit operation.                     | -                                                 | <i>ce Manual"</i> for i | nformation or             |

| 2:                   | This feature is or                            | nly available for                                                                              | he 16x BRG                                               | mode (BRGH =                       | 0).                                               |                         |                           |

|                      | This feature is or                            | -                                                                                              | -                                                        | -                                  |                                                   |                         |                           |

| 4                    | This fosturo is or                            | ly available on (                                                                              | 34 nin daviaa                                            | •                                  |                                                   |                         |                           |

4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                                          | U-0                                                                                       | U-0              | U-0            | U-0                                | U-0    | U-0                | U-0    |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|----------------|------------------------------------|--------|--------------------|--------|--|--|--|

| _                                                                                            | —                                                                                         | —                | _              | —                                  | —      | —                  | —      |  |  |  |

| bit 15                                                                                       |                                                                                           |                  |                |                                    |        |                    | bit 8  |  |  |  |

|                                                                                              |                                                                                           |                  |                |                                    |        |                    |        |  |  |  |

| U-0                                                                                          | U-0                                                                                       | U-0              | R-0            | R-0                                | R-0    | R-0                | R-0    |  |  |  |

| —                                                                                            | —                                                                                         | —                | DNCNT4         | DNCNT3                             | DNCNT2 | DNCNT1             | DNCNT0 |  |  |  |

| bit 7                                                                                        |                                                                                           |                  |                |                                    |        |                    | bit 0  |  |  |  |

|                                                                                              |                                                                                           |                  |                |                                    |        |                    |        |  |  |  |

| Legend:                                                                                      |                                                                                           |                  |                |                                    |        |                    |        |  |  |  |

| R = Readabl                                                                                  | e bit                                                                                     | W = Writable bit |                | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

| -n = Value at                                                                                | POR                                                                                       | '1' = Bit is set |                | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |  |  |

|                                                                                              |                                                                                           |                  |                |                                    |        |                    |        |  |  |  |

| bit 15-5                                                                                     | Unimplemen                                                                                | ted: Read as '   | 0'             |                                    |        |                    |        |  |  |  |

| bit 4-0                                                                                      | DNCNT<4:0>                                                                                | : DeviceNet™     | Filter Bit Num | iber bits                          |        |                    |        |  |  |  |

|                                                                                              | 10010-11111 = Invalid selection<br>10001 = Compares up to Data Byte 3, bit 6 with EID<17> |                  |                |                                    |        |                    |        |  |  |  |

|                                                                                              | •                                                                                         |                  |                |                                    |        |                    |        |  |  |  |

|                                                                                              | •                                                                                         |                  |                |                                    |        |                    |        |  |  |  |

|                                                                                              | •                                                                                         |                  |                |                                    |        |                    |        |  |  |  |

| 00001 = Compares up to Data Byte 1, bit 7 with EID<0><br>00000 = Does not compare data bytes |                                                                                           |                  |                |                                    |        |                    |        |  |  |  |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0                                                                  | R/W-0                                                       | R/W-0             | R/W-0                | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------------------------------------------------------------------|-------------------------------------------------------------|-------------------|----------------------|------------------|-----------------|--------|

| F7MSK<1:0>    |                                                                        | F6MSK<1:0>                                                  |                   | F5MSK<1:0>           |                  | F4MSK<1:0>      |        |

| bit 15        |                                                                        | ·                                                           |                   |                      |                  |                 | bit    |

| R/W-0         | R/W-0                                                                  | R/W-0                                                       | R/W-0             | R/W-0                | R/W-0            | R/W-0           | R/W-0  |

| F3MS          | SK<1:0>                                                                | F2MS                                                        | <b>&lt;</b> <1:0> | F1MS                 | K<1:0>           | F0MS            | <<1:0> |

| bit 7         |                                                                        |                                                             |                   |                      |                  |                 | bit (  |

| Legend:       |                                                                        |                                                             |                   |                      |                  |                 |        |

| R = Readable  | e bit                                                                  | W = Writable                                                | bit               | U = Unimplen         | nented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                    | '1' = Bit is set                                            |                   | '0' = Bit is cleared |                  | x = Bit is unkr | Iown   |

|               | 01 = Accept                                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain   | mask                 |                  |                 |        |

| bit 13-12     | F6MSK<1:0                                                              | >: Mask Source                                              | for Filter 6 bit  | s (same values       | s as bits<15:14  | >)              |        |

| bit 11-10     | F5MSK<1:0                                                              | >: Mask Source                                              | for Filter 5 bit  | s (same values       | s as bits<15:14  | >)              |        |

| bit 9-8       | F4MSK<1:0                                                              | >: Mask Source                                              | for Filter 4 bit  | s (same values       | s as bits<15:14  | >)              |        |

| bit 7-6       | F3MSK<1:0                                                              | >: Mask Source                                              | for Filter 3 bit  | s (same values       | s as bits<15:14  | >)              |        |

| bit 5-4       | F2MSK<1:0                                                              | >: Mask Source                                              | for Filter 2 bit  | s (same values       | s as bits<15:14  | >)              |        |

| bit 3-2       | F1MSK<1:0>: Mask Source for Filter 1 bits (same values as bits<15:14>) |                                                             |                   |                      |                  |                 |        |

|               |                                                                        |                                                             |                   |                      |                  |                 |        |

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

## 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

## 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| DC CHARACTERISTICS |                     |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                 |        |            |  |  |

|--------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|------------|--|--|

| Parameter<br>No.   | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   | nits Conditions |        |            |  |  |

| Idle Current (III  | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |                 |        |            |  |  |

| DC40d              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | -40°C           |        |            |  |  |

| DC40a              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +25°C           | - 3.3V | 10 MIPS    |  |  |

| DC40b              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +85°C           | 3.3V   | 10 101195  |  |  |

| DC40c              | 3                   | 8    | mA                                                                                                                                                                                                                                                                                      | +125°C          |        |            |  |  |