Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (10.7K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

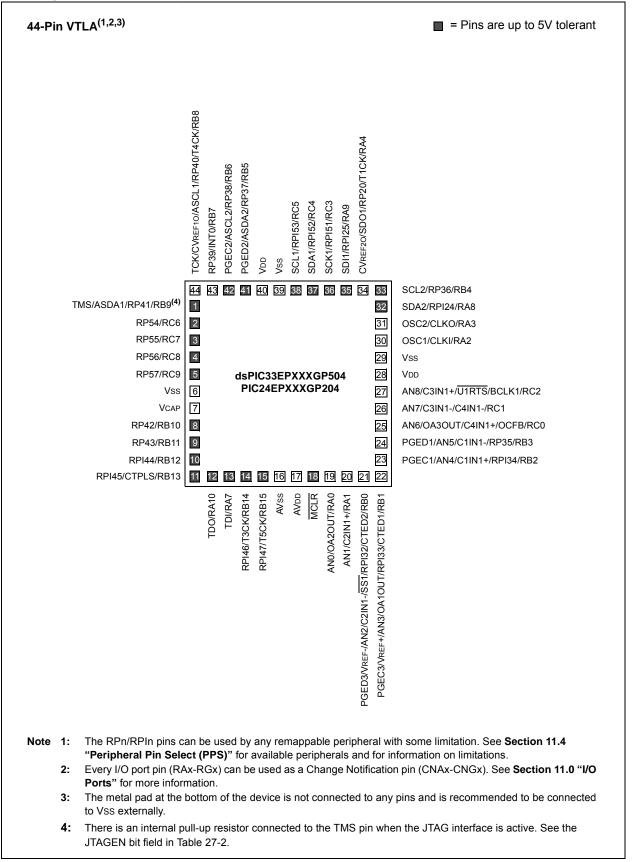

#### **Pin Diagrams (Continued)**

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8               | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------|---------------------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —      | _                   |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —      | _                   |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _      | Baud Rate Generator |       |       |           |              |              |       | 0000  |       |               |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10               | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |        |                     |       |       | I2C1 Addr | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |        |                     |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _      | _                   |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _      | _                   |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _      |                     |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT | ADD10               | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |        |                     |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | _      |        |                     |       |       | I2C2 Add  | dress Mask   |              |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                        | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                   | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|-------------------------------|--------|----------|--------|--------|--------|-------|-------------------------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                        | —      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                   | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                    | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                             | _      | _        | _      | _      | _      | _     | UART1 Transmit Register |            |          |       |            | xxxx     |       |        |       |               |

| U1RXREG     | 0226  | _                             | _      | _        | _      | _      | _      | _     | UART1 Receive Register  |            |          |       |            | 0000     |       |        |       |               |

| U1BRG       | 0228  |                               |        |          |        |        |        | Baud  | Rate Gen                | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                        | _      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                   | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                      | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                    | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                             | _      | _        | _      | _      | _      | _     |                         |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _                             | _      | _        | _      | —      | _      | _     | UART2 Receive Register  |            |          |       |            | 0000     |       |        |       |               |

| U2BRG       | 0238  | Baud Rate Generator Prescaler |        |          |        |        |        |       |                         |            | 0000     |       |            |          |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

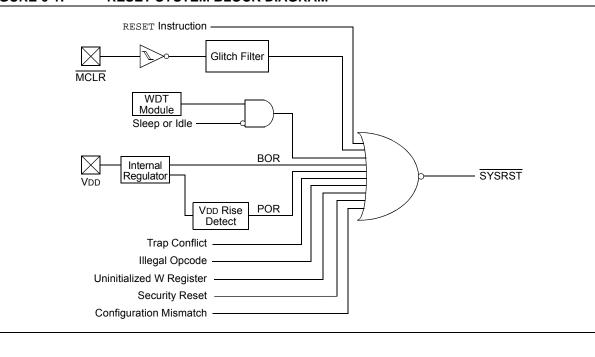

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                  |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                                                          | U-0                                                                                                    | U-0                                        | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|

|                                                              | —                                                                                                      | _                                          | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15                                                       |                                                                                                        | •                                          |                                       | •                    | •                    | •                    | bit                  |  |  |  |

| R/W-0                                                        | R/W-0                                                                                                  | R/W-0                                      | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup>                                          | CKP                                                                                                    | MSTEN                                      | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7                                                        | CKF                                                                                                    | WIGTEN                                     | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |

|                                                              |                                                                                                        |                                            |                                       |                      |                      |                      |                      |  |  |  |

| Legend:                                                      |                                                                                                        |                                            |                                       |                      |                      |                      |                      |  |  |  |

| R = Readabl                                                  | le bit                                                                                                 | W = Writable                               | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at                                                | POR                                                                                                    | '1' = Bit is se                            | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |

|                                                              |                                                                                                        |                                            |                                       |                      |                      |                      |                      |  |  |  |

| bit 15-13                                                    | Unimplemen                                                                                             | ted: Read as                               | 0'                                    |                      |                      |                      |                      |  |  |  |

| bit 12                                                       |                                                                                                        |                                            | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |

|                                                              |                                                                                                        | PIx clock is di                            | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |

| oit 11                                                       |                                                                                                        | able SDOx Pir                              |                                       |                      |                      |                      |                      |  |  |  |

| 1 = SDOx pin is not used by the module; pin functions as I/O |                                                                                                        |                                            |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | 0 = SDOx pin is controlled by the module                                                               |                                            |                                       |                      |                      |                      |                      |  |  |  |

| bit 10                                                       | MODE16: Wo                                                                                             | MODE16: Word/Byte Communication Select bit |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        | 1 = Communication is word-wide (16 bits)   |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        | ication is byte-                           | . ,                                   |                      |                      |                      |                      |  |  |  |

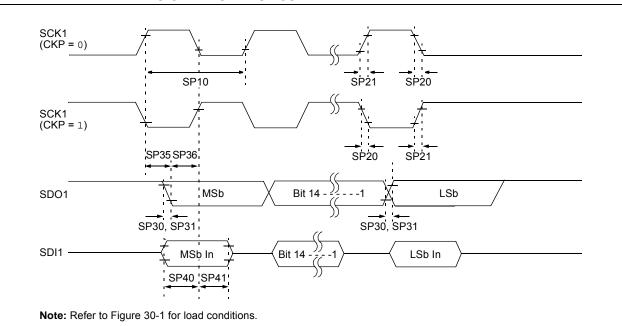

| bit 9                                                        |                                                                                                        | SMP: SPIx Data Input Sample Phase bit      |                                       |                      |                      |                      |                      |  |  |  |

|                                                              | Master mode                                                                                            | -                                          | end of data o                         | utout time           |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        |                                            | middle of data                        |                      |                      |                      |                      |  |  |  |

|                                                              | Slave mode:                                                                                            |                                            |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        |                                            | SPIx is used i                        | n Slave mode.        |                      |                      |                      |  |  |  |

| bit 8                                                        |                                                                                                        | lock Edge Sele                             |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        |                                            |                                       |                      |                      | lle clock state (r   |                      |  |  |  |

| bit 7                                                        |                                                                                                        |                                            |                                       |                      |                      | ve clock state (i    |                      |  |  |  |

|                                                              | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode |                                            |                                       |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        |                                            |                                       | is controlled b      | by port function     |                      |                      |  |  |  |

| bit 6                                                        | CKP: Clock F                                                                                           | Polarity Select                            | bit                                   |                      |                      |                      |                      |  |  |  |

|                                                              |                                                                                                        |                                            | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |

| bit 5                                                        | MSTEN: Mas                                                                                             | ter Mode Enat                              | ole bit                               |                      |                      |                      |                      |  |  |  |

|                                                              | 1 = Master m<br>0 = Slave mo                                                                           |                                            |                                       |                      |                      |                      |                      |  |  |  |

| Note 1: T                                                    | he CKE bit is not                                                                                      | used in Frame                              | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |

|                                                              | his bit must be cl                                                                                     |                                            |                                       |                      |                      |                      |                      |  |  |  |

| <b>0</b>                                                     |                                                                                                        |                                            |                                       |                      |                      |                      |                      |  |  |  |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                              | R/W-0                                                     | R/W-0                         | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------|------------------|-----------------|--------|

| —               | —                                                                                                                | CSIDL                                                     | ABAT                          | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |                                                                                                                  |                                                           |                               |                                |                  |                 | bit 8  |

| R-1             | R-0                                                                                                              | R-0                                                       | U-0                           | R/W-0                          | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1                                                                                                          | OPMODE0                                                   | _                             | CANCAP                         |                  |                 | WIN    |

| bit 7           |                                                                                                                  |                                                           |                               |                                |                  |                 | bit (  |

| Legend:         |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| R = Readable    | bit                                                                                                              | W = Writable I                                            | oit                           | U = Unimpler                   | mented bit, read | d as '0'        |        |

| -n = Value at F | OR                                                                                                               | '1' = Bit is set                                          |                               | '0' = Bit is cle               |                  | x = Bit is unkr | nown   |

|                 |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| bit 15-14       | Unimplemen                                                                                                       | ted: Read as 'o                                           | )'                            |                                |                  |                 |        |

| bit 13          | CSIDL: ECAN                                                                                                      | Nx Stop in Idle I                                         | Node bit                      |                                |                  |                 |        |

|                 |                                                                                                                  | ues module opera module opera                             |                               | device enters I<br>ode         | dle mode         |                 |        |

| bit 12          | ABAT: Abort                                                                                                      | All Pending Tra                                           | nsmissions b                  | bit                            |                  |                 |        |

|                 |                                                                                                                  | I transmit buffe<br>ill clear this bit                    |                               | ansmission<br>smissions are a  | aborted          |                 |        |

| bit 11          | CANCKS: EC                                                                                                       | ANx Module C                                              | lock (FCAN)                   | Source Select b                | bit              |                 |        |

|                 | 1 = FCAN is equal to 2 * FP<br>0 = FCAN is equal to FP                                                           |                                                           |                               |                                |                  |                 |        |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis | ed<br>nfiguration moo<br>ten Only mode<br>opback mode     | es mode<br>le                 | bits                           |                  |                 |        |

| bit 7-5         | 111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module                                                     |                                                           | Messages n<br>ation mode      | node                           |                  |                 |        |

|                 | 010 = Module<br>001 = Module<br>000 = Module                                                                     | e is in Loopback<br>e is in Disable n<br>e is in Normal C | mode<br>node<br>operation mod | de                             |                  |                 |        |

| bit 4           | -                                                                                                                | ted: Read as '                                            |                               |                                |                  |                 |        |

| bit 3           |                                                                                                                  | nput capture ba                                           |                               | Capture Event<br>message recei |                  |                 |        |

| bit 2-1         |                                                                                                                  | ted: Read as '(                                           | ı'                            |                                |                  |                 |        |

| bit 0           | -                                                                                                                | ap Window Sele                                            |                               |                                |                  |                 |        |

| UIL U           | 1 = Uses filter                                                                                                  | -                                                         | יטו טונ                       |                                |                  |                 |        |

| U-0          | U-0                                          | R-0                                           | R-0   | R-0               | R-0              | R-0             | R-0   |  |  |  |

|--------------|----------------------------------------------|-----------------------------------------------|-------|-------------------|------------------|-----------------|-------|--|--|--|

| _            |                                              | FBP5                                          | FBP4  | FBP3              | FBP2             | FBP1            | FBP0  |  |  |  |

| bit 15       |                                              |                                               |       |                   |                  |                 | bit 8 |  |  |  |

|              |                                              |                                               |       |                   |                  |                 |       |  |  |  |

| U-0          | U-0                                          | R-0                                           | R-0   | R-0               | R-0              | R-0             | R-0   |  |  |  |

|              |                                              | FNRB5                                         | FNRB4 | FNRB3             | FNRB2            | FNRB1           | FNRB0 |  |  |  |

| bit 7        |                                              |                                               |       |                   |                  |                 | bit ( |  |  |  |

| Legend:      |                                              |                                               |       |                   |                  |                 |       |  |  |  |

| R = Readab   | le bit                                       | W = Writable                                  | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value a | t POR                                        | '1' = Bit is set                              |       | '0' = Bit is clea |                  | x = Bit is unkr | iown  |  |  |  |

|              |                                              |                                               |       |                   |                  |                 |       |  |  |  |

| bit 15-14    | Unimpleme                                    | ented: Read as '                              | 0'    |                   |                  |                 |       |  |  |  |

| bit 13-8     | FBP<5:0>: FIFO Buffer Pointer bits           |                                               |       |                   |                  |                 |       |  |  |  |

|              | 011111 = RB31 buffer                         |                                               |       |                   |                  |                 |       |  |  |  |

|              | 011110 <b>= F</b>                            | RB30 buffer                                   |       |                   |                  |                 |       |  |  |  |

|              | •                                            |                                               |       |                   |                  |                 |       |  |  |  |

|              | •                                            |                                               |       |                   |                  |                 |       |  |  |  |

|              | •<br>000001 = TRB1 buffer                    |                                               |       |                   |                  |                 |       |  |  |  |

|              | 000000 = TRB1 buller<br>000000 = TRB0 buller |                                               |       |                   |                  |                 |       |  |  |  |

| bit 7-6      | Unimpleme                                    | ented: Read as '                              | 0'    |                   |                  |                 |       |  |  |  |

| bit 5-0      | FNRB<5:0                                     | FNRB<5:0>: FIFO Next Read Buffer Pointer bits |       |                   |                  |                 |       |  |  |  |

|              | 011111 = RB31 buffer                         |                                               |       |                   |                  |                 |       |  |  |  |

|              | 011110 <b>= F</b>                            | RB30 buffer                                   |       |                   |                  |                 |       |  |  |  |

|              | •                                            |                                               |       |                   |                  |                 |       |  |  |  |

|              | •                                            |                                               |       |                   |                  |                 |       |  |  |  |

|              | •                                            |                                               |       |                   |                  |                 |       |  |  |  |

|              |                                              |                                               |       |                   |                  |                 |       |  |  |  |

|              |                                              | FRB1 buffer<br>FRB0 buffer                    |       |                   |                  |                 |       |  |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-20: | CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER |

|-----------------|---------------------------------------------------------------|

|                 | REGISTER (n = 0-2)                                            |

|                                   |                                                                                                                             | -                                        | -             |                                                 |                 |       |       |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|-------------------------------------------------|-----------------|-------|-------|--|--|--|

| R/W-x                             | R/W-x                                                                                                                       | R/W-x                                    | R/W-x         | R/W-x                                           | R/W-x           | R/W-x | R/W-x |  |  |  |

| SID10                             | SID9                                                                                                                        | SID8                                     | SID7          | SID6                                            | SID5            | SID4  | SID3  |  |  |  |

| bit 15                            |                                                                                                                             |                                          |               |                                                 |                 |       | bit 8 |  |  |  |

| R/W-x                             | R/W-x                                                                                                                       | R/W-x R/W-x U-0 R/W-x U-0                |               |                                                 |                 | R/W-x | R/W-x |  |  |  |

| SID2                              | SID1                                                                                                                        | SID0                                     | -             | MIDE                                            | _               | EID17 | EID16 |  |  |  |

| bit 7                             |                                                                                                                             |                                          |               |                                                 |                 |       | bit C |  |  |  |

| <u> </u>                          |                                                                                                                             |                                          |               |                                                 |                 |       |       |  |  |  |

| Legend:                           |                                                                                                                             |                                          |               |                                                 |                 |       |       |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                             |                                          |               | U = Unimplemented bit, read as '0'              |                 |       |       |  |  |  |

| -n = Value a                      | at POR                                                                                                                      | '1' = Bit is set                         | :             | '0' = Bit is cle                                | x = Bit is unkr | iown  |       |  |  |  |

| bit 15-5                          | SID<10:0>: S                                                                                                                | Standard Identii                         | fier bits     |                                                 |                 |       |       |  |  |  |

|                                   |                                                                                                                             | bit, SIDx, in filte<br>is a don't care i |               |                                                 |                 |       |       |  |  |  |

| bit 4                             | Unimplemer                                                                                                                  | nted: Read as '                          | 0'            |                                                 |                 |       |       |  |  |  |

| bit 3                             | MIDE: Identif                                                                                                               | fier Receive Mo                          | de bit        |                                                 |                 |       |       |  |  |  |

|                                   | 0 = Matches                                                                                                                 |                                          | or extended a | d or extended ac<br>address messag<br>SID/EID)) |                 | •     |       |  |  |  |

| bit 2                             | Unimplemented: Read as '0'                                                                                                  |                                          |               |                                                 |                 |       |       |  |  |  |

| bit 1-0                           | EID<17:16>:                                                                                                                 | Extended Iden                            | tifier bits   |                                                 |                 |       |       |  |  |  |

|                                   | <ul> <li>1 = Includes bit, EIDx, in filter comparison</li> <li>0 = EIDx bit is a don't care in filter comparison</li> </ul> |                                          |               |                                                 |                 |       |       |  |  |  |

|                                   |                                                                                                                             |                                          |               |                                                 |                 |       |       |  |  |  |

#### REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x        | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| EID15        | EID14 | EID13        | EID12 | EID11        | EID10            | EID9   | EID8  |

| bit 15       |       |              |       | ·            |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-x        | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

| EID7         | EID6  | EID5         | EID4  | EID3         | EID2             | EID1   | EID0  |

| bit 7        |       |              |       |              |                  | •      | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

# 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                | R/W-0                               | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |  |

|---------------|------------------------------------|-------------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|--|

| ADON          | —                                  | ADSIDL                              | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |  |

| bit 15        | •                                  |                                     |                     |                   |                  |                                     | bit 8               |  |

| R/W-0         | R/W-0                              | R/W-0                               | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |  |

| SSRC2         | SSRC1                              | SSRC0                               | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |  |

| bit 7         |                                    |                                     |                     |                   |                  |                                     | bit (               |  |

| Legend:       |                                    | HC - Hardwar                        | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |  |

| R = Readable  | a hit                              | W = Writable b                      |                     |                   | nented bit, read |                                     | L                   |  |

| -n = Value at |                                    | '1' = Bit is set                    | nt -                | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |  |

|               | FUR                                | I - DILIS SEL                       |                     |                   |                  |                                     |                     |  |

| bit 15        | ADON: ADO                          | C1 Operating M                      | ode bit             |                   |                  |                                     |                     |  |

|               | 1 = ADC mo<br>0 = ADC is 0         | odule is operatir<br>off            | ng                  |                   |                  |                                     |                     |  |

| bit 14        | Unimpleme                          | nted: Read as                       | <b>'</b> 0 <b>'</b> |                   |                  |                                     |                     |  |

| bit 13        | ADSIDL: ADC1 Stop in Idle Mode bit |                                     |                     |                   |                  |                                     |                     |  |

|               | 1 = Disconti                       | nues module oj                      | peration when o     | device enters     | ldle mode        |                                     |                     |  |

|               | 0 = Continu                        | es module oper                      | ation in Idle mo    | ode               |                  |                                     |                     |  |

| bit 12        |                                    | : DMA Buffer B                      |                     |                   |                  |                                     |                     |  |

|               |                                    |                                     |                     |                   |                  | rovides an addre                    | ess to the DM       |  |

|               |                                    |                                     |                     |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |  |

|               |                                    |                                     |                     |                   |                  | size of the DMA b                   |                     |  |

| bit 11        |                                    | nted: Read as                       |                     |                   |                  |                                     |                     |  |

| bit 10        | AD12B: AD                          | C1 10-Bit or 12                     | -Bit Operation I    | Mode bit          |                  |                                     |                     |  |

|               |                                    | -channel ADC                        | -                   |                   |                  |                                     |                     |  |

|               | 0 = 10-bit, 4                      | -channel ADC                        | operation           |                   |                  |                                     |                     |  |

| bit 9-8       | FORM<1:0>                          | Data Output I                       | Format bits         |                   |                  |                                     |                     |  |