Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

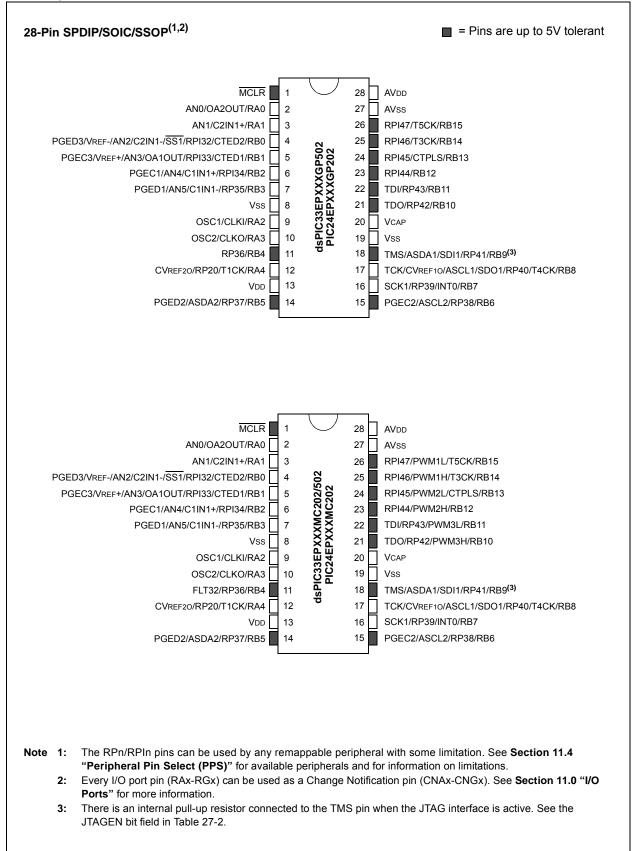

### **Pin Diagrams**

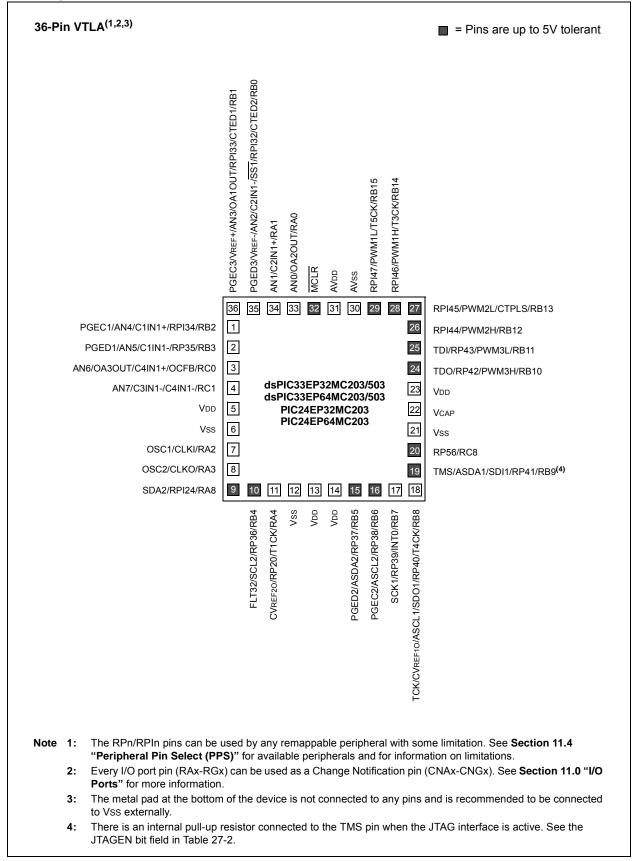

### Pin Diagrams (Continued)

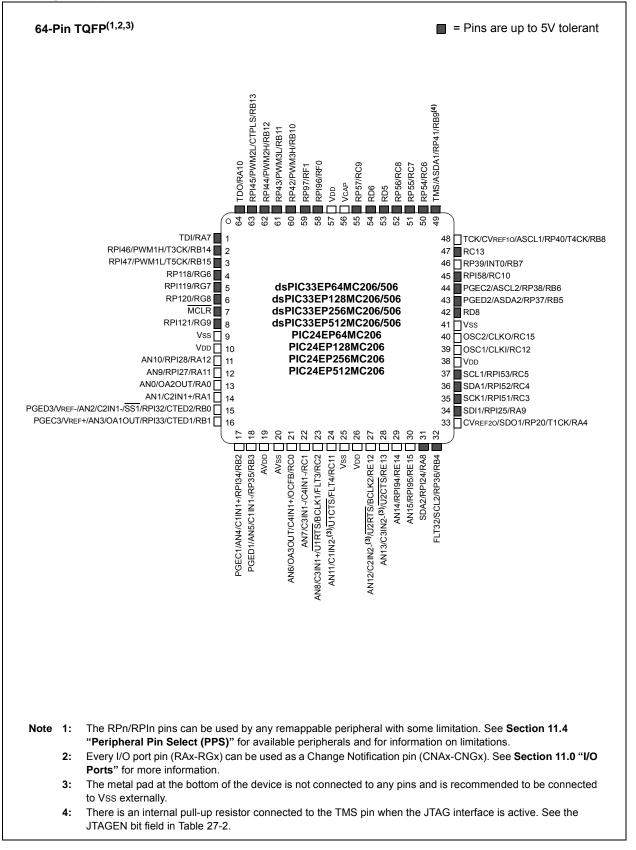

### Pin Diagrams (Continued)

### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

| <b>SUMIMAR I</b> |                         |                   |  |  |  |  |  |  |

|------------------|-------------------------|-------------------|--|--|--|--|--|--|

| Instruction      | Algebraic<br>Operation  | ACC Write<br>Back |  |  |  |  |  |  |

| CLR              | A = 0                   | Yes               |  |  |  |  |  |  |

| ED               | $A = (x - y)^2$         | No                |  |  |  |  |  |  |

| EDAC             | $A = A + (x - y)^2$     | No                |  |  |  |  |  |  |

| MAC              | $A = A + (x \bullet y)$ | Yes               |  |  |  |  |  |  |

| MAC              | $A = A + x^2$           | No                |  |  |  |  |  |  |

| MOVSAC           | No change in A          | Yes               |  |  |  |  |  |  |

| MPY              | $A = x \bullet y$       | No                |  |  |  |  |  |  |

| MPY              | $A = x^2$               | No                |  |  |  |  |  |  |

| MPY.N            | $A = -x \bullet y$      | No                |  |  |  |  |  |  |

| MSC              | $A = A - x \bullet y$   | Yes               |  |  |  |  |  |  |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

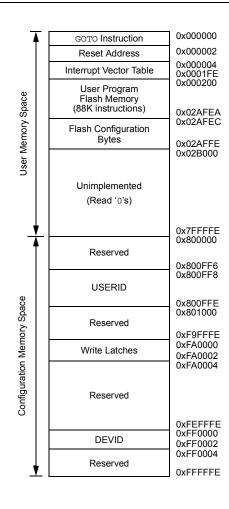

### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |  |  |  |  |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |  |  |  |  |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |  |  |  |  |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |  |  |  |  |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |  |  |  |  |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |  |  |  |  |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |  |  |  |  |

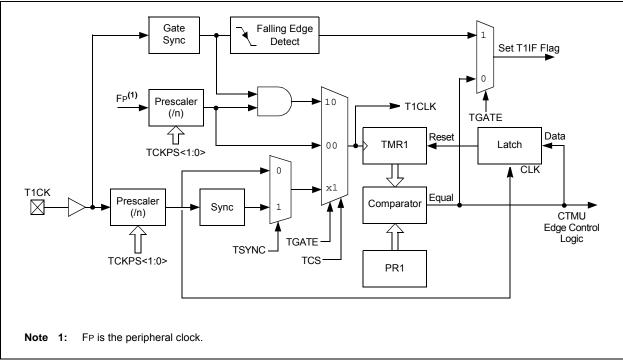

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

### TABLE 12-1: TIMER MODE SETTINGS

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

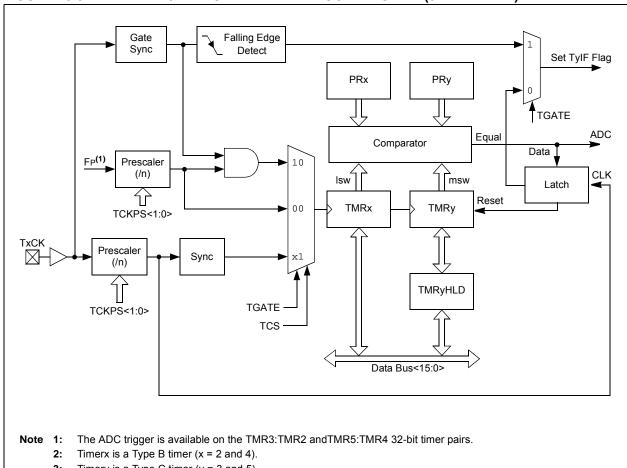

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                     | ,_, ., ., ., .,                                                      | -,-,-,                |                  |                  |                 |                 |  |  |  |

|---------------|-----------------------|----------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|-----------------|--|--|--|

| R/W-0         | R-0                   | R-0                                                                  | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENn         | TXABTn                | TXLARBn                                                              | TXERRn                | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |

| bit 15        |                       |                                                                      |                       |                  |                  |                 | bit 8           |  |  |  |

| R/W-0         | R-0                   | R-0                                                                  | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup>                                               | TXERRm <sup>(1)</sup> | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |

| bit 7         |                       |                                                                      |                       |                  |                  |                 | bit C           |  |  |  |

| Legend:       |                       |                                                                      |                       |                  |                  |                 |                 |  |  |  |

| R = Readabl   | le bit                | W = Writable                                                         | bit                   | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |

| -n = Value at | t POR                 | '1' = Bit is set                                                     |                       | '0' = Bit is cle | ared             | x = Bit is unki | nown            |  |  |  |

| bit 15-8      | See Definitio         | n for bits<7:0>,                                                     | Controls Buffe        | <u>er n</u>      |                  |                 |                 |  |  |  |

| bit 7         |                       | RX Buffer Sele                                                       |                       |                  |                  |                 |                 |  |  |  |

|               |                       | RBn is a transm                                                      |                       |                  |                  |                 |                 |  |  |  |

|               | 0 = Buffer TR         | RBn is a receive                                                     | buffer                |                  |                  |                 |                 |  |  |  |

| bit 6         | TXABTm: Me            | TXABTm: Message Aborted bit <sup>(1)</sup>                           |                       |                  |                  |                 |                 |  |  |  |

|               |                       | 1 = Message was aborted                                              |                       |                  |                  |                 |                 |  |  |  |

|               |                       | completed tran                                                       |                       |                  |                  |                 |                 |  |  |  |

| bit 5         |                       | Message Lost A                                                       |                       |                  |                  |                 |                 |  |  |  |

|               |                       | lost arbitration did not lose ar                                     |                       |                  |                  |                 |                 |  |  |  |

| bit 4         | TXERRm: Er            | <b>TXERRm:</b> Error Detected During Transmission bit <sup>(1)</sup> |                       |                  |                  |                 |                 |  |  |  |

|               |                       | or occurred wh<br>or did not occu                                    |                       |                  |                  |                 |                 |  |  |  |

| bit 3         |                       | essage Send F                                                        |                       |                  |                  |                 |                 |  |  |  |

|               |                       | 0                                                                    | •                     | bit automatic    | ally clears wher | n the message   | is successfully |  |  |  |

|               | 0 = Clearing          | the bit to '0' wh                                                    | nile set reques       | ts a message     | abort            |                 |                 |  |  |  |

| bit 2         | RTRENm: Au            | uto-Remote Tra                                                       | Insmit Enable         | bit              |                  |                 |                 |  |  |  |

|               |                       | emote transmit<br>emote transmit                                     |                       |                  |                  |                 |                 |  |  |  |

| bit 1-0       | TXmPRI<1:0            | >: Message Tra                                                       | ansmission Pri        | iority bits      |                  |                 |                 |  |  |  |

|               | 11 = Highest          | message prior                                                        | ity                   |                  |                  |                 |                 |  |  |  |

|               | 0                     | ermediate mes                                                        |                       |                  |                  |                 |                 |  |  |  |

|               |                       | ermediate mess<br>message priori                                     |                       |                  |                  |                 |                 |  |  |  |

|               |                       |                                                                      | -                     |                  |                  |                 |                 |  |  |  |

| Note 1: ⊤     | his bit is cleared    | when TXREQ                                                           | s set.                |                  |                  |                 |                 |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

| oit 3-0 | Step<br>Command        | d OPTION<3:0> Option Description |                                                                                                         |  |  |  |  |  |

|---------|------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | PTGCTRL(1)             | 0000                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0001                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0010                             | Disable Step Delay Timer (PTGSD).                                                                       |  |  |  |  |  |

|         |                        | 0011                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0100                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0101                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0110                             | Enable Step Delay Timer (PTGSD).                                                                        |  |  |  |  |  |

|         |                        | 0111                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 1000                             | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |  |  |  |  |  |

|         |                        | 1001                             | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |  |  |  |  |  |

|         |                        | 1010                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 1011                             | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |  |  |  |  |  |

|         |                        | 1100                             | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |  |  |  |  |  |

|         |                        | 1101                             | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |  |  |  |  |  |

|         |                        | 1110                             | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |  |  |  |  |  |

|         |                        | 1111                             | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |  |  |  |  |  |

|         | PTGADD(1)              | 0000                             | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |  |  |  |  |  |

|         |                        | 0001                             | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |  |  |  |  |  |

|         |                        | 0010                             | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |  |  |  |  |  |

|         |                        | 0011                             | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |  |  |  |  |  |

|         |                        | 0100                             | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                         |  |  |  |  |  |

|         |                        | 0101                             | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |  |  |  |  |  |

|         |                        | 0110                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 0111                             | Reserved.                                                                                               |  |  |  |  |  |

|         | PTGCOPY <sup>(1)</sup> | 1000                             | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |  |  |  |  |  |

|         |                        | 1001                             | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |  |  |  |  |  |

|         |                        | 1010                             | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |  |  |  |  |  |

|         |                        | 1011                             | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |  |  |  |  |  |

|         |                        | 1100                             | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |  |  |  |  |  |

|         |                        | 1101                             | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |  |  |  |  |  |

|         |                        | 1110                             | Reserved.                                                                                               |  |  |  |  |  |

|         |                        | 1111                             | Reserved.                                                                                               |  |  |  |  |  |

### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

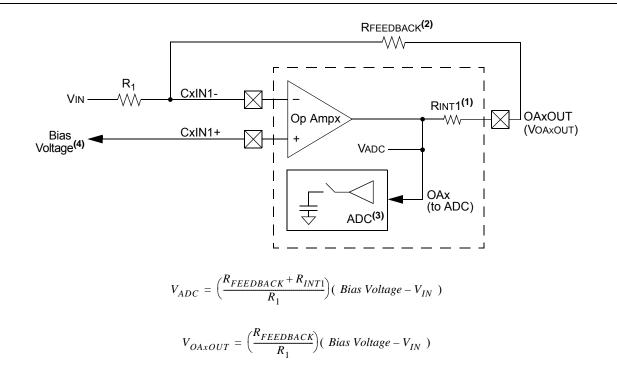

### 25.1 Op Amp Application Considerations

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

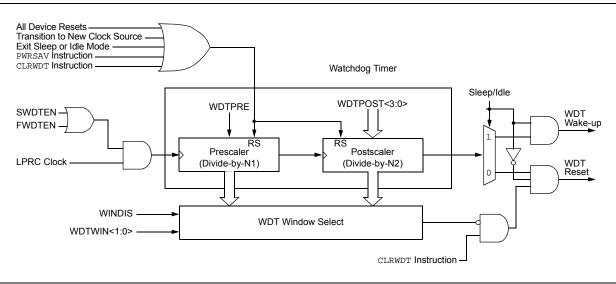

### 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

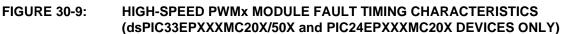

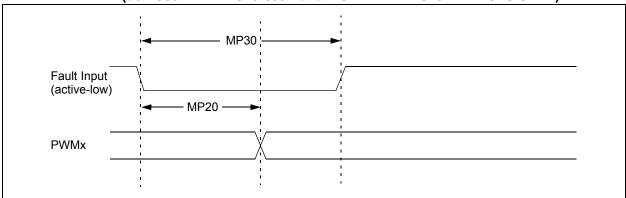

### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | (unless                         | rd Operat<br>otherwis<br>ng tempe | se stated | )<br>-40°C ≤ T | 8.0V to 3.6V<br>A ≤ +85°C for Industrial<br>A ≤ +125°C for Extended |

|--------------------|--------|-------------------------------------|---------------------------------|-----------------------------------|-----------|----------------|---------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min. Typ. Max. Units Conditions |                                   |           |                | Conditions                                                          |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                 | —                                 | _         | ns             | See Parameter DO32                                                  |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                               | —                                 | _         | ns             | See Parameter DO31                                                  |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                               | _                                 | 15        | ns             |                                                                     |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                              | _                                 | _         | ns             |                                                                     |

**Note 1:** These parameters are characterized but not tested in manufacturing.

| AC CHARACTERISTICS |        |                                                  | (unless  |           | se stateo<br>rature | <b>i)<sup>(1)</sup></b><br>-40°C ≤ <sup>-</sup> | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended |

|--------------------|--------|--------------------------------------------------|----------|-----------|---------------------|-------------------------------------------------|----------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Min.                                             | Тур.     | Max.      | Units               | Conditions                                      |                                                                                        |

|                    |        | ADC A                                            | Accuracy | (12-Bit   | Mode)               |                                                 |                                                                                        |

| AD20a              | Nr     | Resolution                                       | 12       | 2 Data Bi | its                 | bits                                            |                                                                                        |

| AD21a              | INL    | Integral Nonlinearity                            | -2.5     |           | 2.5                 | LSb                                             | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2)                                        |

|                    |        |                                                  | -5.5     | —         | 5.5                 | LSb                                             | +85°C $<$ TA $\leq$ +125°C (Note 2)                                                    |

| AD22a              | DNL    | Differential Nonlinearity                        | -1       | _         | 1                   | LSb                                             | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                                                  |

|                    |        |                                                  | -1       | —         | 1                   | LSb                                             | +85°C $<$ TA $\leq$ +125°C (Note 2)                                                    |

| AD23a              | Gerr   | Gain Error <sup>(3)</sup>                        | -10      | _         | 10                  | LSb                                             | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                                                  |

|                    |        |                                                  | -10      | _         | 10                  | LSb                                             | +85°C < TA $\leq$ +125°C (Note 2)                                                      |

| AD24a              | EOFF   | Offset Error                                     | -5       | —         | 5                   | LSb                                             | $-40^{\circ}C \le TA \le +85^{\circ}C$ (Note 2)                                        |

|                    |        |                                                  | -5       | —         | 5                   | LSb                                             | +85°C < TA $\leq$ +125°C (Note 2)                                                      |

| AD25a              | —      | Monotonicity                                     | —        |           |                     |                                                 | Guaranteed                                                                             |

|                    |        | Dynamic                                          | Performa | ance (12- | -Bit Mod            | e)                                              |                                                                                        |

| AD30a              | THD    | Total Harmonic Distortion <sup>(3)</sup>         | _        | 75        |                     | dB                                              |                                                                                        |

| AD31a              | SINAD  | Signal to Noise and<br>Distortion <sup>(3)</sup> | —        | 68        |                     | dB                                              |                                                                                        |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup>    | —        | 80        | —                   | dB                                              |                                                                                        |

| AD33a              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>            | —        | 250       | —                   | kHz                                             |                                                                                        |

| AD34a              | ENOB   | Effective Number of Bits <sup>(3)</sup>          | 11.09    | 11.3      |                     | bits                                            |                                                                                        |

### TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

3: Parameters are characterized but not tested in manufacturing.

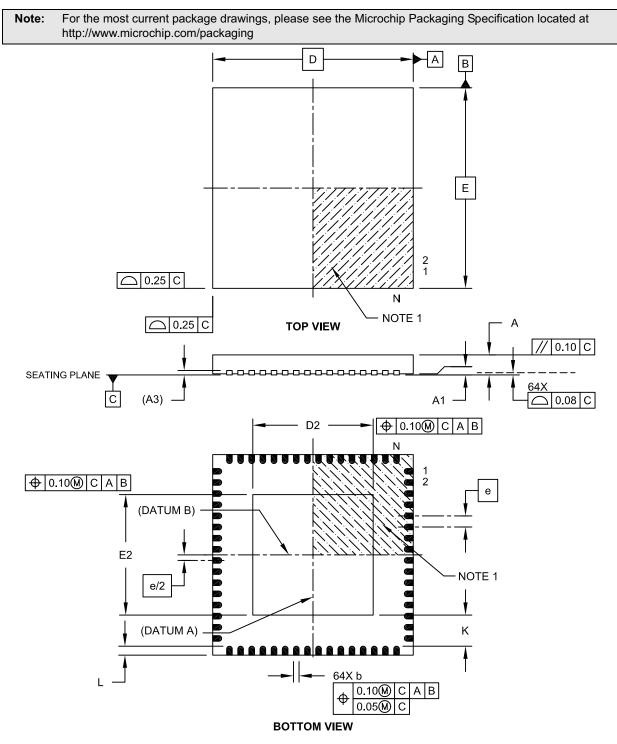

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |

|-------------------------|-------------|----------------|----------|------|--|

| Dimension               | MIN         | NOM            | MAX      |      |  |

| Number of Pins          | N           |                | 44       |      |  |

| Pitch                   | е           |                | 0.65 BSC |      |  |

| Overall Height          | A           | 0.80           | 0.90     | 1.00 |  |

| Standoff                | A1          | 0.00           | 0.02     | 0.05 |  |

| Terminal Thickness      | A3          | 0.20 REF       |          |      |  |

| Overall Width           | E           | 8.00 BSC       |          |      |  |

| Exposed Pad Width       | E2          | 6.25           | 6.45     | 6.60 |  |

| Overall Length          | D           | 8.00 BSC       |          |      |  |

| Exposed Pad Length      | D2          | 6.25 6.45 6.60 |          |      |  |

| Terminal Width          | b           | 0.20           | 0.30     | 0.35 |  |

| Terminal Length         | L           | 0.30           | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K           | 0.20           | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

### TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)