Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (10.7K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32mc504t-i-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

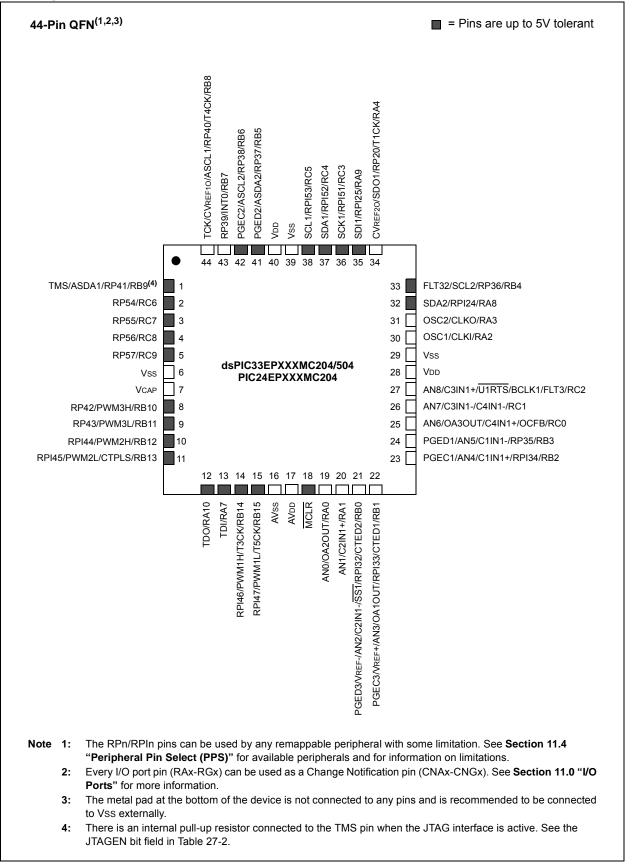

## Pin Diagrams (Continued)

#### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

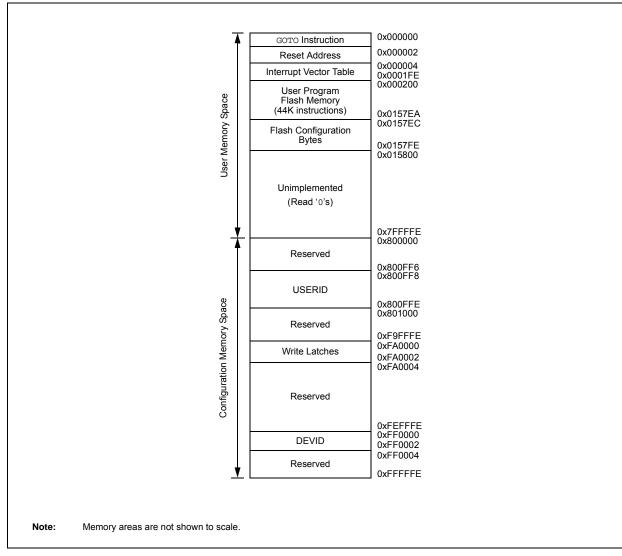

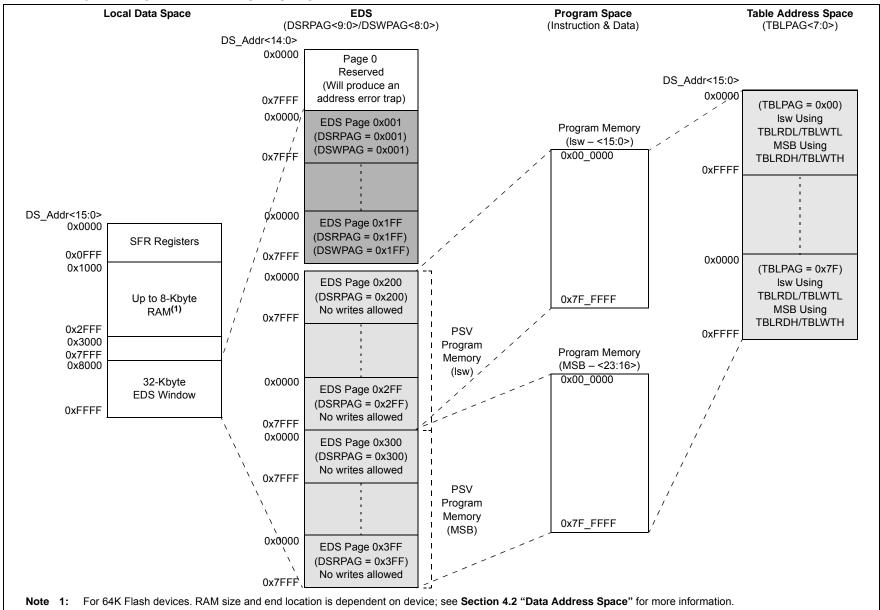

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

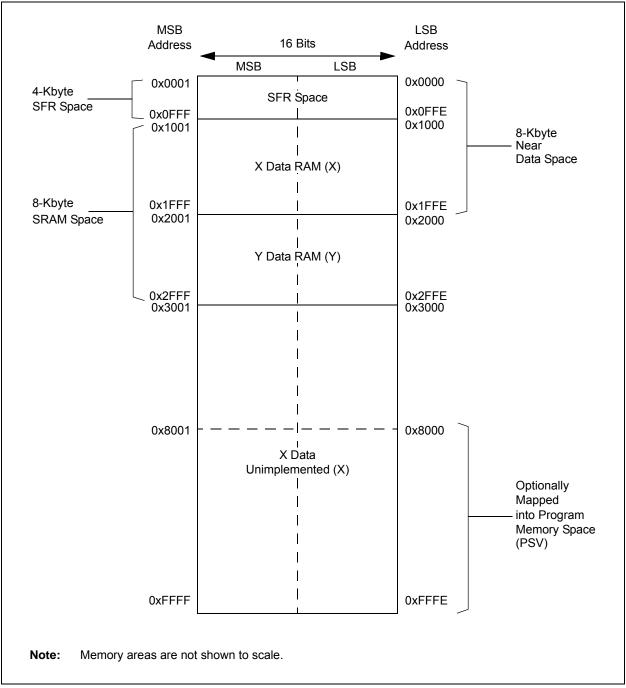

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |         |        |              |            |        |       | 20/0/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|---------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14  | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |         |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |         |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |         |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |         |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |         |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |         |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |         |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |         |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |         |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |         |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |         |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |         |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |         |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        | W13 xx: |        |              |            |        |       |             |        |       |        | xxxx    |          |          |       |       |               |

| W14       | 001C  |        | W14 xxx |        |              |            |        |       |             |        |       |        | xxxx    |          |          |       |       |               |

| W15       | 001E  |        | W15 x   |        |              |            |        |       |             |        |       | xxxx   |         |          |          |       |       |               |

| SPLIM     | 0020  |        |         |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |         |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |         |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |         | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |         |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |         |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |         | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |         |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       | —     | 0000          |

| PCH       | 0030  | _      | _       | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _       | _      | _            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |         | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |         |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |         |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |         |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —       | —      | _            | —          | —      | _     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |         |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —       | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |         |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

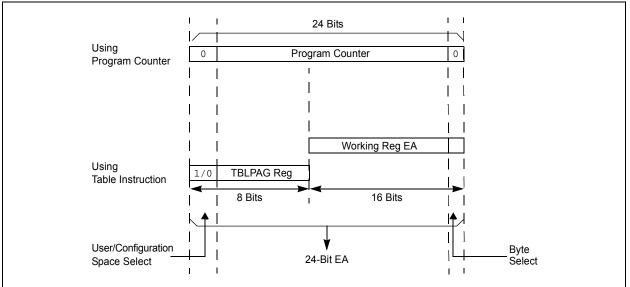

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| U-0                                                                        | U-0          | U-0                                    | U-0           | U-0                | U-0      | U-0    | U-0    |  |  |  |

|----------------------------------------------------------------------------|--------------|----------------------------------------|---------------|--------------------|----------|--------|--------|--|--|--|

| —                                                                          | —            | —                                      | —             | —                  | —        | —      | —      |  |  |  |

| bit 15                                                                     |              |                                        |               |                    |          |        | bit 8  |  |  |  |

|                                                                            |              |                                        |               |                    |          |        |        |  |  |  |

| U-0                                                                        | U-0          | U-0                                    | U-0           | R-0                | R-0      | R-0    | R-0    |  |  |  |

|                                                                            | <u> </u>     | <u> </u>                               | _             | PWCOL3             | PWCOL2   | PWCOL1 | PWCOL0 |  |  |  |

| bit 7                                                                      |              |                                        |               |                    |          |        | bit 0  |  |  |  |

|                                                                            |              |                                        |               |                    |          |        |        |  |  |  |

| Legend:                                                                    |              |                                        |               |                    |          |        |        |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |              |                                        |               |                    |          |        |        |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |                                        |               |                    |          |        |        |  |  |  |

|                                                                            |              |                                        |               |                    |          |        |        |  |  |  |

| bit 15-4                                                                   | Unimplemen   | ted: Read as '                         | 0'            |                    |          |        |        |  |  |  |

| bit 3                                                                      | PWCOL3: DI   | MA Channel 3 F                         | Peripheral Wi | rite Collision Fla | ag bit   |        |        |  |  |  |

|                                                                            |              | lision is detecte                      |               |                    |          |        |        |  |  |  |

|                                                                            |              | collision is dete                      |               |                    |          |        |        |  |  |  |

| bit 2                                                                      |              |                                        | •             | rite Collision Fla | ag bit   |        |        |  |  |  |

|                                                                            |              | lision is detecte<br>collision is dete |               |                    |          |        |        |  |  |  |

| bit 1                                                                      |              |                                        |               | rite Collision Fla | a hit    |        |        |  |  |  |

| DILI                                                                       |              | lision is detecte                      | •             |                    |          |        |        |  |  |  |

|                                                                            |              | 0 = No write collision is detected     |               |                    |          |        |        |  |  |  |

| bit 0                                                                      | PWCOL0: DI   | MA Channel 0 F                         | Peripheral Wi | rite Collision Fla | ag bit   |        |        |  |  |  |

|                                                                            |              | lision is detecte                      | •             | -                  | <b>č</b> |        |        |  |  |  |

|                                                                            | 0 = No write | collision is dete                      | ected         |                    |          |        |        |  |  |  |

|                                                                            |              |                                        |               |                    |          |        |        |  |  |  |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| U-0             | U-0                                                                                                                                           | R/W-0          | R/W-0 | R/W-0                                   | R/W-0  | R/W-0 | R/W-0 |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|-----------------------------------------|--------|-------|-------|--|--|

| —               | —                                                                                                                                             |                |       | RP57                                    | R<5:0> |       |       |  |  |

| bit 15          |                                                                                                                                               |                |       |                                         |        |       | bit 8 |  |  |

|                 |                                                                                                                                               |                |       |                                         |        |       |       |  |  |

| U-0             | U-0                                                                                                                                           | R/W-0          | R/W-0 | R/W-0                                   | R/W-0  | R/W-0 | R/W-0 |  |  |

| _               | —                                                                                                                                             |                |       | RP56                                    | R<5:0> |       |       |  |  |

| bit 7           |                                                                                                                                               |                |       |                                         |        |       | bit 0 |  |  |

|                 |                                                                                                                                               |                |       |                                         |        |       |       |  |  |

| Legend:         |                                                                                                                                               |                |       |                                         |        |       |       |  |  |

| R = Readable I  | bit                                                                                                                                           | W = Writable   | bit   | U = Unimplemented bit, read as '0'      |        |       |       |  |  |

| -n = Value at P | -n = Value at POR '1' = Bit is set                                                                                                            |                |       | '0' = Bit is cleared x = Bit is unknown |        |       |       |  |  |

|                 |                                                                                                                                               |                |       |                                         |        |       |       |  |  |

| bit 15-14       | Unimplemen                                                                                                                                    | ted: Read as ' | 0'    |                                         |        |       |       |  |  |

| bit 13-8        | 13-8 <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                |       |                                         |        |       |       |  |  |

| bit 7-6         | Unimplemen                                                                                                                                    | ted: Read as ' | 0'    |                                         |        |       |       |  |  |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

#### 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|--|--|--|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0                           | U-0                                                                                              | R/W-0                                                                                                          | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |  |  |  |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN                           | _                                                                                                | QEISIDL                                                                                                        | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                                          | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |  |  |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          | bit 15                          |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 8               |  |  |  |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          |                                 |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0                             |                                                                                                  |                                                                                                                |                                                                                              | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |                                 | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                         | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                                         | GATEN                                                      | CCM1                              |                     |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7                           |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 0               |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy                         |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |                                 | lo hit                                                                                           |                                                                                                                | hit                                                                                          | II – Unimplor                                                                                  | monted bit read                                            | ac '0'                            |                     |  |  |  |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |                                 |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a                    | PUR                                                                                              | I = Bit is set                                                                                                 |                                                                                              | 0 = Bit is cle                                                                                 | ared                                                       | x = Bit is unkr                   | lown                |  |  |  |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | 1 = Module counters are enabled |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14                          | Unimplemented: Read as '0'                                                                       |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                              | bit 13                          | QEISIDL: QE                                                                                      | -                                                                                                              |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| <ul> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>011 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>0 = Phase A match occurs when QEA = 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                | dle mode                                                   |                                   |                     |  |  |  |

| <ul> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 12-10                       | PIMOD<2:0>                                                                                       | : Position Cour                                                                                                | nter Initializatio                                                                           | on Mode Selec                                                                                  | t bits <sup>(1)</sup>                                      |                                   |                     |  |  |  |

| 1 = Phase B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 | 110 = Module<br>101 = Resets<br>100 = Second<br>011 = First in<br>010 = Next in<br>001 = Every i | b Count mode f<br>the position co<br>d index event a<br>dex event after<br>idex input even<br>index input even | bunter when the<br>fter home event<br>home event in<br>t initializes the<br>put resets the p | e position cou<br>at initializes posi<br>nitializes positi<br>position coun<br>position counte | sition counter wit<br>on counter with<br>ter with contents | h contents of C<br>contents of QE | EI1IC register      |  |  |  |

| 0 = Phase B match occurs when QEB = 0         bit 8         IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7         Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 9                           | IMV1: Index I                                                                                    | Match Value for                                                                                                | <sup>-</sup> Phase B bit <sup>(2</sup>                                                       | )                                                                                              |                                                            |                                   |                     |  |  |  |

| bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1         0 = Phase A match occurs when QEA = 0         bit 7       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |  |  |  |

| 1 = Phase A match occurs when QEA = 10 = Phase A match occurs when QEA = 0bit 7Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |                                                                                                  |                                                                                                                |                                                                                              | <b>N</b>                                                                                       |                                                            |                                   |                     |  |  |  |