Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

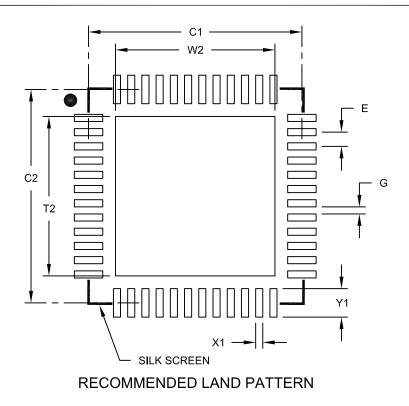

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp502-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

|                                               | Vector | IRQ        |                   | Inte     | errupt Bit L | ocation     |

|-----------------------------------------------|--------|------------|-------------------|----------|--------------|-------------|

| Interrupt Source                              | #      | #          | IVT Address       | Flag     | Enable       | Priority    |

|                                               | High   | est Natura | I Order Priority  |          |              |             |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>  | IEC0<0>      | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>  | IEC0<1>      | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>  | IEC0<2>      | IPC0<10:8>  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>  | IEC0<3>      | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>  | IEC0<4>      | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>  | IEC0<5>      | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>  | IEC0<6>      | IPC1<10:8>  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>  | IEC0<7>      | IPC1<14:12> |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>  | IEC0<8>      | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>  | IEC0<9>      | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10> | IEC0<10>     | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11> | IEC0<11>     | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12> | IEC0<12>     | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13> | IEC0<13>     | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14> | IEC0<14>     | IPC3<10:8>  |

| Reserved                                      | 23     | 15         | 0x000032          |          |              | _           |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>  | IEC1<0>      | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>  | IEC1<1>      | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>  | IEC1<2>      | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>  | IEC1<3>      | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>  | IEC1<4>      | IPC5<2:0>   |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 |          |              | _           |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>  | IEC1<8>      | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>  | IEC1<9>      | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10> | IEC1<10>     | IPC6<10:8>  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11> | IEC1<11>     | IPC6<14:12> |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12> | IEC1<12>     | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13> | IEC1<13>     | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14> | IEC1<14>     | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15> | IEC1<15>     | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>  | IEC2<0>      | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>  | IEC2<1>      | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>  | IEC2<2>      | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>  | IEC2<3>      | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>  | IEC2<4>      | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>  | IEC2<5>      | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>  | IEC2<6>      | IPC9<10:8>  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | —        | —            | —           |

| SI2C2 – I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8> |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 |          | _            |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

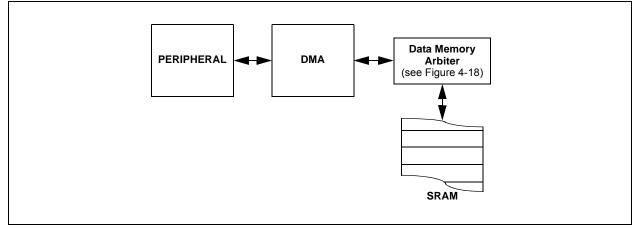

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

# FIGURE 8-1: DMA CONTROLLER MODULE

| REGISTE       | R 16-7: PWMC                                                                              | CONX: PWMX (                                                                                                                                | CONTROL R      | EGISTER          |                      |                      |                     |  |  |

|---------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|--|--|

| HS/HC-        | 0 HS/HC-0                                                                                 | HS/HC-0                                                                                                                                     | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>                                                                | TRGSTAT                                                                                                                                     | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |

| bit 15        | ·                                                                                         | •                                                                                                                                           |                | ÷                |                      |                      | bit                 |  |  |

| R/W-0         | R/W-0                                                                                     | R/W-0                                                                                                                                       | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |

| DTC1          |                                                                                           | DTCP <sup>(3)</sup>                                                                                                                         | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |

| bit 7         | DICO                                                                                      |                                                                                                                                             |                |                  |                      |                      |                     |  |  |

|               |                                                                                           |                                                                                                                                             |                |                  |                      |                      | bit                 |  |  |

| Legend:       |                                                                                           | HC = Hardware                                                                                                                               | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |  |  |

| R = Reada     | able bit                                                                                  | W = Writable bi                                                                                                                             | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |

| -n = Value    | at POR                                                                                    | '1' = Bit is set                                                                                                                            |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |

| bit 15        | ELTSTAT: ES                                                                               | ult Interrupt Statu                                                                                                                         | is hit(1)      |                  |                      |                      |                     |  |  |

| DIL 15        |                                                                                           | rrupt is pending                                                                                                                            |                |                  |                      |                      |                     |  |  |

|               |                                                                                           | interrupt is pendi                                                                                                                          | ng             |                  |                      |                      |                     |  |  |

|               |                                                                                           | ared by setting F                                                                                                                           |                |                  |                      |                      |                     |  |  |

| bit 14        |                                                                                           | rent-Limit Interru                                                                                                                          | •              |                  |                      |                      |                     |  |  |

|               |                                                                                           | 1 = Current-limit interrupt is pending<br>0 = No current-limit interrupt is pending                                                         |                |                  |                      |                      |                     |  |  |

|               |                                                                                           |                                                                                                                                             |                |                  |                      |                      |                     |  |  |

| bit 13        | This bit is cleared by setting CLIEN = 0.<br><b>TRGSTAT:</b> Trigger Interrupt Status bit |                                                                                                                                             |                |                  |                      |                      |                     |  |  |

|               | 1 = Trigger interrupt is pending                                                          |                                                                                                                                             |                |                  |                      |                      |                     |  |  |

|               |                                                                                           | r interrupt is pen                                                                                                                          |                |                  |                      |                      |                     |  |  |

|               |                                                                                           | ared by setting T                                                                                                                           |                |                  |                      |                      |                     |  |  |

| bit 12        |                                                                                           | t Interrupt Enable                                                                                                                          | e bit          |                  |                      |                      |                     |  |  |

|               |                                                                                           | rrupt is enabled rrupt is disabled                                                                                                          | and the FLTS   | TAT bit is clear | ed                   |                      |                     |  |  |

| bit 11        |                                                                                           | ent-Limit Interrup                                                                                                                          |                |                  | cu .                 |                      |                     |  |  |

|               |                                                                                           | mit interrupt is er                                                                                                                         |                |                  |                      |                      |                     |  |  |

|               |                                                                                           | mit interrupt is di                                                                                                                         |                | e CLSTAT bit is  | s cleared            |                      |                     |  |  |

| bit 10        | TRGIEN: Trig                                                                              | ger Interrupt En                                                                                                                            | able bit       |                  |                      |                      |                     |  |  |

|               |                                                                                           | event generates                                                                                                                             |                |                  | T hit is cleared     |                      |                     |  |  |

| bit 9         |                                                                                           | vent interrupts ar<br>dent Time Base I                                                                                                      |                |                  | i bit is cleared     |                      |                     |  |  |

| DIL 9         |                                                                                           | register provides                                                                                                                           |                | riad for this PM | VM generator         |                      |                     |  |  |

|               |                                                                                           | egister provides f                                                                                                                          | •              |                  | •                    |                      |                     |  |  |

| bit 8         |                                                                                           | er Duty Cycle Re                                                                                                                            |                |                  |                      |                      |                     |  |  |

|               |                                                                                           | ister provides du<br>jister provides du                                                                                                     |                |                  |                      | r                    |                     |  |  |

| Note 1:       | Software must clea                                                                        |                                                                                                                                             |                |                  | -                    |                      | t controller        |  |  |

| Note 1.<br>2: |                                                                                           | -                                                                                                                                           |                | -                | -                    | the interrup         |                     |  |  |

| 3:            |                                                                                           | nese bits should not be changed after the PWMx is enabled (PTEN = 1).<br>TC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored. |                |                  |                      |                      |                     |  |  |

| 4:            | The Independent T<br>CAM bit is ignored                                                   | Time Base (ITB =                                                                                                                            |                | •                |                      | igned mode. If       | TTB = 0, the        |  |  |

| 5:            | To operate in Exter                                                                       |                                                                                                                                             | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |  |  |

# REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                     | U-0                            | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |

|-------------------------|--------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|

| _                       | _                              |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |

| bit 15                  | <b>I</b>                       | •                                  |         |                  |                 |                 | bit 8   |

|                         |                                |                                    |         |                  |                 |                 |         |

| U-0                     | R-1                            | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |

| _                       | ICODE6                         | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |

| bit 7                   |                                |                                    |         |                  |                 |                 | bit     |

| Logondi                 |                                |                                    |         |                  |                 |                 |         |

| Legend:<br>R = Readable | - hit                          |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |

| -n = Value at           |                                | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |

| -n = value at           | POR                            | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |

| bit 15-13               | Unimplemen                     | ted: Read as '                     | 0'      |                  |                 |                 |         |

| bit 12-8                | =                              | Filter Hit Num                     |         |                  |                 |                 |         |

|                         |                                | 1 = Reserved                       |         |                  |                 |                 |         |

|                         | 01111 <b>= Filte</b>           | r 15                               |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         |                                | - 1                                |         |                  |                 |                 |         |

|                         | 00001 = Filte<br>00000 = Filte |                                    |         |                  |                 |                 |         |

| bit 7                   |                                | ted: Read as '                     | 0'      |                  |                 |                 |         |

| bit 6-0                 | -                              | Interrupt Flag                     |         |                  |                 |                 |         |

|                         |                                | 11111 = Rese                       |         |                  |                 |                 |         |

|                         |                                | IFO almost full                    |         |                  |                 |                 |         |

|                         |                                | eceiver overflo                    |         |                  |                 |                 |         |

|                         | 1000010 = K<br>1000001 = E     | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |

|                         | 1000000 = N                    |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         |                                | 11111 = Rese                       |         |                  |                 |                 |         |

|                         | •                              | B15 buffer inte                    | inupt   |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | •                              |                                    |         |                  |                 |                 |         |

|                         | 0001001 <b>= R</b>             | B9 buffer inter                    | rupt    |                  |                 |                 |         |

|                         |                                | B8 buffer inter                    |         |                  |                 |                 |         |

|                         |                                | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |

|                         |                                | RB5 buffer inte                    |         |                  |                 |                 |         |

|                         |                                | RB4 buffer inte                    |         |                  |                 |                 |         |

|                         | 0000011 <b>= T</b>             | RB3 buffer inte                    | errupt  |                  |                 |                 |         |

|                         |                                |                                    |         |                  |                 |                 |         |

|                         |                                | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

#### 22.2 **CTMU Control Registers**

| REGISTER                                                                                                                                                            | 22-1: CTM  | UCON1: CTM                                  | J CONTROI | - REGISTER       | 1                |                        |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|-----------|------------------|------------------|------------------------|--------|

| R/W-0                                                                                                                                                               | U-0        | R/W-0                                       | R/W-0     | R/W-0            | R/W-0            | R/W-0                  | R/W-0  |

| CTMUEN                                                                                                                                                              | _          | CTMUSIDL                                    | TGEN      | EDGEN            | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |

| bit 15                                                                                                                                                              |            |                                             |           |                  |                  |                        | bit 8  |

|                                                                                                                                                                     |            |                                             |           |                  |                  |                        |        |

| U-0                                                                                                                                                                 | U-0        | U-0                                         | U-0       | U-0              | U-0              | U-0                    | U-0    |

|                                                                                                                                                                     | _          |                                             | _         | <u> </u>         | <u> </u>         |                        | _      |

| bit 7                                                                                                                                                               |            |                                             |           |                  |                  |                        | bit 0  |

|                                                                                                                                                                     |            |                                             |           |                  |                  |                        |        |

| Legend:                                                                                                                                                             |            |                                             |           |                  |                  |                        |        |

| R = Readable                                                                                                                                                        | e bit      | W = Writable b                              | bit       | U = Unimplen     | nented bit, read | as '0'                 |        |

| -n = Value at                                                                                                                                                       | POR        | '1' = Bit is set                            |           | '0' = Bit is cle | own              |                        |        |

| bit 15                                                                                                                                                              |            | TMU Enable bit<br>is enabled<br>is disabled |           |                  |                  |                        |        |

| bit 14                                                                                                                                                              | Unimpleme  | nted: Read as '0                            | ,         |                  |                  |                        |        |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |            |                                             |           |                  |                  |                        |        |

| bit 12                                                                                                                                                              | TGEN: Time | Generation Ena                              | ble bit   |                  |                  |                        |        |

#### DECISTED

| bit 9 | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul> |

| bit 8 | CTTRIG: ADC Trigger Control bit                                                                                         |

|       | <ul><li>1 = CTMU triggers ADC start of conversion</li><li>0 = CTMU does not trigger ADC start of conversion</li></ul>   |

EDGSEQEN: Edge Sequence Enable bit

0 = No edge sequence is needed

1 = Enables edge delay generation 0 = Disables edge delay generation

EDGEN: Edge Enable bit

bit 7-0 Unimplemented: Read as '0'

bit 11

bit 10

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.) 0 = Software is used to trigger edges (manual set of EDGxSTAT)

1 = Edge 1 event must occur before Edge 2 event can occur

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                                                                                                     | U-0                                    | R/W-0                        | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|

| CH0NB      | _                                                                                                                       | _                                      | CH0SB4 <sup>(1)</sup>        | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |

| bit 15     | •                                                                                                                       |                                        |                              | •                     |                          |                       | bit 8                 |  |  |

|            |                                                                                                                         |                                        |                              |                       |                          |                       |                       |  |  |

| R/W-0      | U-0                                                                                                                     | U-0                                    | R/W-0                        | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |

| CH0NA      |                                                                                                                         |                                        | CH0SA4 <sup>(1)</sup>        | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |

| bit 7      |                                                                                                                         |                                        |                              |                       |                          |                       | bit (                 |  |  |

|            |                                                                                                                         |                                        |                              |                       |                          |                       |                       |  |  |

| Legend:    |                                                                                                                         |                                        |                              |                       |                          |                       |                       |  |  |

| R = Read   |                                                                                                                         | W = Writable                           |                              | •                     | nented bit, read         |                       |                       |  |  |

| -n = Value | e at POR                                                                                                                | '1' = Bit is set                       |                              | '0' = Bit is cle      | ared                     | x = Bit is unkr       | iown                  |  |  |

| bit 15     |                                                                                                                         | nannel 0 Negative                      | Input Soloot fo              | r Samala MUV          | 'D hit                   |                       |                       |  |  |

| DIL 15     |                                                                                                                         | el 0 negative input                    |                              |                       |                          |                       |                       |  |  |

|            |                                                                                                                         | el 0 negative input                    |                              |                       |                          |                       |                       |  |  |

| bit 14-13  | Unimplem                                                                                                                | ented: Read as 'o                      | )'                           |                       |                          |                       |                       |  |  |

| bit 12-8   | CH0SB<4:                                                                                                                | 0>: Channel 0 Po                       | sitive Input Sele            | ect for Sample        | MUXB bits <sup>(1)</sup> |                       |                       |  |  |

|            |                                                                                                                         | pen; use this sele                     |                              |                       |                          | ement                 |                       |  |  |

|            | 11110 <b>= C</b>                                                                                                        | nannel 0 positive in                   | put is connected             | to the CTMU te        | emperature mea           | surement diode        | (CTMU TEMF            |  |  |

|            | 11101 <b>=</b> R                                                                                                        |                                        |                              |                       |                          |                       |                       |  |  |

|            | 11100 = R<br>11011 = R                                                                                                  |                                        |                              |                       |                          |                       |                       |  |  |

|            |                                                                                                                         | hannel 0 positive                      | input is the outr            | out of OA3/AN6        | <sub>)</sub> (2,3)       |                       |                       |  |  |

|            |                                                                                                                         | hannel 0 positive                      |                              |                       |                          |                       |                       |  |  |

|            | 11000 <b>= C</b>                                                                                                        | hannel 0 positive                      | input is the outp            | out of OA1/AN3        | <sub>3</sub> (2)         |                       |                       |  |  |

|            | 10111 <b>= R</b>                                                                                                        | eserved                                |                              |                       |                          |                       |                       |  |  |

|            | •                                                                                                                       |                                        |                              |                       |                          |                       |                       |  |  |

|            | •                                                                                                                       |                                        |                              |                       |                          |                       |                       |  |  |

|            | 10000 <b>= R</b>                                                                                                        | eserved                                |                              |                       |                          |                       |                       |  |  |

|            | 01111 <b>= C</b>                                                                                                        | hannel 0 positive                      | input is AN15 <sup>(3)</sup> |                       |                          |                       |                       |  |  |

|            | 01110 = C                                                                                                               | hannel 0 positive                      | input is AN14 <sup>(3)</sup> |                       |                          |                       |                       |  |  |

|            | 01101 = C                                                                                                               | hannel 0 positive                      | Input is AN130               |                       |                          |                       |                       |  |  |

|            | •                                                                                                                       |                                        |                              |                       |                          |                       |                       |  |  |

|            | •                                                                                                                       |                                        |                              |                       |                          |                       |                       |  |  |

|            | 00010 <b>= C</b>                                                                                                        | hannel 0 positive                      | input is AN2 <sup>(3)</sup>  |                       |                          |                       |                       |  |  |

|            |                                                                                                                         | hannel 0 positive<br>hannel 0 positive |                              |                       |                          |                       |                       |  |  |

| L:1 7      |                                                                                                                         | •                                      | •                            |                       | A 64                     |                       |                       |  |  |

| bit 7      | <b>CH0NA:</b> Channel 0 Negative Input Select for Sample MUXA bit<br>1 = Channel 0 negative input is AN1 <sup>(1)</sup> |                                        |                              |                       |                          |                       |                       |  |  |

|            |                                                                                                                         | el 0 negative input                    |                              |                       |                          |                       |                       |  |  |

| bit 6-5    |                                                                                                                         | ented: Read as '                       |                              |                       |                          |                       |                       |  |  |

| Note 1:    | to determine I                                                                                                          | AN7 are repurpos<br>now enabling a pa  |                              |                       |                          |                       |                       |  |  |

| -          | and 3.                                                                                                                  |                                        |                              |                       |                          |                       | - >                   |  |  |

| 2:         |                                                                                                                         | t is used if the co                    |                              | amp is selecte        | d (OPMODE (C             | MxCON<10>) :          | = 1);                 |  |  |

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                             | R/W-0                                                                                       | R/W-0                                         | R/W-0            | R/W-0           | R/W-0   |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|-----------------|---------|--|

| PTGCLK2         | PTGCLK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PTGCLK0                                                                           | PTGDIV4                                                                                     | PTGDIV3                                       | PTGDIV2          | PTGDIV1         | PTGDIV0 |  |

| bit 15          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                 | 1                                                                                           |                                               | 1                |                 | bit     |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                             | R/W-0                                                                                       | U-0                                           | R/W-0            | R/W-0           | R/W-0   |  |

| PTGPWD3         | PTGPWD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PTGPWD1                                                                           | PTGPWD0                                                                                     | _                                             | PTGWDT2          | PTGWDT1         | PTGWDTC |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |                                                                                             |                                               |                  |                 | bit     |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |                                                                                             |                                               |                  |                 |         |  |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W = Writable                                                                      | bit                                                                                         | U = Unimpler                                  | mented bit, read | l as '0'        |         |  |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                  |                                                                                             | '0' = Bit is cle                              | ared             | x = Bit is unkr | nown    |  |

| bit 15-13       | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc | SCLK<br>SCLK<br>CLK<br>D<br>DSC               |                  |                 |         |  |

| bit 12-8        | <pre>PTGDIV&lt;4:0&gt;: PTG Module Clock Prescaler (divider) bits 11111 = Divide-by-32 11110 = Divide-by-31</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |                                                                                             |                                               |                  |                 |         |  |

| bit 7-4         | PTGPWD<3:0<br>1111 = All trig<br>1110 = All trig<br>0001 = All trig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>D&gt;:</b> PTG Trigge<br>gger outputs ar<br>gger outputs ar<br>gger outputs ar | e 16 PTG cloc<br>e 15 PTG cloc<br>e 2 PTG clock                                             | k cycles wide<br>k cycles wide<br>cycles wide |                  |                 |         |  |

| bit 3           | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as '                                                                    | 0'                                                                                          |                                               |                  |                 |         |  |

| bit 2-0         | Unimplemented: Read as '0'<br>PTGWDT<2:0>: Select PTG Watchdog Timer Time-out Count Value bits<br>111 = Watchdog Timer will time-out after 512 PTG clocks<br>110 = Watchdog Timer will time-out after 256 PTG clocks<br>101 = Watchdog Timer will time-out after 128 PTG clocks<br>100 = Watchdog Timer will time-out after 64 PTG clocks<br>011 = Watchdog Timer will time-out after 32 PTG clocks<br>010 = Watchdog Timer will time-out after 16 PTG clocks<br>010 = Watchdog Timer will time-out after 8 PTG clocks<br>001 = Watchdog Timer will time-out after 8 PTG clocks<br>000 = Watchdog Timer is disabled |                                                                                   |                                                                                             |                                               |                  |                 |         |  |

# REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

| <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |