Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp502-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   |                                | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

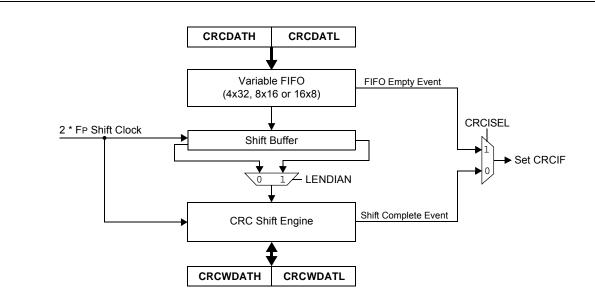

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

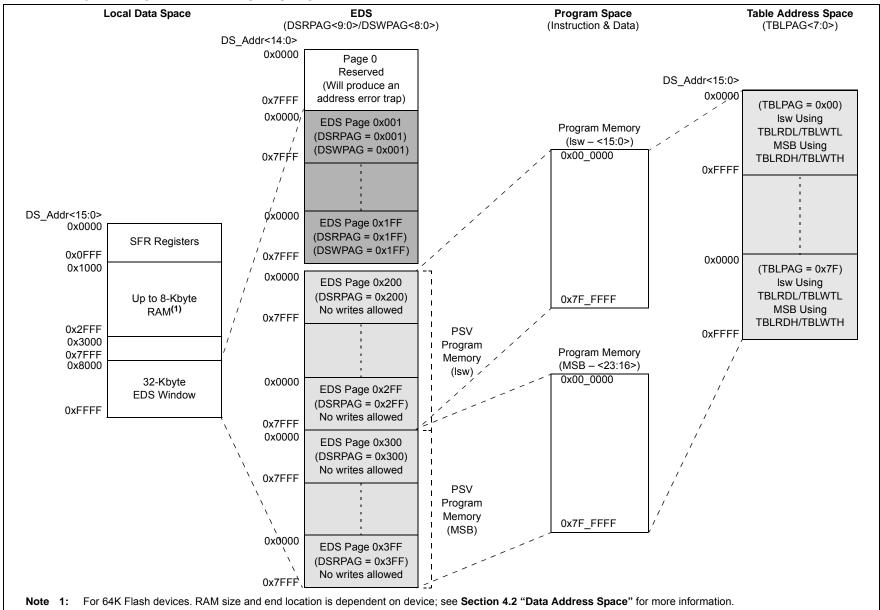

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1        | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|--------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF        | <b>INT0IF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF      | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |        | _          | _      |       | IC4IF  | IC3IF       | DMA3IF | _      | —        | SPI2IF       | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF | PSEMIF     | _      | _     | _      | _           | _      | _      | MI2C2IF  | SI2C2IF      | —             | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |        | —          | _      | _     |        | _           | _      | CRCIF  | U2EIF    | U1EIF        |               | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            |               | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | _             | 0000          |

| IFS9         | 0812  | _      | _      | _          |        | _      | _      | _          | —      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF    |               | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE        | INTOIE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | —     | _      | —           | INT1IE | CNIE   | CMIE     | MI2C1IE      | SI2C1IE       | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |        | —          | —      | _     | IC4IE  | IC3IE       | DMA3IE |        | _        | SPI2IE       | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | _          |        | _      | QEI1IE | PSEMIE     | —      | _     | _      | —           | —      | -      | MI2C2IE  | SI2C2IE      | —             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     |        | _      |        | —          | —      | _     | _      | —           | _      | CRCIE  | U2EIE    | U1EIE        |               | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          |        | _      | _      | _          | —      | _     | _      | —           | _      |        | _        | —            |               | 0000          |

| IEC6         | 082C  | _      | _      | _          |        | _      |        | _          | —      | _     | _      | —           | _      | -      | _        | _            | PWM3IE        | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          |        | _      |        | _          | —      | _     | _      | —           | _      | -      | _        | _            | —             | 0000          |

| IEC9         | 0832  | _      | _      | _          |        | _      |        | _          | —      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE    |               | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | )>     | _     |        | IC1IP<2:0>  |        |        |          | INT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | )>     | _     |        | IC2IP<2:0>  |        | -      | [        | DMA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | -      |          | T3IP<2:0>    |               | 4444          |

| IPC3         | 0846  | _      | _      | —          | —      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | -      |          | U1TXIP<2:0>  |               | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |        | MI2C1IP<2:0 | >      | -      | 5        | SI2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  | _      | _      | —          | —      | _      |        | —          | —      | _     | _      | —           | —      | -      |          | INT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | )>     |       |        | OC3IP<2:0>  |        |        | [        | DMA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | 0>     |       |        | INT2IP<2:0> | •      |        |          | T5IP<2:0>    |               | 4444          |

| IPC8         | 0850  | _      | _      | —          | —      | _      |        | —          | —      | _     |        | SPI2IP<2:0> | •      | -      | 5        | SPI2EIP<2:0> |               | 0044          |

| IPC9         | 0852  | _      | _      | _          | -      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | -      | [        | DMA3IP<2:0>  |               | 0444          |

| IPC12        | 0858  | _      | _      | _          | -      | _      | N      | 112C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | -      | _        | —            |               | 0440          |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:0 | )>     | _     |        | PSEMIP<2:0  | >      | _      | _        | _            | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _            | _             | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —      | —          | _      | _     |        | CTMUIP<2:0  | >      | _      | _        | _            | _             | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P      | WM1IP<2:   | 0>     | _     | _      | _           | —      | _      | _        | _            | _             | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |        | _          |        |       | _      | _           | _      | _      | F        | PWM3IP<2:0>  |               | 4004          |

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST                                                          |        | FOR as | PIC33EP  | ATOR 2 REGISTER MAP FOR OSPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |          |          |         |         |          |          |         |         |               |

|-----------|-------|----------|--------|---------|----------------------------------------------------------------|--------|--------|----------|--------------------------------------------------------------------------------|----------|----------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12                                                         | Bit 11 | Bit 10 | Bit 9    | Bit 8                                                                          | Bit 7    | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN                                                         | CLIEN  | TRGIEN | ITB      | MDCS                                                                           | DTC      | <1:0>    | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL                                                           | PMOD   | 0<1:0> | OVRENH   | OVRENL                                                                         | OVRDA    | \T<1:0>  | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0                                                      | )>     |        | CLPOL    | CLMOD                                                                          |          | FLT      | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |         |                                                                |        |        |          |                                                                                |          |          |         |         |          |          | 0000    |         |               |

| PHASE2    | 0C48  |          |        |         |                                                                |        |        |          |                                                                                |          |          |         |         |          | 0000     |         |         |               |

| DTR2      | 0C4A  | _        | _      |         |                                                                |        |        |          |                                                                                |          |          |         |         | 0000     |          |         |         |               |

| ALTDTR2   | 0C4C  | _        | _      |         |                                                                |        |        |          | AL                                                                             | TDTR2<13 | :0>      |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |         |                                                                |        |        | TI       | RGCMP<15:0                                                                     | )>       |          |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |                                                                | _      | —      | _        | _                                                                              | _        | -        |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLR PLF FLTLEBEN CLLEBEN — — — — BCH BCL BPHH BPHL BPLH BPLL ( |        |        |          |                                                                                |          |          |         |         | 0000     |          |         |         |               |

| LEBDLY2   | 0C5C  | _        | _      | _       | _                                                              |        |        |          |                                                                                |          | LEB<11:0 | )>      |         |          |          |         |         | 0000          |

| AUXCON2   | 0C5E  | _        | _      | —       | —                                                              |        | BLANK  | SEL<3:0> |                                                                                | _        | —        |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12    | Bit 11                                             | Bit 10         | Bit 9    | Bit 8     | Bit 7     | Bit 6    | Bit 5 | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------|---------|-----------|----------------------------------------------------|----------------|----------|-----------|-----------|----------|-------|---------|----------|----------|---------|---------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN    | CLIEN                                              | TRGIEN         | ITB      | MDCS      | DTC<      | <1:0>    | DTCP  | —       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL      | PMOD                                               | )<1:0>         | OVRENH   | OVRENL    | OVRDA     | T<1:0>   | FLTD  | AT<1:0> | CLD      | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON3   | 0C64  |         |        | C       | CLSRC<4:0 | )>                                                 |                |          |           |           |          |       |         | FLTMO    | D<1:0>   | 00F8    |         |               |

| PDC3      | 0C66  |         |        |         |           |                                                    | PDC3<15:0>     |          |           |           |          |       |         | 0000     |          |         |         |               |

| PHASE3    | 0C68  |         |        |         |           |                                                    | PHASE3<15:0> 0 |          |           |           |          |       |         | 0000     |          |         |         |               |

| DTR3      | 0C6A  |         | —      |         |           |                                                    |                |          | [         | DTR3<13:0 | >        |       |         |          |          |         |         | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |           |                                                    |                |          | AL        | TDTR3<13  | :0>      |       |         |          |          |         |         | 0000          |

| TRIG3     | 0C72  |         |        |         |           |                                                    |                | Т        | RGCMP<15: | 0>        |          |       |         |          |          |         |         | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |           | _                                                  | _              | _        | _         | _         | _        |       |         | TR       | GSTRT<5: | 0>      |         | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF       | FLTLEBEN CLLEBEN — — — BCH BCL BPHH BPHL BPLH BPLL |                |          |           |           |          |       | 0000    |          |          |         |         |               |

| LEBDLY3   | 0C7C  |         | —      | _       | _         |                                                    |                |          |           |           | LEB<11:0 | )>    |         |          |          |         |         | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | —         |                                                    | BLANK          | SEL<3:0> |           |           | —        |       | CHOPS   | SEL<3:0> | •        | CHOPHEN | CHOPLEN | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | _     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      |        | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | _      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0          | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0     |

|----------------------|--------------|---------------------------------|-----------------------|------------------|------------------|-----------------|---------|

| FORCE <sup>(1)</sup> |              | _                               | _                     | —                |                  | _               |         |

| bit 15               |              |                                 |                       |                  |                  |                 | bit 8   |

|                      |              |                                 |                       |                  |                  |                 |         |

| R/W-0                | R/W-0        | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IRQSEL7              | IRQSEL6      | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |

| bit 7                |              |                                 |                       |                  |                  |                 | bit     |

| Legend:              |              | S = Settable b                  | oit                   |                  |                  |                 |         |

| R = Readable         | bit          | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at F      | POR          | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                      |              |                                 |                       |                  |                  |                 |         |

| bit 15               | FORCE: Force | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |         |

|                      | 1 = Forces a | single DMA tra                  | insfer (Manua         | l mode)          |                  |                 |         |

|                      | 0 = Automati | c DMA transfer                  | initiation by D       | DMA request      |                  |                 |         |

| bit 14-8             | Unimplemen   | ted: Read as 'd                 | )'                    |                  |                  |                 |         |

| bit 7-0              | IRQSEL<7:0>  | -: DMA Periphe                  | eral IRQ Num          | ber Select bits  |                  |                 |         |

|                      |              | ECAN1 – TX D                    |                       | 2)               |                  |                 |         |

|                      |              | IC4 – Input Ca                  |                       |                  |                  |                 |         |

|                      |              | IC3 – Input Ca                  |                       |                  |                  |                 |         |

|                      |              | ECAN1 – RX D<br>SPI2 Transfer I | -                     |                  |                  |                 |         |

|                      |              | UART2TX – UA                    |                       | itter            |                  |                 |         |

|                      |              | UART2RX – U                     |                       |                  |                  |                 |         |

|                      |              | TMR5 – Timer5                   |                       |                  |                  |                 |         |

|                      | 00011011 =   | TMR4 – Timer4                   | 1                     |                  |                  |                 |         |

|                      |              | OC4 – Output (                  |                       |                  |                  |                 |         |

|                      |              | OC3 – Output (                  |                       |                  |                  |                 |         |

|                      |              | ADC1 – ADC1                     |                       |                  |                  |                 |         |

|                      |              | UART1TX – UA                    |                       |                  |                  |                 |         |

|                      |              | UART1RX – U/<br>SPI1 – Transfe  |                       | er               |                  |                 |         |

|                      |              | TMR3 – Timer3                   |                       |                  |                  |                 |         |

|                      |              | TMR2 – Timer2                   |                       |                  |                  |                 |         |

|                      |              | OC2 – Output (                  |                       |                  |                  |                 |         |

|                      |              | IC2 – Input Ca                  |                       |                  |                  |                 |         |

|                      | 00000010 =   | OC1 – Output (                  | Compare 1             |                  |                  |                 |         |

|                      |              | IC1 – Input Ca                  |                       |                  |                  |                 |         |

|                      | 00000000 =   | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |         |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -            | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15       |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7        |                             |                                              |                |                  |                  |                 | bit 0 |

| Legend:      |                             |                                              |                |                  |                  |                 |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                             |                                              |                |                  |                  |                 |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|              |                             | data transfer wa                             |                |                  |                  |                 |       |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0          | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| 0-0          | 0-0   | 0-0   | 0-0   | 0-0   | 0-0   | 0-0   | 0-0   |  |

|              | —     |       | _     | _     | —     | —     |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

|              |       |       |       |       |       |       |       |  |

| U-0          | R/W-0 |  |

| — U2RXR<6:0> |       |       |       |       |       |       |       |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |

|              |       |       |       |       |       |       |       |  |

| Legend:      |       |       |       |       |       |       |       |  |

|              |       |       |       |       |       |       |       |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

## 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                              | R/W-0                                                                                                          | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                | QEISIDL                                                                                                        | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                                          | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       111 = Reserved       112 = Rise index input event mees the position counter         11 = First index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event mees the position counter         10 = Next ind                                                                                                                                                   | bit 15       |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 8               |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       111 = Reserved       112 = Rise index input event mees the position counter         11 = First index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event mees the position counter         10 = Next ind                                                                                                                                                   |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                  |                                                                                                                |                                                                                              | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                         | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                                         | GATEN                                                      | CCM1                              |                     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 0               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |