Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp502t-i-mm |

# **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

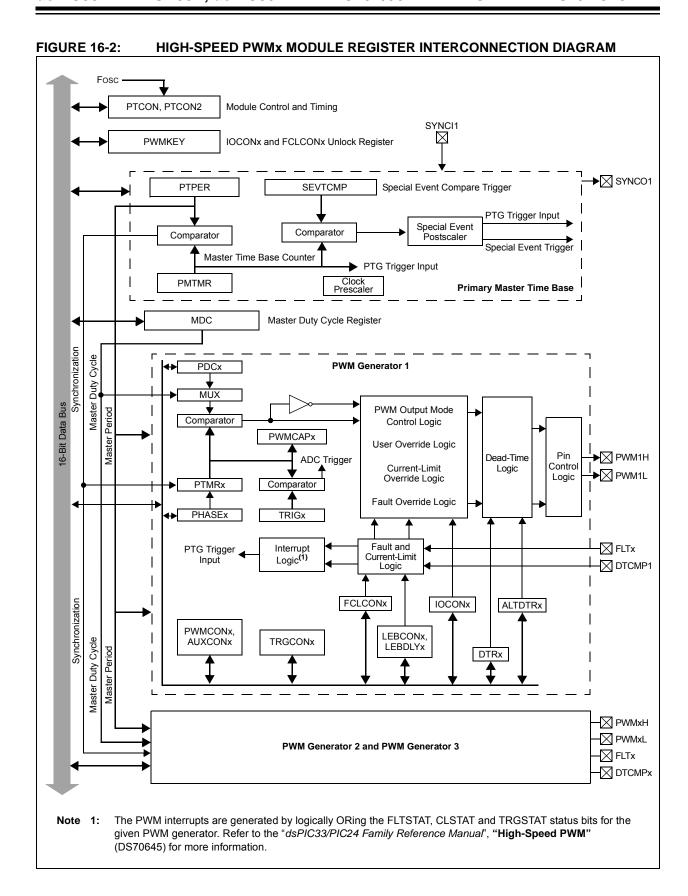

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

**TABLE 4-4:** INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6             | Bit 5        | Bit 4  | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|-------------------|--------------|--------|--------|----------|--------------|---------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF             | IC2IF        | DMA0IF | T1IF   | OC1IF    | IC1IF        | INT0IF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _                 | _            | INT1IF | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IF             | IC3IF        | DMA3IF | _      | _        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | -      | -      | QEI1IF | PSEMIF     | _      | _     | -                 | ı            | _      | ı      | MI2C2IF  | SI2C2IF      | -       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | -      | -      | _      | -          | _      | _     | -                 | ı            | _      | CRCIF  | U2EIF    | U1EIF        | -       | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | -      | -      | _      | -          | _      | _     | -                 | ı            | _      | 1      | _        | _            | -       | 0000          |

| IFS6         | 080C  | _      | -      | _          | -      |        | _      | -          | _      | _     | _                 | 1            | _      | ı      | _        | _            | PWM3IF  | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | -      | -      | _      | -          | _      | _     | -                 | ı            | _      | 1      | _        | _            | -       | 0000          |

| IFS9         | 0812  | _      |        | _          | -      | -      | _      | -          | _      | _     | PTG3IF            | PTG2IF       | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF    | -       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE             | IC2IE        | DMA0IE | T1IE   | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | -                 | ı            | INT1IE | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      |        | _          | -      |        | _      | -          | _      | _     | IC4IE             | IC3IE        | DMA3IE | 1      | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      |        | _          | -      |        | QEI1IE | PSEMIE     | _      | _     | -                 | ı            | _      | 1      | MI2C2IE  | SI2C2IE      | -       | 0000          |

| IEC4         | 0828  | _      |        | CTMUIE     | -      |        | _      | -          | _      | _     | -                 | ı            | _      | CRCIE  | U2EIE    | U1EIE        | -       | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | -      |        | _      | -          | _      | _     | -                 | ı            | _      | 1      | _        | _            | -       | 0000          |

| IEC6         | 082C  | _      |        | _          | -      |        | _      | -          | _      | _     | -                 | ı            | _      | 1      | _        | _            | PWM3IE  | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | -      |        | _      | -          | _      | _     | _                 | 1            | _      | ı      | _        | _            |         | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | _          | _      | _     | PTG3IE            | PTG2IE       | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | >      | _     |                   | IC1IP<2:0>   |        | _      |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | >      | _     |                   | IC2IP<2:0>   |        | _      | I        | DMA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | l      | U1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |                   | SPI1EIP<2:0  | >      | _      |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      |        | MA1IP<2:   | 0>     | _     |                   | AD1IP<2:0>   | •      | _      |          | U1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  | •      | _      |        | CMIP<2:0   | >      | _     | I                 | MI2C1IP<2:0  | >      | _      | ;        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _                 | _            | _      | _      |          | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | >      | _     |                   | OC3IP<2:0>   | •      | _      | I        | DMA2IP<2:0>  |         | 4444          |

| IPC7         | 084E  | _      | I      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | )>     | _     |                   | INT2IP<2:0>  | •      | _      |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  | _      |        | _          | -      | -      | _      | -          | _      | _     |                   | SPI2IP<2:0>  | •      | 1      |          | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  | _      |        | _          | -      | -      |        | IC4IP<2:0  | >      | _     |                   | IC3IP<2:0>   |        | 1      |          | DMA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | I.     | 112C2IP<2: | 0>     | _     |                   | SI2C2IP<2:0: | >      | _      | _        | _            | _       | 0440          |

| IPC14        | 085C  |        | _      |            |        |        | (      | QEI1IP<2:0 | )>     |       |                   | PSEMIP<2:0   | >      |        | _        |              |         | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      |        |        | U2EIP<2:0  | >      |       |                   | U1EIP<2:0>   | ,      |        | _        | _            |         | 4440          |

| IPC19        | 0866  | _      | _      | _          | _      | _      | _      | _          | _      | _     | CTMUIP<2:0> — — — |              | _      | 0040   |          |              |         |               |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | Р      | WM1IP<2:   | 0>     | _     | _                 | _            | _      | _      | _        | _            | _       | 4400          |

| IPC24        | 0870  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _                 | _            | _      | _      | F        | PWM3IP<2:0>  |         | 4004          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8      | Bit 7                         | Bit 6    | Bit 5  | Bit 4 | Bit 3      | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|------------|---------------|--------|-----------|--------|--------|--------|--------|----------|------------|-------------------------------|----------|--------|-------|------------|--------|--------|--------|---------------|

|            | 0400-<br>041E |        |           |        |        |        |        |          | See defini | tion when W                   | IN = x   |        |       |            |        |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF      | P<3:0> |        |        | F2BI   | P<3:0>   |            |                               | F1BP     | <3:0>  |       |            | F0BP   | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF      | P<3:0> |        |        | F6BI   | P<3:0>   |            |                               | F5BP     | <3:0>  |       |            | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B      | P<3:0> |        |        | F10B   | P<3:0>   |            |                               | F9BP     | <3:0>  |       | F8BP<3:0>  |        |        |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B      | P<3:0> |        |        | F14B   | P<3:0>   |            |                               | F13BF    | °<3:0> |       | F12BP<3:0> |        |        |        | 0000          |

| C1RXM0SID  | 0430          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | MIDE       | _      | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       | 7:0>   |        |        |               |

| C1RXM1SID  | 0434          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | MIDE       | _      | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | )<7:0>     |        |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | MIDE       | _      | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF0SID  | 0440          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF1SID  | 0444          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |        | EID<15:8> |        |        |        |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF2SID  | 0448          |        | SID<10:3> |        |        |        |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |           |        | EID<   | :15:8> |        |          |            | EID<7:0>                      |          |        |       |            |        |        |        | xxxx          |

| C1RXF4SID  | 0450          |        |           |        | SID<   | :10:3> |        |          |            | SID<2:0> — EXIDE —            |          |        |       |            | EID<   | 17:16> | xxxx   |               |

| C1RXF4EID  | 0452          |        |           |        | EID<   | :15:8> |        |          |            | EID<7:0>                      |          |        |       |            |        |        | xxxx   |               |

| C1RXF5SID  | 0454          |        |           |        | SID<   | :10:3> |        |          |            | SID<2:0> —                    |          |        |       | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |        | SID<10:3> |        |        |        |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        | EID<15:8> |        |        |        |        | EID<7:0> |            |                               |          |        |       | xxxx       |        |        |        |               |

| C1RXF9SID  | 0464          |        |           |        | SID<   | :10:3> |        |          |            | SID<2:0> — EXIDE — EID<17:    |          |        |       |            | 17:16> | xxxx   |        |               |

| C1RXF9EID  | 0466          |        |           |        | EID<   | :15:8> |        |          |            | EID<7:0>                      |          |        |       |            |        | xxxx   |        |               |

| C1RXF10SID | 0468          |        |           |        | SID<   | :10:3> |        |          |            | SID<2:0> — EXIDE — EID<17:16> |          |        |       |            | 17:16> | xxxx   |        |               |

| C1RXF10EID | 046A          |        |           |        | EID<   | :15:8> |        |          |            |                               |          |        | EID<  | 7:0>       |        | •      |        | xxxx          |

| C1RXF11SID | 046C          |        |           |        | SID<   | :10:3> |        |          |            |                               | SID<2:0> |        | _     | EXIDE      | _      | EID<   | 17:16> | xxxx          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY (CONTINUED)

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8 | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|--------|--------|----------|-------|-------------------------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| C1RXF11EID | 046E |           | EID<15:8> |        |        |        |        |          |       |                               |          | EID<  | 7:0>  |       |       |       | xxxx  |               |

| C1RXF12SID | 0470 |           |           |        | SID<   | 10:3>  |        |          |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472 |           | EID<15:8> |        |        |        |        |          |       | EID<7:0>                      |          |       |       |       |       |       |       | xxxx          |

| C1RXF13SID | 0474 |           |           |        | SID<   | 10:3>  |        |          |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476 |           |           |        | EID<   | 15:8>  |        |          |       | EID<7:0>                      |          |       |       |       |       | xxxx  |       |               |

| C1RXF14SID | 0478 |           |           |        | SID<   | 10:3>  |        |          |       |                               | SID<2:0> |       | _     | EXIDE | _     | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A |           | EID<15:8> |        |        |        |        |          |       |                               |          |       | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF15SID | 047C |           | SID<10:3> |        |        |        |        |          |       | SID<2:0> — EXIDE — EID<17:16> |          |       |       |       | 7:16> | xxxx  |       |               |

| C1RXF15EID | 047E | EID<15:8> |           |        |        |        |        | EID<7:0> |       |                               |          |       |       | xxxx  |       |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

bit 4 **Unimplemented:** Read as '0' bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

1 = FSCM has detected clock failure0 = FSCM has not detected clock failure

bit 2-1 Unimplemented: Read as '0'

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

Note: Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 30.0 "Electrical Characteristics"** for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

#### REGISTER 16-2: PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | -   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|-----|-----|-----|-----|-------------------------|-------------------------|-------------------------|

| _     | _   | _   | _   | _   | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0 <sup>(1)</sup> |

| bit 7 |     |     |     |     |                         |                         | bit 0                   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

111 = Reserved

110 = Divide-by-64

101 = Divide-by-32

100 = Divide-by-16

011 = Divide-by-8

010 = Divide-by-4

001 = Divide-by-2

000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# **REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | DTRx  | <13:8> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|--|

|       | DTRx<7:0>   |       |       |       |       |       |       |  |  |  |  |  |  |

| bit 7 | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|--------|-----|-------|-------|--------|----------|-------|-------|

| _      | _   |       |       | ALTDTI | Rx<13:8> |       |       |

| bit 15 |     |       |       |        |          |       | bit 8 |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|--|--|

|       | ALTDTRx<7:0> |       |       |       |       |       |       |  |  |  |  |  |  |  |

| bit 7 | bit 7 bit 0  |       |       |       |       |       |       |  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 17-4: POS1CNTH: POSITION COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|--|

|        | POSCNT<31:24> |       |       |       |       |       |       |  |  |  |  |  |  |

| bit 15 | bit 15 bit 8  |       |       |       |       |       |       |  |  |  |  |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSCNT<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 POSCNT<31:16>: High Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

## REGISTER 17-5: POS1CNTL: POSITION COUNTER 1 LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| POSCNT<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSCNT<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **POSCNT<15:0>:** Low Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

## REGISTER 17-6: POS1HLD: POSITION COUNTER 1 HOLD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSHLD<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSHLD<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **POSHLD<15:0>:** Hold Register for Reading and Writing POS1CNTH bits

## 18.1 SPI Helpful Tips

Note:

- In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on  $\overline{SSx}$ .

This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 30.0 "Electrical Characteristics" for details.

In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPIx data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 18.2.1 KEY RESOURCES

- "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC | R-0, HSC | U-0 | U-0 | U-0 | R/C-0, HS | R-0, HSC | R-0, HSC |

|----------|----------|-----|-----|-----|-----------|----------|----------|

| ACKSTAT  | TRSTAT   | _   | _   | _   | BCL       | GCSTAT   | ADD10    |

| bit 15   |          |     |     |     |           |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     |           |          |            |            |          |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         | HSC = Hardware Settable/Clearable bit |  |  |

|-------------------|-------------------|------------------------------------|---------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                                       |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown                    |  |  |

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C<sup>™</sup> master, applicable to master transmit operation)

- 1 = NACK received from slave

- 0 = ACK received from slave

Hardware is set or clear at the end of slave Acknowledge.

- bit 14 TRSTAT: Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No bus collision detected

Hardware is set at detection of a bus collision.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware is set when address matches general call address. Hardware is clear at Stop detection.

- bit 8 ADD10: 10-Bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop detection.

- bit 7 IWCOL: I2Cx Write Collision Detect bit

- 1 = An attempt to write to the I2CxTRN register failed because the I2C module is busy

- 0 = No collision

Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: I2Cx Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register was still holding the previous byte

- 0 = No overflow

Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was a device address

Hardware is clear at a device address match. Hardware is set by reception of a slave byte.

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware is set or clear when a Start, Repeated Start or Stop is detected.

#### REGISTER 21-3: **CXVEC: ECANX INTERRUPT CODE REGISTER**

| U-0    | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     | R-0     |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | _   | _   | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | R-1    | R-0    | R-0    | R-0    | R-0    | R-0    | R-0    |

|-------|--------|--------|--------|--------|--------|--------|--------|

| _     | ICODE6 | ICODE5 | ICODE4 | ICODE3 | ICODE2 | ICODE1 | ICODE0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 FILHIT<4:0>: Filter Hit Number bits

10000-11111 = Reserved

01111 = Filter 15

00001 = Filter 1

00000 = Filter 0

bit 7 Unimplemented: Read as '0'

bit 6-0 ICODE<6:0>: Interrupt Flag Code bits

1000101-1111111 = Reserved

1000100 = FIFO almost full interrupt

1000011 = Receiver overflow interrupt

1000010 = Wake-up interrupt

1000001 = Error interrupt

1000000 **= No interrupt**

0010000-0111111 = Reserved

0001111 = RB15 buffer interrupt

0001001 = RB9 buffer interrupt

0001000 = RB8 buffer interrupt

0000111 = TRB7 buffer interrupt

0000110 = TRB6 buffer interrupt

0000101 = TRB5 buffer interrupt

0000100 = TRB4 buffer interrupt

0000011 = TRB3 buffer interrupt

0000010 = TRB2 buffer interrupt

0000001 = TRB1 buffer interrupt

0000000 = TRB0 buffer interrupt

# REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                   | R/W-0 | R/W-0       | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|-------------------------|-------|-------------|-------|-------------|-------|-------|-------|

| F15MSK<1:0> F14MSK<1:0> |       | F13MSK<1:0> |       | F12MSK<1:0> |       |       |       |

| bit 15                  |       |             |       | •           |       | •     | bit 8 |

| R/W-0 | R/W-0  | R/W-0 | R/W-0       | R/W-0 | R/W-0      | R/W-0 | R/W-0  |

|-------|--------|-------|-------------|-------|------------|-------|--------|

| F11MS | K<1:0> | F10MS | F10MSK<1:0> |       | F9MSK<1:0> |       | K<1:0> |

| bit 7 |        |       |             |       |            |       | bit 0  |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | F15MSK<1:0>: Mask Source for Filter 15 bits  11 = Reserved  10 = Acceptance Mask 2 registers contain mask  01 = Acceptance Mask 1 registers contain mask  00 = Acceptance Mask 0 registers contain mask |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-12 | F14MSK<1:0>: Mask Source for Filter 14 bits (same values as bits<15:14>)                                                                                                                                |

| bit 11-10 | F13MSK<1:0>: Mask Source for Filter 13 bits (same values as bits<15:14>)                                                                                                                                |

| bit 9-8   | F12MSK<1:0>: Mask Source for Filter 12 bits (same values as bits<15:14>)                                                                                                                                |

| bit 7-6   | F11MSK<1:0>: Mask Source for Filter 11 bits (same values as bits<15:14>)                                                                                                                                |

| bit 5-4   | F10MSK<1:0>: Mask Source for Filter 10 bits (same values as bits<15:14>)                                                                                                                                |

| bit 3-2   | F9MSK<1:0>: Mask Source for Filter 9 bits (same values as bits<15:14>)                                                                                                                                  |

| bit 1-0   | F8MSK<1:0>: Mask Source for Filter 8 bits (same values as bits<15:14>)                                                                                                                                  |

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- · Four Edge Input Trigger Sources

- · Polarity Control for Each Edge Source

- · Control of Edge Sequence

- · Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUICON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/PIC24 Family Reference Manual".

#### 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

bit 1 C2OUT: Comparator 2 Output Status bit<sup>(2)</sup>

When CPOL = 0: 1 = VIN+ > VIN-0 = VIN+ < VIN-When CPOL = 1: 1 = VIN+ < VIN-0 = VIN+ > VIN-

bit 0 C10UT: Comparator 1 Output Status bit<sup>(2)</sup>

When CPOL = 0: 1 = VIN+ > VIN-0 = VIN+ < VIN-When CPOL = 1: 1 = VIN+ < VIN-0 = VIN+ > VIN-

**Note 1:** Reflects the value of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

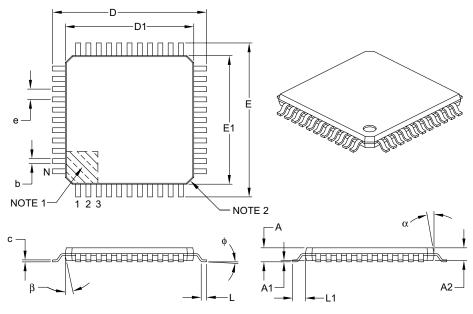

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |            | MILLIMETERS |      |      |

|--------------------------|------------|-------------|------|------|

| Dimens                   | ion Limits | MIN         | NOM  | MAX  |

| Number of Leads          | N          | 44          |      |      |

| Lead Pitch               | е          | 0.80 BSC    |      |      |

| Overall Height           | Α          | _           | _    | 1.20 |

| Molded Package Thickness | A2         | 0.95        | 1.00 | 1.05 |

| Standoff                 | A1         | 0.05        | _    | 0.15 |

| Foot Length              | L          | 0.45        | 0.60 | 0.75 |

| Footprint                | L1         | 1.00 REF    |      |      |

| Foot Angle               | ф          | 0°          | 3.5° | 7°   |

| Overall Width            | Е          | 12.00 BSC   |      |      |

| Overall Length           | D          | 12.00 BSC   |      |      |

| Molded Package Width     | E1         | 10.00 BSC   |      |      |

| Molded Package Length    | D1         | 10.00 BSC   |      |      |

| Lead Thickness           | С          | 0.09        | _    | 0.20 |

| Lead Width               | b          | 0.30        | 0.37 | 0.45 |

| Mold Draft Angle Top     | α          | 11°         | 12°  | 13°  |

| Mold Draft Angle Bottom  | β          | 11°         | 12°  | 13°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

# **INDEX**

| A                                                    | Timer1 External Clock Requirements         |      |

|------------------------------------------------------|--------------------------------------------|------|

| Absolute Maximum Ratings401                          | Timer2/Timer4 External Clock Requirements  |      |

| AC Characteristics413, 471                           | Timer3/Timer5 External Clock Requirements  | 419  |

| 10-Bit ADC Conversion Requirements                   | UARTx I/O Requirements                     | 454  |

| 12-Bit ADC Conversion Requirements                   | ADC                                        |      |

| ADC Module459                                        | Control Registers                          | 325  |

| ADC Module (10-Bit Mode)                             | Helpful Tips                               | 324  |

| ADC Module (10-Bit Mode)                             | Key Features                               | 321  |

| ,                                                    | Resources                                  | 324  |

| Capacitive Loading Requirements on                   | Arithmetic Logic Unit (ALU)                | 44   |

| Output Pins                                          | Assembler                                  |      |

| DMA Module Requirements                              | MPASM Assembler                            | 398  |

| ECANx I/O Requirements                               |                                            |      |

| External Clock 414                                   | В                                          |      |

| High-Speed PWMx Requirements422                      | Bit-Reversed Addressing                    | 115  |

| I/O Timing Requirements416                           | Example                                    |      |

| I2Cx Bus Data Requirements (Master Mode)451          | Implementation                             |      |

| I2Cx Bus Data Requirements (Slave Mode)453           | Sequence Table (16-Entry)                  |      |

| Input Capture x Requirements420                      | Block Diagrams                             |      |

| Internal FRC Accuracy415                             | Data Access from Program Space             |      |

| Internal LPRC Accuracy415                            | Address Generation                         | 117  |

| Internal RC Accuracy472                              | 16-Bit Timer1 Module                       |      |

| Load Conditions 413, 471                             |                                            |      |

| OCx/PWMx Mode Requirements421                        | ADC Conversion Clock Period                | 323  |

| Op Amp/Comparator Voltage Reference                  | ADC with Connection Options for ANx Pins   | 200  |

| Settling Time Specifications457                      | and Op Amps                                |      |

| Output Compare x Requirements421                     | Arbiter Architecture                       |      |

| PLL Clock415, 471                                    | BEMF Voltage Measurement Using ADC         |      |

| QEI External Clock Requirements                      | Boost Converter Implementation             |      |

| QEI Index Pulse Requirements425                      | CALL Stack Frame                           |      |

| Quadrature Decoder Requirements                      | Comparator (Module 4)                      |      |

| Reset, Watchdog Timer, Oscillator Start-up Timer,    | Connections for On-Chip Voltage Regulator  |      |

| Power-up Timer Requirements417                       | CPU Core                                   |      |

| SPI1 Master Mode (Full-Duplex, CKE = 0, CKP = x,     | CRC Module                                 |      |

| SMP = 1) Requirements                                | CRC Shift Engine                           |      |

| SPI1 Master Mode (Full-Duplex, CKE = 1, CKP = x,     | CTMU Module                                | 316  |

| SMP = 1) Requirements                                | Digital Filter Interconnect                |      |

| SPI1 Master Mode (Half-Duplex, Transmit Only)        | DMA Controller                             | 141  |

| Requirements439                                      | DMA Controller Module                      | 139  |

| SPI1 Maximum Data/Clock Rate Summary                 | dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/      | /50X |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,               | and PIC24EPXXXGP/MC20X                     | 25   |

| CKP = 0, SMP = 0) Requirements449                    | ECAN Module                                | 288  |

|                                                      | EDS Read Address Generation                | 105  |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,               | EDS Write Address Generation               | 106  |

| CKP = 1, SMP = 0) Requirements                       | Example of MCLR Pin Connections            | 30   |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,               | High-Speed PWMx Architectural Overview     | 227  |

| CKP = 0, SMP = 0) Requirements443                    | High-Speed PWMx Register Interconnection   |      |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,               | I2Cx Module                                |      |

| CKP = 1, SMP = 0) Requirements445                    | Input Capture x                            |      |

| SPI2 Master Mode (Full-Duplex, CKE = 0, CKP = x, SMP | Interleaved PFC                            |      |

| = 1) Requirements429                                 | Multiphase Synchronous Buck Converter      |      |

| SPI2 Master Mode (Full-Duplex, CKE = 1,              | Multiplexing Remappable Output for RPn     |      |

| CKP = x, SMP = 1) Requirements 428                   | Op Amp Configuration A                     |      |

| SPI2 Master Mode (Half-Duplex, Transmit Only)        | Op Amp Configuration B                     |      |

| Requirements427                                      | Op Amp/Comparator Voltage Reference Module |      |

| SPI2 Maximum Data/Clock Rate Summary 426             | Op Amp/Comparator x (Modules 1, 2, 3)      |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,               | Oscillator System                          |      |

| CKP = 0, SMP = 0) Requirements437                    |                                            |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 0, CKP = 1, SMP  | Output Compare x Module<br>PLL             |      |

| = 0) Requirements435                                 |                                            |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,               | Programmer's Model                         |      |

| CKP = 0, SMP = 0) Requirements431                    | PTG Module                                 |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,               | Quadrature Encoder Interface               |      |

| CKP = 1, SMP = 0) Requirements433                    | Recommended Minimum Connection             | 30   |