#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

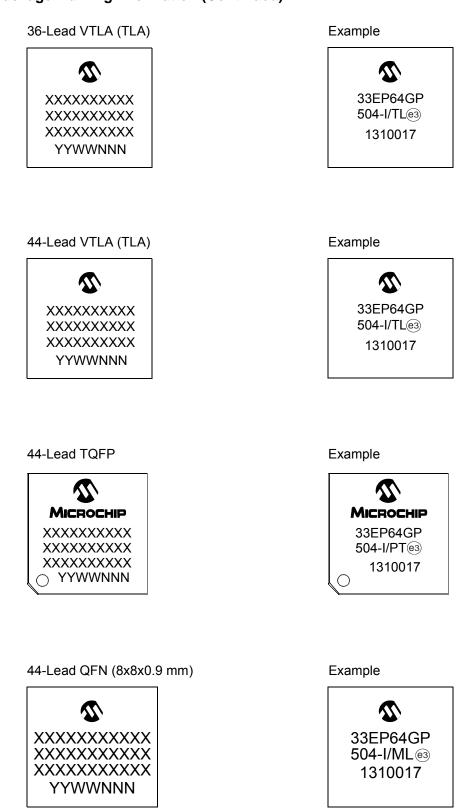

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |              | -         | -         | -          |        |       |                |       |             |       |           |            |       |       |       |               |

|--------------|-------|--------|--------------|-----------|-----------|------------|--------|-------|----------------|-------|-------------|-------|-----------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13    | Bit 12    | Bit 11     | Bit 10 | Bit 9 | Bit 8          | Bit 7 | Bit 6       | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |              |           |           | NT1R<6:0>  |        |       |                |       | _           | _     | _         | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —            | —         | -         |            | -      |       |                | -     |             |       |           | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  |        | _            | _         | _         | _          | _      | _     | _              | _     |             |       | -         | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |              |           |           | IC2R<6:0>  |        |       |                | —     | IC1R<6:0>   |       |           |            |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |              | IC4R<6:0> |           |            |        |       | —              |       |             |       | IC3R<6:0> |            |       |       | 0000  |               |

| RPINR11      | 06B6  | _      | _            | _         | —         | _          | _      | _     | — — OCFAR<6:0> |       |             |       |           |            | 0000  |       |       |               |

| RPINR12      | 06B8  | _      |              |           | l         | =LT2R<6:0> |        |       |                | —     | FLT1R<6:0>  |       |           |            |       |       | 0000  |               |

| RPINR14      | 06BC  | _      |              |           | (         | QEB1R<6:0  | >      |       |                | —     | QEA1R<6:0>  |       |           |            |       |       | 0000  |               |

| RPINR15      | 06BE  | _      |              |           | Н         | OME1R<6:0  | )>     |       |                | —     | INDX1R<6:0> |       |           |            |       |       | 0000  |               |

| RPINR18      | 06C4  | _      | _            | _         | —         | _          | _      | _     | _              | —     |             |       | ι         | J1RXR<6:0> | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _            | _         | _         | _          | _      | _     | _              | —     |             |       | ι         | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | •         | S         | CK2INR<6:0 | )>     |       |                | _     |             |       |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _            |           | SS2R<6:0> |            |        |       |                |       |             | 0000  |           |            |       |       |       |               |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |           |           |            |        |       | _              | _     | _           | _     | _         | _          | _     | _     | 0000  |               |

| RPINR38      | 06EC  | _      | DTCMP1R<6:0> |           |           |            |        |       | _              |       |             |       |           |            | _     | 0000  |       |               |

| RPINR39      | 06EE  | _      |              |           | DT        | CMP3R<6:   | 0>     |       |                | —     |             |       | D         | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

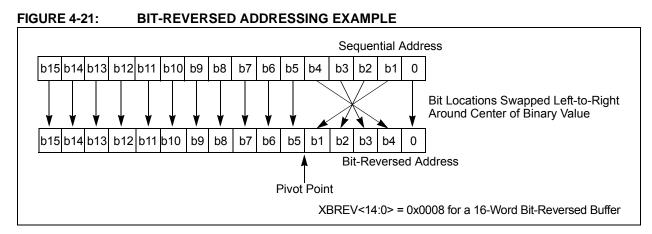

## TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

## 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

## 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                               | CONTROL R      | EGISTER          |                      |                      |                     |

|---------------|-----------------------------------------|--------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                    | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                    | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15        | ·                                       | •                                          |                | ÷                |                      |                      | bit                 |

| R/W-0         | R/W-0                                   | R/W-0                                      | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1          |                                         | DTCP <sup>(3)</sup>                        | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7         | DICO                                    | DICE                                       | _              | INT DO           | CAIM                 | AFRES'               | bit                 |

|               |                                         |                                            |                |                  |                      |                      | <u> </u>            |

| Legend:       |                                         | HC = Hardware                              | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada     | able bit                                | W = Writable bi                            | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |

| -n = Value    | at POR                                  | '1' = Bit is set                           |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                        | is hit(1)      |                  |                      |                      |                     |

| DIL 15        |                                         | rrupt is pending                           |                |                  |                      |                      |                     |

|               |                                         | interrupt is pendi                         | ng             |                  |                      |                      |                     |

|               |                                         | ared by setting F                          |                |                  |                      |                      |                     |

| bit 14        |                                         | rent-Limit Interru                         | •              |                  |                      |                      |                     |

|               |                                         | mit interrupt is pe                        |                |                  |                      |                      |                     |

|               |                                         | nt-limit interrupt is<br>ared by setting C |                |                  |                      |                      |                     |

| bit 13        |                                         | igger Interrupt S                          |                |                  |                      |                      |                     |

|               |                                         | terrupt is pendin                          |                |                  |                      |                      |                     |

|               |                                         | r interrupt is pen                         |                |                  |                      |                      |                     |

|               |                                         | ared by setting T                          |                |                  |                      |                      |                     |

| bit 12        |                                         | t Interrupt Enable                         | e bit          |                  |                      |                      |                     |

|               |                                         | rrupt is enabled rrupt is disabled         | and the FLTS   | TAT bit is clear | ed                   |                      |                     |

| bit 11        |                                         | ent-Limit Interrup                         |                |                  | cu .                 |                      |                     |

|               |                                         | mit interrupt is er                        |                |                  |                      |                      |                     |

|               |                                         | mit interrupt is di                        |                | e CLSTAT bit is  | s cleared            |                      |                     |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                           | able bit       |                  |                      |                      |                     |

|               |                                         | event generates                            |                |                  | T hit is cleared     |                      |                     |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I     |                |                  | i bit is cleared     |                      |                     |

| DIL 9         |                                         | register provides                          |                | riad for this PM | VM generator         |                      |                     |

|               |                                         | egister provides f                         | •              |                  | •                    |                      |                     |

| bit 8         |                                         | er Duty Cycle Re                           |                |                  |                      |                      |                     |

|               |                                         | ister provides du<br>jister provides du    |                |                  |                      | r                    |                     |

| Note 1:       | Software must clea                      |                                            |                |                  | -                    |                      | t controller        |

| Note 1.<br>2: | These bits should                       | -                                          |                | -                | -                    | the interrup         |                     |

| 3:            | DTC<1:0> = 11 fo                        | -                                          |                | -                | -                    |                      |                     |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                           |                | •                |                      | igned mode. If       | TTB = 0, the        |

| 5:            | To operate in Exter                     |                                            | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>۸xL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

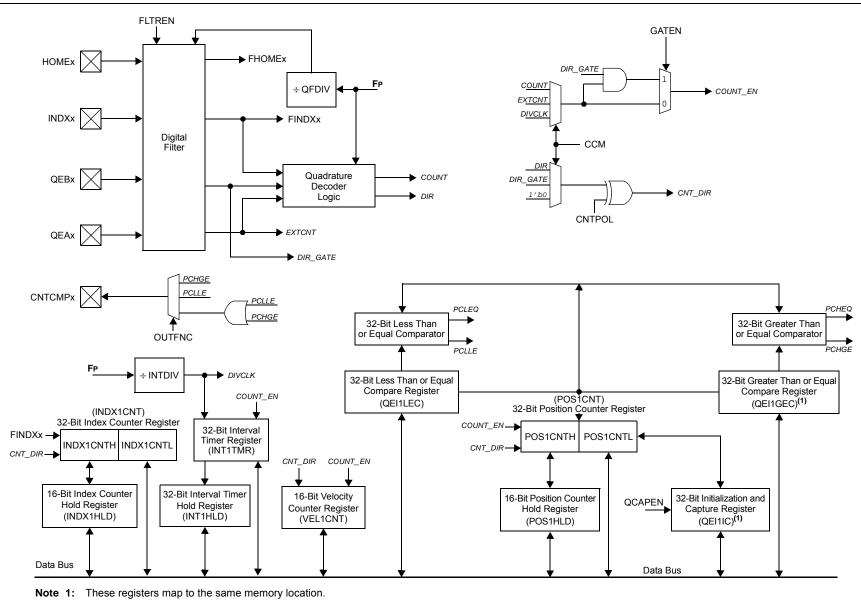

#### FIGURE 17-1: QEI BLOCK DIAGRAM

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       5ID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       -       -       EID17       EID16       bit 0       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                                          |                                |               |                  |                  |                 |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------------------|---------------|------------------|------------------|-----------------|-------|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                          | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID       EID         bit 1-0       EID       Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SID10         | SID9                                                                     | SID8                           | SID7          | SID6             | SID5             | SID4            | SID3  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        | ÷                                                                        |                                |               |                  |                  |                 | bit 8 |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                |               |                  |                  |                 |       |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                    | R/W-x                          | U-0           | R/W-x            | U-0              | R/W-x           | R/W-x |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                           | _             | EXIDE            |                  | EID17           | EID16 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         1f MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Matches bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7         |                                                                          |                                |               |                  |                  |                 | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Message Sit, SIDE       5         bit 2       Unimplemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 4       Unimplemented: Read as '0'         bit 1-0       EID         if MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                          |                                |               |                  |                  |                 |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         o = Message address bit, SIDx, must be '1' to match filter       0' = Bit is cleared       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:       |                                                                          |                                |               |                  |                  |                 |       |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | e bit                                                                    | W = Writable                   | bit           | U = Unimpler     | nented bit, read | d as '0'        |       |

| 1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         I= Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value at | POR                                                                      | '1' = Bit is set               |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 4         | 0 = Message                                                              | address bit, SI                | Dx, must be ' |                  |                  |                 |       |

| bit 1-0 EID<17:16>: Extended Identifier bits<br>1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 3         | <u>If MIDE = 1:</u><br>1 = Matches<br>0 = Matches<br><u>If MIDE = 0:</u> | only messages<br>only messages | with Extende  |                  |                  |                 |       |

| 1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2         | Unimplemen                                                               | ted: Read as '                 | כ'            |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 1-0       | EID<17:16>:                                                              | Extended Iden                  | tifier bits   |                  |                  |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | •                                                                        |                                |               |                  |                  |                 |       |

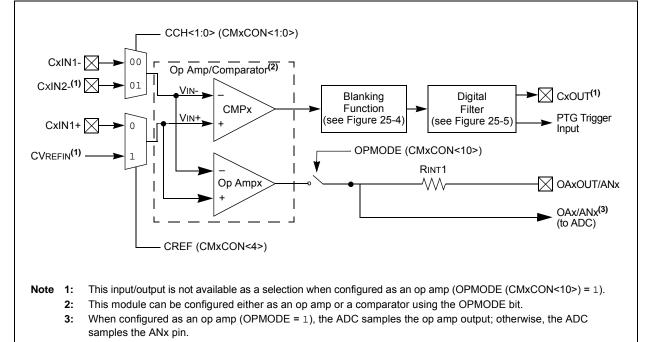

## 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

## 25.1 Op Amp Application Considerations

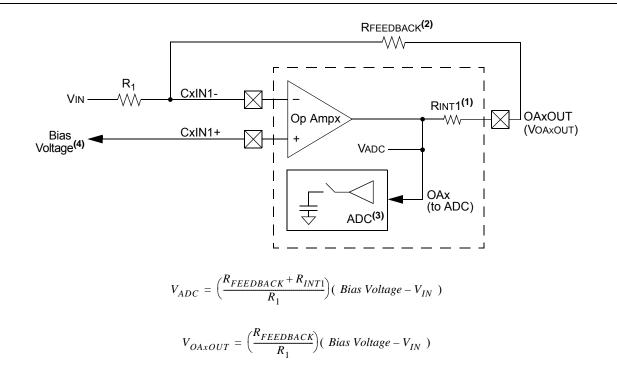

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

## 25.1.1 OP AMP CONFIGURATION A