Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

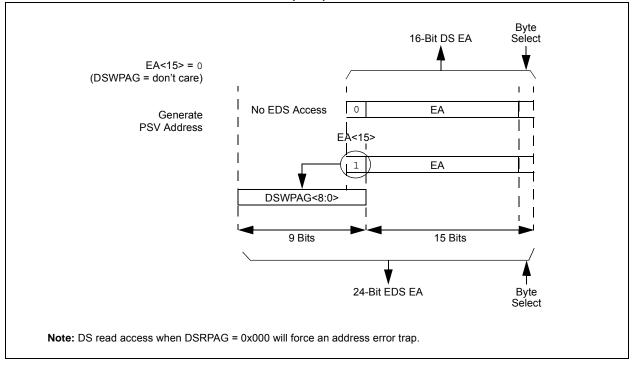

### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

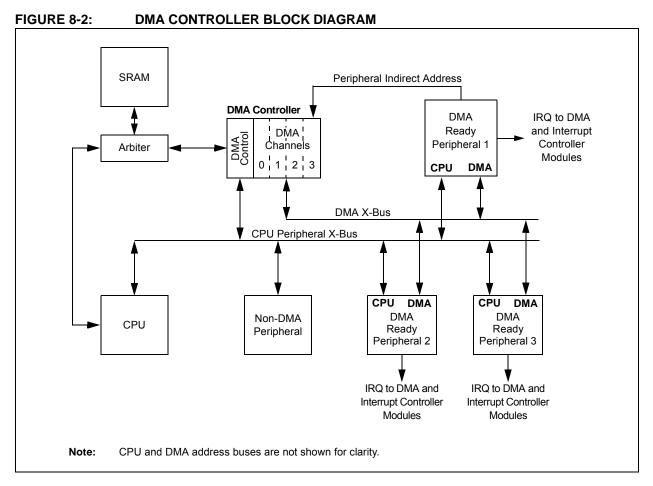

### 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0                                    | U-0     | U-0 | U-0 | U-0   |

|----------------|-----|-----------------|----------------------------------------|---------|-----|-----|-------|

| —              | —   | —               | —                                      | —       | —   | -   | —     |

| bit 15         |     |                 |                                        |         |     |     | bit 8 |

|                |     |                 |                                        |         |     |     |       |

| R-0            | R-0 | R-0             | R-0                                    | R-0     | R-0 | R-0 | R-0   |

|                |     |                 | DSADR                                  | <23:16> |     |     |       |

| bit 7          |     |                 |                                        |         |     |     | bit 0 |

|                |     |                 |                                        |         |     |     |       |

| Legend:        |     |                 |                                        |         |     |     |       |

| R = Readable b | it  | W = Writable bi | bit U = Unimplemented bit, read as '0' |         |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | J = Unimplemented bit, read as '0' |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0                                     | R-0      | R-0 | R-0 | R-0   |  |

|------------------|-----|------------------|-----------------------------------------|----------|-----|-----|-------|--|

|                  |     |                  | DSAD                                    | DR<15:8> |     |     |       |  |

| bit 15           |     |                  |                                         |          |     |     | bit 8 |  |

|                  |     |                  |                                         |          |     |     |       |  |

| R-0              | R-0 | R-0              | R-0                                     | R-0      | R-0 | R-0 | R-0   |  |

| DSADR<7:0>       |     |                  |                                         |          |     |     |       |  |

| bit 7            |     |                  |                                         |          |     |     | bit 0 |  |

|                  |     |                  |                                         |          |     |     |       |  |

| Legend:          |     |                  |                                         |          |     |     |       |  |

| R = Readable b   | it  | W = Writable bit | ut U = Unimplemented bit, read as '0'   |          |     |     |       |  |

| -n = Value at PC | OR  | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |          |     |     | own   |  |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| U-0             | U-0                                       | U-0              | U-0             | U-0              | U-0              | U-0             | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

| —               | —                                         | —                |                 | —                | —                | —               | PLLDIV8 |

| bit 15          |                                           |                  |                 |                  |                  |                 | bit 8   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3          | PLLDIV2          | PLLDIV1         | PLLDIV0 |

| bit 7           |                                           |                  |                 |                  |                  |                 | bit 0   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| Legend:         |                                           |                  |                 |                  |                  |                 |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                 |                                           |                  |                 |                  |                  |                 |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                  |                  |                 |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)        |         |

|                 | 111111111 =                               | = 513            |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000110000 =                               | = 50 (default)   |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0          | U-0                 | U-0                                | U-0   | U-0                  | U-0              | U-0                | U-0   |

|--------------|---------------------|------------------------------------|-------|----------------------|------------------|--------------------|-------|

| —            | —                   | —                                  | _     | —                    | —                | —                  | _     |

| bit 15       |                     |                                    |       |                      |                  |                    | bit 8 |

|              |                     |                                    |       |                      |                  |                    |       |

| U-0          | R/W-0               | R/W-0                              | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0 |

| —            |                     |                                    |       | INT2R<6:0>           |                  |                    |       |

| bit 7        |                     |                                    |       |                      |                  |                    | bit 0 |

|              |                     |                                    |       |                      |                  |                    |       |

| Legend:      |                     |                                    |       |                      |                  |                    |       |

| R = Readal   | ole bit             | W = Writable                       | bit   | U = Unimpler         | mented bit, read | as '0'             |       |

| -n = Value a | at POR              | '1' = Bit is set                   |       | '0' = Bit is cleared |                  | x = Bit is unknown |       |

|              |                     |                                    |       |                      |                  |                    |       |

| bit 15-7     | Unimplemen          | ted: Read as 'd                    | )'    |                      |                  |                    |       |

| bit 6-0      |                     | Assign Externa<br>-2 for input pin |       |                      | orresponding RI  | Pn Pin bits        |       |

|              | 1111001 <b>= lr</b> | put tied to RPI                    | 121   |                      |                  |                    |       |

|              |                     |                                    |       |                      |                  |                    |       |

|              |                     |                                    |       |                      |                  |                    |       |

|              | 0000001 – Ir        | put tied to CMI                    | ⊃1    |                      |                  |                    |       |

|              |                     | put tied to Civil                  |       |                      |                  |                    |       |

|              |                     |                                    |       |                      |                  |                    |       |

|              |                     |                                    |       |                      |                  |                    |       |

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |                     |                  |       |                                    |       |                    |       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                               | U-0                 | U-0              | U-0   | U-0                                | U-0   | U-0                | U-0   |  |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                 | -                   | —                | _     | —                                  | —     | —                  | —     |  |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15                            |                     |                  |       |                                    |       |                    | bit 8 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     |                  |       |                                    |       |                    |       |  |  |

| bit 7       Image: Constraint of the system of | U-0                               | R/W-0               | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td></td><td></td><td>T2CKR&lt;6:0&gt;</td><td>&gt;</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                 |                     |                  |       | T2CKR<6:0>                         | >     |                    |       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7                             |                     |                  |       |                                    |       |                    | bit 0 |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                     |                  |       |                                    |       |                    |       |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:                           |                     |                  |       |                                    |       |                    |       |  |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readable bit W = Writable bit |                     |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a                      | at POR              | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |                     |                  |       |                                    |       |                    |       |  |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7                          | Unimplemen          | ted: Read as 'd  | )'    |                                    |       |                    |       |  |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0                           | 5                   |                  |       |                                    |       |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     |                  |       | ,                                  |       |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     |                  |       |                                    |       |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |                     |                  |       |                                    |       |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   | 0000001 = Ir        | nout tied to CM  | ⊃1    |                                    |       |                    |       |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                     |                  |       |                                    |       |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   | 0000000 <b>- II</b> | iput tied to vss |       |                                    |       |                    |       |  |  |

### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP120 | )R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

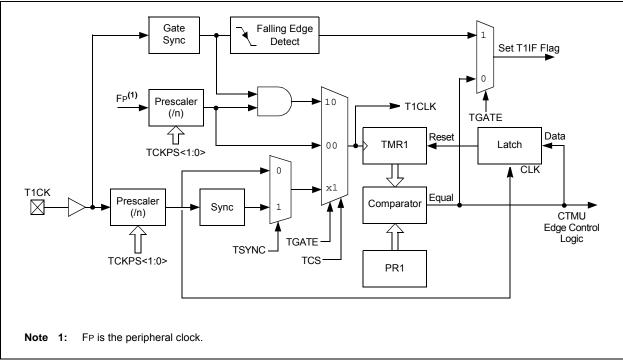

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

### TABLE 12-1: TIMER MODE SETTINGS

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

| R/W-0        | R/W-0                                              | R/W-0                                                                                                    | R/W-0          | U-0                                                                                                                                                                                         | U-0                 | U-0              | U-0          |  |  |  |  |

|--------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|--------------|--|--|--|--|

|              | TRGD                                               | V<3:0>                                                                                                   |                | —                                                                                                                                                                                           |                     | —                | _            |  |  |  |  |

| bit 15       |                                                    |                                                                                                          |                |                                                                                                                                                                                             |                     |                  | bit 8        |  |  |  |  |

|              |                                                    |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

| U-0          | U-0                                                | R/W-0                                                                                                    | R/W-0          | R/W-0                                                                                                                                                                                       | R/W-0               | R/W-0            | R/W-0        |  |  |  |  |

| _            |                                                    |                                                                                                          |                | TRGSTF                                                                                                                                                                                      | RT<5:0> <b>(1)</b>  |                  |              |  |  |  |  |

| bit 7        |                                                    |                                                                                                          |                |                                                                                                                                                                                             |                     |                  | bit          |  |  |  |  |

|              |                                                    |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

| Legend:      | 1. 1.4                                             |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

| R = Readab   |                                                    | W = Writable                                                                                             |                | •                                                                                                                                                                                           | nented bit, read    |                  |              |  |  |  |  |

| -n = Value a | t POR                                              | '1' = Bit is set                                                                                         |                | '0' = Bit is clea                                                                                                                                                                           | ared                | x = Bit is unkn  | own          |  |  |  |  |

|              |                                                    |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

| bit 15-12    |                                                    | <b>)&gt;:</b> Trigger # Ou                                                                               | -              |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

|              | 1111 = Trigger output for every 16th trigger event |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

|              |                                                    | 1110 = Trigger output for every 15th trigger event<br>1101 = Trigger output for every 14th trigger event |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |

|              | 1100 = Trigger output for every 13th trigger event |                                                                                                          |                |                                                                                                                                                                                             |                     |                  |              |  |  |  |  |