Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-h-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

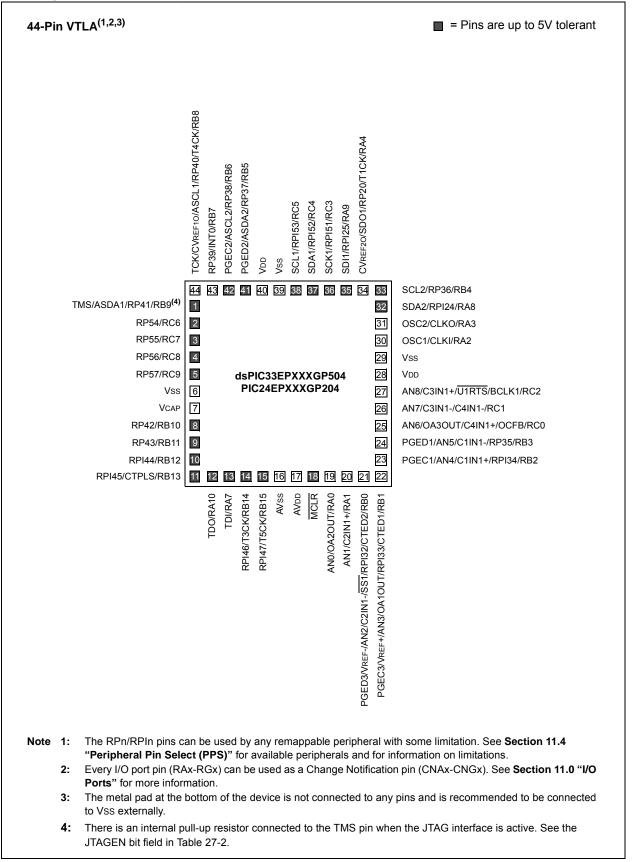

#### **Pin Diagrams (Continued)**

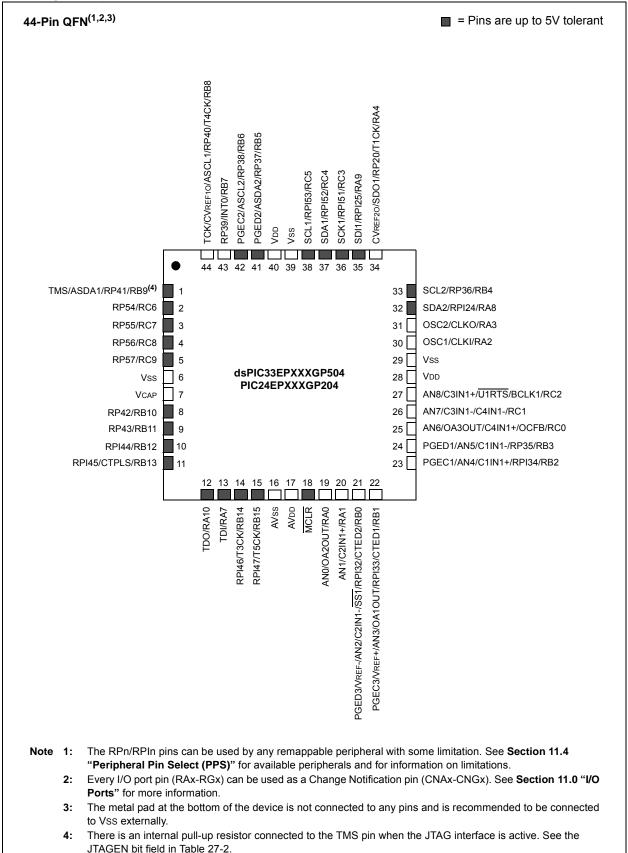

#### **Pin Diagrams (Continued)**

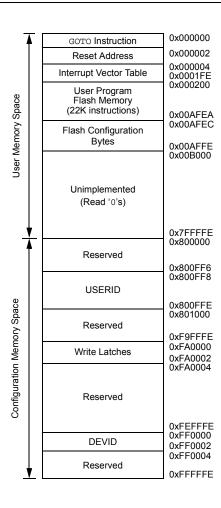

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

### TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

### 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "*dsPIC33/PIC24 Family Reference Manual*".

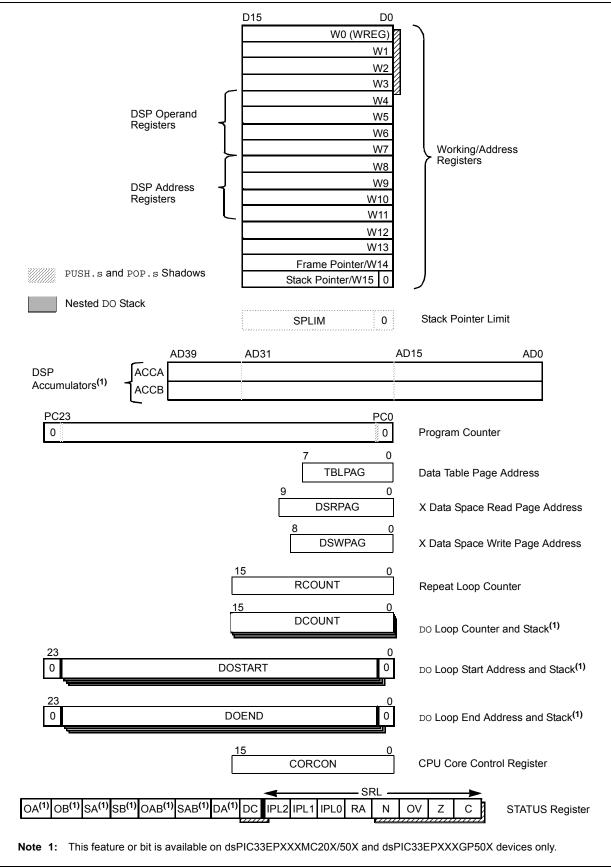

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

#### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                              | R/W-0                                                     | R/W-0                         | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------|------------------|-----------------|--------|

| —               | —                                                                                                                | CSIDL                                                     | ABAT                          | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |                                                                                                                  |                                                           |                               |                                |                  |                 | bit 8  |

| R-1             | R-0                                                                                                              | R-0                                                       | U-0                           | R/W-0                          | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1                                                                                                          | OPMODE0                                                   | _                             | CANCAP                         |                  |                 | WIN    |

| bit 7           |                                                                                                                  |                                                           |                               |                                |                  |                 | bit (  |

| Legend:         |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| R = Readable    | bit                                                                                                              | W = Writable I                                            | oit                           | U = Unimpler                   | mented bit, read | d as '0'        |        |

| -n = Value at F | OR                                                                                                               | '1' = Bit is set                                          |                               | '0' = Bit is cle               |                  | x = Bit is unkr | nown   |

|                 |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| bit 15-14       | Unimplemen                                                                                                       | ted: Read as 'o                                           | )'                            |                                |                  |                 |        |

| bit 13          | CSIDL: ECAN                                                                                                      | Nx Stop in Idle I                                         | Node bit                      |                                |                  |                 |        |

|                 |                                                                                                                  | ues module opera module opera                             |                               | device enters I<br>ode         | dle mode         |                 |        |

| bit 12          | ABAT: Abort                                                                                                      | All Pending Tra                                           | nsmissions b                  | bit                            |                  |                 |        |

|                 |                                                                                                                  | I transmit buffe<br>ill clear this bit                    |                               | ansmission<br>smissions are a  | aborted          |                 |        |

| bit 11          | CANCKS: EC                                                                                                       | ANx Module C                                              | lock (FCAN)                   | Source Select b                | bit              |                 |        |

|                 | 1 = FCAN is e<br>0 = FCAN is e                                                                                   | ·                                                         |                               |                                |                  |                 |        |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis | ed<br>nfiguration moo<br>ten Only mode<br>opback mode     | es mode<br>le                 | bits                           |                  |                 |        |

| bit 7-5         | 111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module                                                     |                                                           | Messages n<br>ation mode      | node                           |                  |                 |        |

|                 | 010 = Module<br>001 = Module<br>000 = Module                                                                     | e is in Loopback<br>e is in Disable n<br>e is in Normal C | mode<br>node<br>operation mod | de                             |                  |                 |        |

| bit 4           | -                                                                                                                | ted: Read as '                                            |                               |                                |                  |                 |        |

| bit 3           |                                                                                                                  | nput capture ba                                           |                               | Capture Event<br>message recei |                  |                 |        |

| bit 2-1         |                                                                                                                  | ted: Read as '(                                           | ı'                            |                                |                  |                 |        |

| bit 0           | -                                                                                                                | ap Window Sele                                            |                               |                                |                  |                 |        |

| UIL U           | 1 = Uses filter                                                                                                  | -                                                         | יטו טונ                       |                                |                  |                 |        |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |

|---------------|----------------------------------------|---------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                        | 1                                     |                  | 11                 |                 |                 | bit 8    |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | —               | _        |  |  |  |  |

| bit 7         |                                        |                                       |                  | 1 1                |                 | 1               | bit (    |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |

| Legend:       |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |

| R = Readabl   | le bit                                 | W = Writable                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                    | '1' = Bit is set                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |

| bit 15        | EDG1MOD: E                             | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 is                          | s edge-sensitive                      | 9                |                    |                 |                 |          |  |  |  |  |

|               | •                                      | s level-sensitive                     |                  |                    |                 |                 |          |  |  |  |  |

| bit 14        |                                        | dge 1 Polarity                        |                  |                    |                 |                 |          |  |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |  |

| L:1 40 40     | •                                      | s programmed f                        | •                | •                  |                 |                 |          |  |  |  |  |

| bit 13-10     |                                        | :0>: Edge 1 So                        | urce Select bits | 5                  |                 |                 |          |  |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved     |                                       |                  |                    |                 |                 |          |  |  |  |  |

|               |                                        | 01xx = Reserved<br>0011 = CTED1 pin   |                  |                    |                 |                 |          |  |  |  |  |

|               | 0010 = CTED2 pin                       |                                       |                  |                    |                 |                 |          |  |  |  |  |

|               | 0001 = OC1                             |                                       |                  |                    |                 |                 |          |  |  |  |  |

| hit O         | 0000 = Timer                           |                                       | :+               |                    |                 |                 |          |  |  |  |  |

| bit 9         |                                        | Edge 2 Status b                       |                  | vritten to control | the odge cou    | reo             |          |  |  |  |  |

|               | 1 = Edge 2 h                           |                                       |                  |                    | the edge sou    | ice.            |          |  |  |  |  |

|               |                                        | as not occurred                       | 1                |                    |                 |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: E                            | Edge 1 Status b                       | it               |                    |                 |                 |          |  |  |  |  |

|               |                                        |                                       | 1 and can be v   | vritten to control | the edge sou    | rce.            |          |  |  |  |  |

|               |                                        | ge 1 has occurred                     |                  |                    |                 |                 |          |  |  |  |  |

|               | -                                      | as not occurred                       |                  |                    |                 |                 |          |  |  |  |  |

| bit 7         |                                        | Edge 2 Edge Sa                        |                  | Selection bit      |                 |                 |          |  |  |  |  |

|               |                                        | s edge-sensitive<br>s level-sensitive |                  |                    |                 |                 |          |  |  |  |  |

| bit 6         | •                                      | dge 2 Polarity                        |                  |                    |                 |                 |          |  |  |  |  |

| Sit 0         |                                        | s programmed f                        |                  | dae response       |                 |                 |          |  |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |  |

| bit 5-2       | EDG2SEL<3                              | :0>: Edge 2 So                        | urce Select bits | 3                  |                 |                 |          |  |  |  |  |

|               | 1111 <b>= Rese</b>                     | rved                                  |                  |                    |                 |                 |          |  |  |  |  |

|               | 01xx = Rese                            |                                       |                  |                    |                 |                 |          |  |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE |                                       |                  |                    |                 |                 |          |  |  |  |  |

|               | 0010 = CTEE                            |                                       |                  |                    |                 |                 |          |  |  |  |  |

|               |                                        | Ji pili                               |                  |                    |                 |                 |          |  |  |  |  |

|               | 0001 = OC1                             | module                                |                  |                    |                 |                 |          |  |  |  |  |

|               |                                        | module                                |                  |                    |                 |                 |          |  |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|-----------------------------------------|-------|-------|-------|

|                                    |       |       | PTGA                               | DJ<15:8>                                |       |       |       |

| bit 15                             |       |       |                                    |                                         |       |       | bit 8 |

|                                    |       |       |                                    |                                         |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | PTGA                               | DJ<7:0>                                 |       |       |       |

| bit 7                              |       |       |                                    |                                         |       |       | bit 0 |

|                                    |       |       |                                    |                                         |       |       |       |

| Legend:                            |       |       |                                    |                                         |       |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |                                         |       |       |       |

| -n = Value at POR (1' = Bit is set |       |       |                                    | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

## REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | PTGL0<15:8> |       |       |       |       |       |       |  |  |  |

| bit 15 |             |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | PTGL0<7:0>  |       |       |       |       |       |       |  |  |  |

| bit 7 | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| U-0           | U-0                                 | U-0               | R/W-0          | R/W-0                                 | R/W-0   | R/W-0              | R/W-0   |  |

|---------------|-------------------------------------|-------------------|----------------|---------------------------------------|---------|--------------------|---------|--|

| _             | —                                   | —                 | DWIDTH4        | DWIDTH3                               | DWIDTH2 | DWIDTH1            | DWIDTH0 |  |

| bit 15        |                                     |                   |                |                                       |         |                    | bit 8   |  |

|               |                                     |                   |                |                                       |         |                    |         |  |

| U-0           | U-0                                 | U-0               | R/W-0          | R/W-0                                 | R/W-0   | R/W-0              | R/W-0   |  |

| —             | —                                   | —                 | PLEN4          | PLEN3                                 | PLEN2   | PLEN1              | PLEN0   |  |

| bit 7         |                                     |                   |                |                                       |         |                    | bit 0   |  |

|               |                                     |                   |                |                                       |         |                    |         |  |

| Legend:       |                                     |                   |                |                                       |         |                    |         |  |

| R = Readable  | e bit                               | W = Writable      | bit            | it U = Unimplemented bit, read as '0' |         |                    |         |  |

| -n = Value at | POR                                 | '1' = Bit is set  |                | '0' = Bit is cle                      | ared    | x = Bit is unknown |         |  |

|               |                                     |                   |                |                                       |         |                    |         |  |

| bit 15-13     | Unimplemen                          | ted: Read as '    | 0'             |                                       |         |                    |         |  |

| bit 12-8      | DWIDTH<4:0>: Data Width Select bits |                   |                |                                       |         |                    |         |  |

|               | These bits se                       | t the width of th | ne data word ( | DWIDTH<4:0>                           | • + 1). |                    |         |  |

| bit 7-5       | Unimplemen                          | ted: Read as '    | 0'             |                                       |         |                    |         |  |

|               |                                     |                   |                |                                       |         |                    |         |  |

#### REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

#### 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

### 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

#### 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

### 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |                               | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9                  | BTG                  | BTG     | f,#bit4                       | Bit Toggle f                                               | 1             | 1                             | None                     |

|                    |                      | BTG     | Ws,#bit4                      | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4                       | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSC    | Ws,#bit4                      | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4                       | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSS    | Ws,#bit4                      | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                       | Bit Test f                                                 | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,#bit4                      | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,#bit4                      | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,Wb                         | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,Wb                         | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                       | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4                      | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4                      | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                 | CALL                 | CALL    | lit23                         | Call subroutine                                            | 2             | 4                             | SFA                      |

|                    |                      | CALL    | Wn                            | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                    |                      | CALL.L  | Wn                            | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                 | CLR                  | CLR     | f                             | f = 0x0000                                                 | 1             | 1                             | None                     |

|                    |                      | CLR     | WREG                          | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                    |                      | CLR     | Ws                            | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB(1) | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  |                               | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17                 | COM                  | СОМ     | f                             | $f = \bar{f}$                                              | 1             | 1                             | N,Z                      |

|                    |                      | COM     | f,WREG                        | WREG = $\overline{f}$                                      | 1             | 1                             | N,Z                      |

|                    |                      | СОМ     | Ws,Wd                         | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                 | CP                   | CP      | f                             | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    | 01                   | CP      | Wb,#lit8                      | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                         | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                 | CP0                  | CPO     | f                             | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

| 10                 | 010                  | CPO     | Ws                            | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                             | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    | 012                  | CPB     | Wb,#lit8                      | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                         | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                         | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                         | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                         | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                         | Compare Wb with Wn, skip if $\neq$                         | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBNE                | CPBNE   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| <b>TABLE 28-2:</b> | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED | ) |

|--------------------|-----------------------------------|-----------|---|

|                    |                                   | CONTINUED | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |                          |       |                                |

|--------------------|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max.                     | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK2 Input<br>Frequency                 | -                                                                                                                                                                                                                                                                                       | -                   | Lesser<br>of FP<br>or 15 | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK2 Input Fall Time                            | _                                                                                                                                                                                                                                                                                       |                     |                          | ns    | See Parameter DO32<br>(Note 4) |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                                                                                                                                                                                                                                                                       |                     |                          | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | —                                                                                                                                                                                                                                                                                       |                     |                          | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                                                                                                                                                                                                                                                       | _                   | _                        | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                                                                                                                                                                                                                                                       | 6                   | 20                       | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                                                                                                                                                                                                                                                      | _                   | _                        | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                                                                                                                                                                                                                                                      |                     |                          | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                                                                                                                                                                                                                                                      |                     |                          | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                                                                                                                                                                                                                                                     | _                   | _                        | ns    |                                |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                                                                                                                                                                                                                                                      | _                   | 50                       | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | _                   | _                        | ns    | (Note 4)                       |

| SP60               | TssL2doV              | SDO2 Data Output Valid after<br>SS2 Edge        | —                                                                                                                                                                                                                                                                                       |                     | 50                       | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

| AC CHARACTERISTICS |        |                                                                                                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup>                                                                                                         |         |       |       |                                         |  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|-----------------------------------------|--|

|                    |        |                                                                                                     | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |       |                                         |  |

| Param<br>No.       | Symbol | Characteristic                                                                                      | Min.                                                                                                                                                                                         | Тур.    | Max.  | Units | Conditions                              |  |

|                    |        | Cloci                                                                                               | k Parame                                                                                                                                                                                     | eters   |       |       |                                         |  |

| AD50               | TAD    | ADC Clock Period                                                                                    | 76                                                                                                                                                                                           | _       | _     | ns    |                                         |  |

| AD51               | tRC    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |                                                                                                                                                                                              | 250     | _     | ns    |                                         |  |

|                    | •      | Conv                                                                                                | version F                                                                                                                                                                                    | Rate    |       | •     |                                         |  |

| AD55               | tCONV  | Conversion Time                                                                                     |                                                                                                                                                                                              | 12 Tad  | _     |       |                                         |  |

| AD56               | FCNV   | Throughput Rate                                                                                     | _                                                                                                                                                                                            | —       | 1.1   | Msps  | Using simultaneous sampling             |  |

| AD57a              | TSAMP  | Sample Time when Sampling any ANx Input                                                             | 2 Tad                                                                                                                                                                                        | —       | _     | —     |                                         |  |

| AD57b              | TSAMP  | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad                                                                                                                                                                                        | _       | —     | —     |                                         |  |

|                    |        | Timin                                                                                               | g Param                                                                                                                                                                                      | eters   |       |       |                                         |  |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad                                                                                                                                                                                        | —       | 3 Tad | _     | Auto-convert trigger is<br>not selected |  |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad                                                                                                                                                                                        | —       | 3 Tad | —     |                                         |  |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _                                                                                                                                                                                            | 0.5 Tad |       | —     |                                         |  |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |                                                                                                                                                                                              | —       | 20    | μs    | (Note 6)                                |  |

#### TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

#### TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |

|--------------------|--------------------------------|-------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Characteristic                 | Min.                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DM1                | DMA Byte/Word Transfer Latency | 1 Tcy <b>(2)</b>                                      | -                   | _    | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

<sup>© 2011-2013</sup> Microchip Technology Inc.

NOTES:

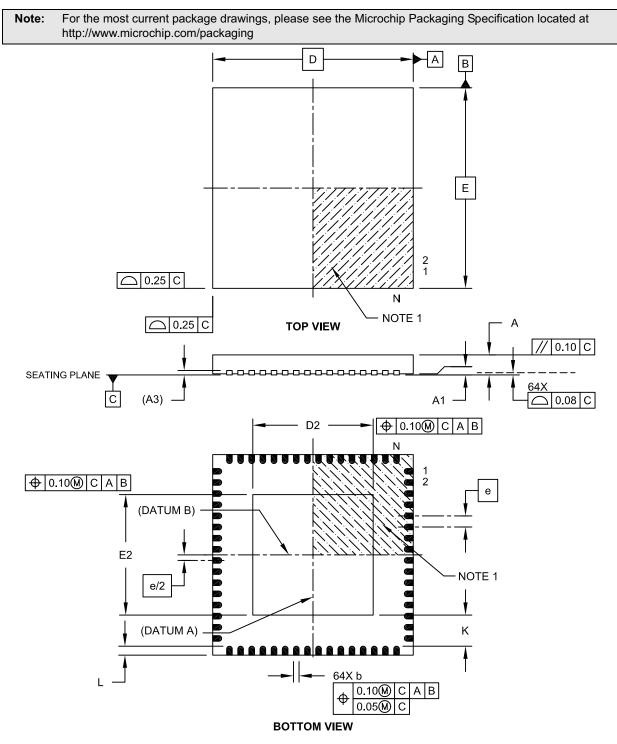

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

## Revision H (August 2013)