Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

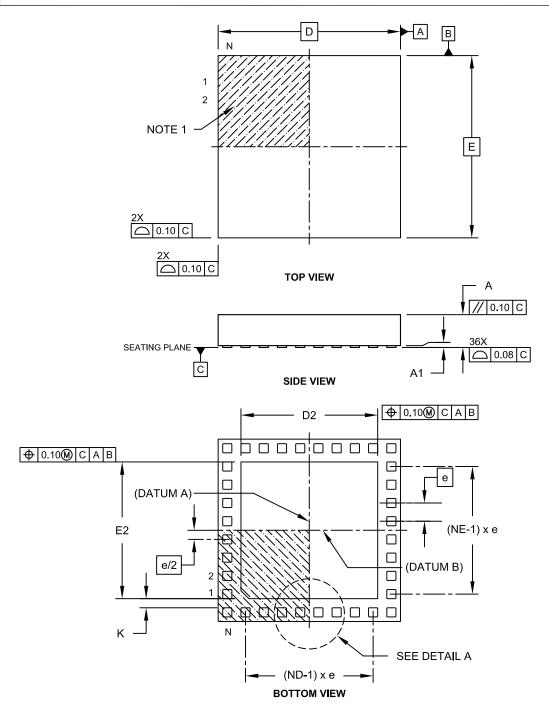

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-i-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

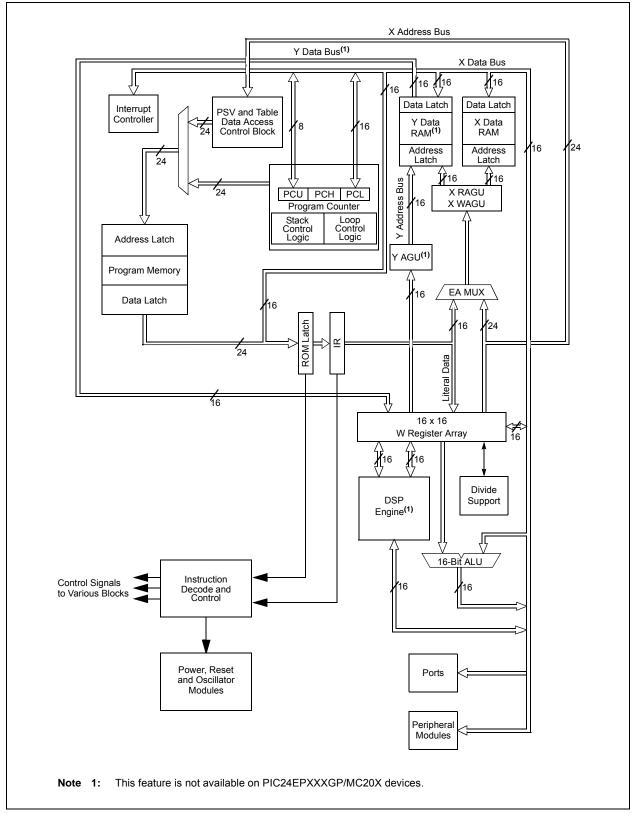

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

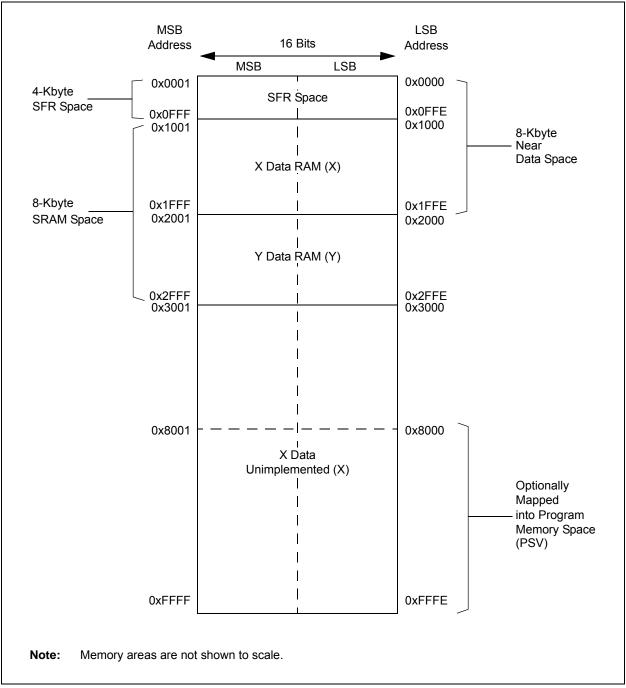

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _          | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |            |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |            |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     | SDI2R<6:0> |       |       |            | 0000  |       |       |               |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     | SS2R<6:0>  |       |       |            | 0000  |       |       |               |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     | C1RXR<6:0> |       |       |            | 0000  |       |       |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |        |        | INT1R<6:0> |        |       |       | —     | —          | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | -     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |            |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |            |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |        |        |        | FLT2R<6:0> | •      |       |       | _     |            |       |       | FLT1R<6:0> | •     |       |       | 0000          |

| RPINR14   | 06BC  |        |        |        | (      | QEB1R<6:0  | >      |       |       | _     | QEA1R<6:0> |       |       |            |       | 0000  |       |               |

| RPINR15   | 06BE  |        |        |        | Н      | OME1R<6:0  | )>     |       |       | _     |            |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |            |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |        | S      | CK2INR<6:( | )>     |       |       | —     |            |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —      |        | —          | —      |       | —     | —     |            |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _      |        | —          | —      |       | —     | —     |            |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        |        | S      | YNCI1R<6:0 | )>     |       |       | —     |            |       |       |            | 0000  |       |       |               |

| RPINR38   | 06EC  | _      |        |        | D      | CMP1R<6:   | 0>     |       |       | —     |            |       |       |            | 0000  |       |       |               |

| RPINR39   | 06EE  | _      |        |        | D      | FCMP3R<6:  | 0>     |       |       | _     |            |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0       U-0       U-0       R-0       R-0       R-0       R-0         -       -       -       -       RQCOL3       RQCOL2       RQCOL1       RQCOL0         bit 7       -       -       -       RQCOL3       RQCOL2       RQCOL1       RQCOL0         bit 7       -       -       -       RQCOL3       RQCOL2       RQCOL1       RQCOL0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'          n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-4       Unimplemented: Read as '0'           bit 3       RQCOL3: DMA Channel 3 Transfer Request Collision Flag bit       1 = User force and interrupt-based request collision is detected         bit 2       RQCOL2: DMA Channel 2 Transfer Request Collision Flag bit       1 = User force and interrupt-based request collision is detected         bit 2       RQCOL2: DMA Channel 2 Transfer Request collision is detected       0 = No request collision is detected         bit 2       RQCOL2: DMA Channel 2 Transfer Request collision is detected       0 = No request collision is detected |                |                    |              |                                         |                  |          |        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|--------------|-----------------------------------------|------------------|----------|--------|--|

| U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0            | U-0                | U-0          | U-0                                     | U-0              | U-0      | U-0    |  |

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —              | —                  | —            | —                                       | —                | —        | —      |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                    |              |                                         |                  |          | bit 8  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                    |              |                                         |                  |          |        |  |

| U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0            | U-0                | U-0          | R-0                                     | R-0              | R-0      | R-0    |  |

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | —                  | —            | RQCOL3                                  | RQCOL2           | RQCOL1   | RQCOL0 |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                    |              |                                         |                  |          | bit 0  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                    |              |                                         |                  |          |        |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                    |              |                                         |                  |          |        |  |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit            | W = Writable       | bit          | U = Unimpler                            | mented bit, read | l as '0' |        |  |

| -n = Value at F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | POR            | '1' = Bit is set   |              | '0' = Bit is cleared x = Bit is unknown |                  |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                    |              |                                         |                  |          |        |  |

| bit 15-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Unimplemen     | ted: Read as '     | כ'           |                                         |                  |          |        |  |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RQCOL3: DN     | /IA Channel 3 T    | ransfer Requ | est Collision F                         | ag bit           |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                    |              | st collision is d                       | etected          |          |        |  |

| <b>h</b> # 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •              |                    |              | est Callisian Fl                        | aa hit           |          |        |  |

| DIL Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                    | •            |                                         | 0                |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | •                  |              |                                         | elecieu          |          |        |  |

| bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RQCOL1: DN     | /IA Channel 1 T    | ransfer Requ | est Collision F                         | ag bit           |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 = User for   | e and interrupt    | -based reque | st collision is d                       | etected          |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 = No reque   | est collision is d | etected      |                                         |                  |          |        |  |

| bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RQCOLO: DN     | /IA Channel 0 T    | ransfer Requ | est Collision F                         | lag bit          |          |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 = User force | e and interrupt    | -based reque | st collision is d                       | etected          |          |        |  |

# REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

# REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> 444 A                             | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA            | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

NOTES:

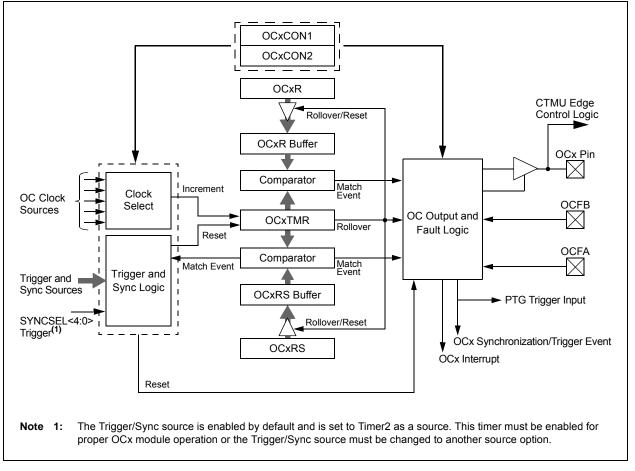

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                          | R/W-0                                  | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |

|---------------|------------------------------|----------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|

|               | 0-0                          | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |

| <br>bit 15    |                              | COOIDE                                 |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |

| Sit 10        |                              |                                        |                   |                   |                        |                  | bit 0         |

| R/W-0         | U-0                          | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |

| ENFLT         |                              | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |

| bit 7         |                              |                                        |                   |                   |                        |                  | bit 0         |

|               |                              |                                        |                   |                   |                        |                  |               |

| Legend:       |                              | HSC = Hardw                            | are Settable/Cl   | earable bit       |                        |                  |               |

| R = Read      | able bit                     | W = Writable I                         | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |

| -n = Value    | e at POR                     | '1' = Bit is set                       |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |

|               |                              |                                        |                   |                   |                        |                  |               |

| bit 15-14     | Unimplemen                   | ted: Read as 'o                        | )'                |                   |                        |                  |               |

| bit 13        | OCSIDL: Out                  | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                        |                  |               |

|               |                              | ompare x Halts                         |                   |                   |                        |                  |               |

|               | •                            | compare x conti                        | •                 |                   | ode                    |                  |               |

| bit 12-10     |                              | )>: Output Com                         | pare x Clock S    | elect bits        |                        |                  |               |

|               | 111 = Periph<br>110 = Reserv | eral clock (FP)                        |                   |                   |                        |                  |               |

|               | 101 = PTGO                   |                                        |                   |                   |                        |                  |               |

|               |                              | is the clock so                        |                   |                   | hronous clock          | is supported)    |               |

|               |                              | is the clock so                        |                   |                   |                        |                  |               |

|               |                              | ( is the clock so<br>( is the clock so |                   |                   |                        |                  |               |

|               |                              | is the clock so                        |                   |                   |                        |                  |               |

| bit 9         | Unimplemen                   | ted: Read as '0                        | )'                |                   |                        |                  |               |

| bit 8         | ENFLTB: Fau                  | ult B Input Enab                       | le bit            |                   |                        |                  |               |

|               |                              | compare Fault B<br>compare Fault B     |                   |                   |                        |                  |               |

| bit 7         | -                            | ult A Input Enab                       |                   |                   |                        |                  |               |

|               | 1 = Output C                 | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                        |                  |               |

| bit 6         | •                            | ted: Read as '0                        | • • •             |                   |                        |                  |               |

| bit 5         | OCFLTB: PW                   | M Fault B Con                          | dition Status bit |                   |                        |                  |               |

|               |                              | ult B condition of Fault B condition   |                   |                   |                        |                  |               |

| bit 4         |                              | /M Fault A Cond                        | •                 |                   |                        |                  |               |

|               |                              | ult A condition o                      |                   |                   |                        |                  |               |

| Note 1:       | OCxR and OCxF                | 29 are double h                        | uffered in D\\//  | / mode only       |                        |                  |               |

| Note 1.<br>2: | Each Output Cor              |                                        |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |

| 2.            | Generator (PTG               |                                        |                   |                   |                        | 5.1 2 7.0 1 611p |               |

|               | PTGO4 = OC1                  | -                                      |                   |                   |                        |                  |               |

|               | PTGO5 = OC2                  |                                        |                   |                   |                        |                  |               |

|               | PTGO6 = OC3<br>PTGO7 = OC4   |                                        |                   |                   |                        |                  |               |

|               |                              |                                        |                   |                   |                        |                  |               |

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

- 1 = RX FIFO is empty

- 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       5ID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       -       -       EID17       EID16       bit 0       bit 0         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                                          |                                |               |                  |                  |                 |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|--------------------------------|---------------|------------------|------------------|-----------------|-------|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                          | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       Ignores Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SID10         | SID9                                                                     | SID8                           | SID7          | SID6             | SID5             | SID4            | SID3  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        | ÷                                                                        |                                |               |                  |                  |                 | bit 8 |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                |               |                  |                  |                 |       |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                    | R/W-x                          | U-0           | R/W-x            | U-0              | R/W-x           | R/W-x |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                           | _             | EXIDE            |                  | EID17           | EID16 |