Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XEI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

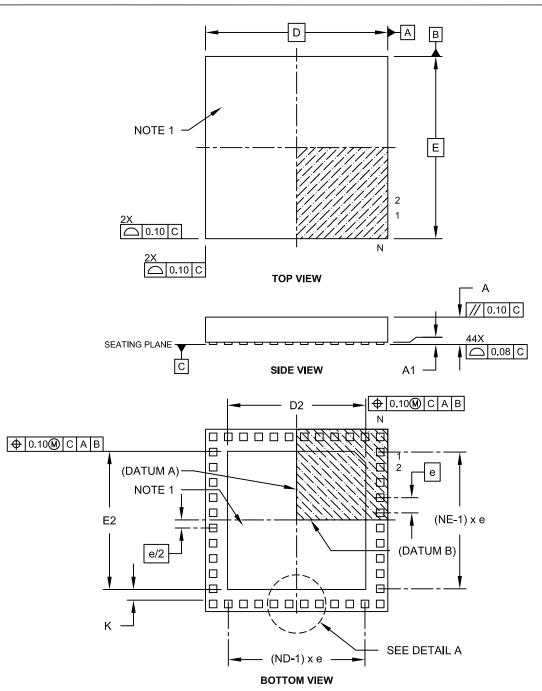

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| IABLE 4   | -10.  | 001    |        | JMPARE   |        |           | OUIFU  |       | ARE 4       | REGIS       |              | <u>٢</u> |        |          |           |          |       |               |

|-----------|-------|--------|--------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|----------|--------|----------|-----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5    | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900  | —      | -      | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS     | 0904  |        |        |          |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC1R      | 0906  |        |        |          |        |           |        |       | Output Co   | mpare 1 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |        |        |          |        |           |        |       | Timer V     | alue 1 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _      | —      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC2RS     | 090E  |        |        |          |        |           |        | Outp  | out Compare | e 2 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC2R      | 0910  |        |        |          |        |           |        |       | Output Co   | mpare 2 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC2TMR    | 0912  |        |        |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC3CON1   | 0914  | _      | —      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |        |        |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC3R      | 091A  |        |        |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |        |        |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _      | -      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922  |        |        |          |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC4R      | 0924  |        |        |          |        |           |        |       | Output Co   | mpare 4 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC4TMR    | 0926  |        |        |          |        |           |        |       | Timer V     | alue 4 Regi | ster         |          |        |          |           |          |       | xxxx          |

# TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4 | Bit 3   | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|--------|---------|---------|-------|-------|--------|----------|-------|---------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | -      | —      | C4EVT  | C3EVT   | C2EVT   | C1EVT | _     | -      | —        | —     | C4OUT   | C3OUT  | C2OUT     | C10UT | 0000          |

| CVRCON                   | 0A82  |        | CVR2OE | _      | _      | _      | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS |         | CVR<   | 3:0>      |       | 0000          |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | 0A8A  |        | _      | _      | _      | _      | _       | _       | _     | _     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM3MSKSRC(1)             | 0A96  | _      | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _      | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | _      | _      |        | _      |        | SELSR   | CC<3:0> | -     |       | SELSRC | B<3:0>   | •     |         | SELSRC | A<3:0>    |       | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      |        | _      | _      | _       | _       | _     | —     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

### TABLE 4-43: CTMU REGISTER MAP

| File N | lame | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------|------|-------|---------|---------|----------|--------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------------|

| CTMUC  | CON1 | 033A  | CTMUEN  | —       | CTMUSIDL | TGEN   | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _     | _       | _     | _     | _     | 0000          |

| CTMUC  | CON2 | 033C  | EDG1MOD | EDG1POL |          | EDG1   | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | EL<3:0> |       | _     | -     | 0000          |

| CTMU   | ICON | 033E  |         |         | ITRIM<5  | 5:0>   |          |          | IRNG     | <1:0>    |         | _       | _     | _     | _       | _     | -     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11           | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|------------------|--------|-------|-------|-------|--------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | —      | _      | _      |                  |        |       |       |       | JDATAH | <27:16> |       |       |       |       |       | xxxx          |

| JDATAL    | 0FF2 |        |        |        |        | JDATAL<15:0> 000 |        |       |       |       |        |         |       | 0000  |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 97

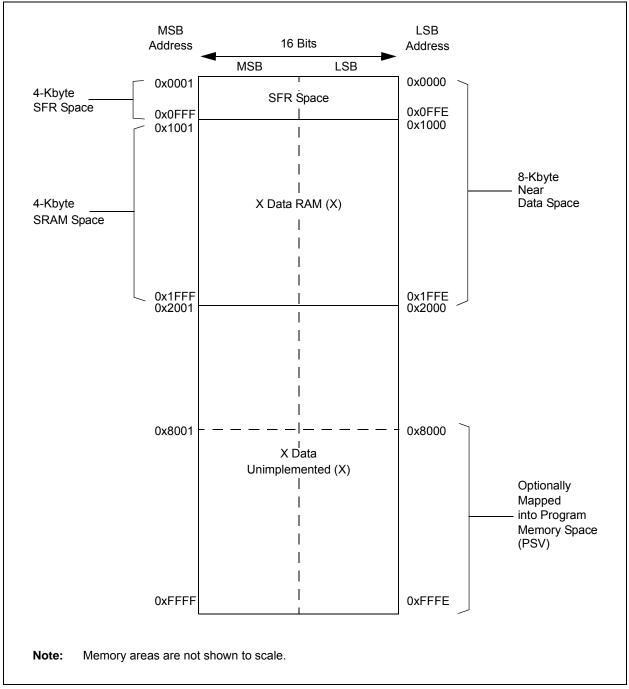

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

NOTES:

### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

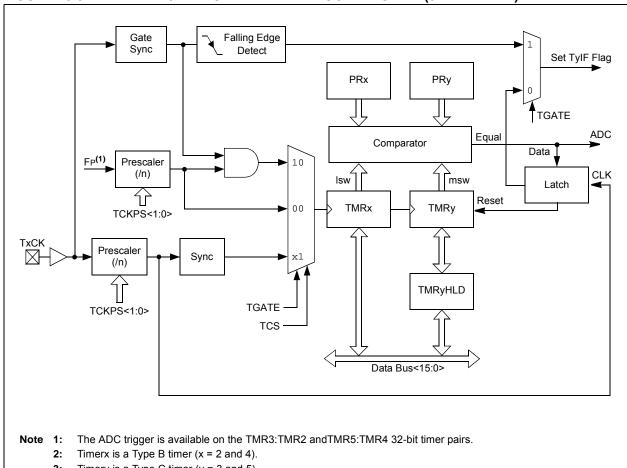

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:<br>R = Readable bi | t     | W = Writable bit |       | U = Unimpler | mented bit, read | l as '0' |       |

|----------------------------|-------|------------------|-------|--------------|------------------|----------|-------|

| bit 7                      |       |                  |       |              |                  |          | bit 0 |

|                            |       |                  | PTPE  | ER<7:0>      |                  |          |       |

| R/W-1                      | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                     |       |                  |       |              |                  |          | bit 8 |

|                            |       |                  | PTPE  | R<15:8>      |                  |          |       |

| R/W-1                      | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0                     | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|---------------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                           |       |                  | SEVTC | MP<15:8>          |                 |                 |       |

| bit 15                    |       |                  |       |                   |                 |                 | bit 8 |

|                           |       |                  |       |                   |                 |                 |       |

| R/W-0                     | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                           |       |                  | SEVT  | CMP<7:0>          |                 |                 |       |

| bit 7                     |       |                  |       |                   |                 |                 | bit 0 |

|                           |       |                  |       |                   |                 |                 |       |

| Legend:                   |       |                  |       |                   |                 |                 |       |

| R = Readable bit W = Writ |       | W = Writable bi  | t     | U = Unimplem      | nented bit, rea | id as '0'       |       |

| -n = Value at POR         |       | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |

|----------------|-------------------------------------|

|                | CONTROL REGISTER                    |

| R/W-0                                     |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|--------------------|--------------|--|--|

|                                           | U-0                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                         | R/W-0                                  | R/W-0             | R/W-0              | R/W-0        |  |  |

| HLMS                                      | —                                                                                                                                                                                                                                                                                                             | OCEN                                                                                                                                                                                                                                                                                             | OCNEN                                                                                                                                                                                                                                                                         | OBEN                                   | OBNEN             | OAEN               | OANEN        |  |  |

| bit 15                                    |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    | bit          |  |  |

| R/W-0                                     | R/W-0                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                         | R/W-0                                  | R/W-0             | R/W-0              | R/W-0        |  |  |

| NAGS                                      | PAGS                                                                                                                                                                                                                                                                                                          | ACEN                                                                                                                                                                                                                                                                                             | ACNEN                                                                                                                                                                                                                                                                         | ABEN                                   | ABNEN             | AAEN               | AANEN        |  |  |

| bit 7                                     |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    | bit          |  |  |

| Legend:                                   |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

| R = Readable                              | bit                                                                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                     | bit                                                                                                                                                                                                                                                                           | U = Unimple                            | mented bit, read  | l as '0'           |              |  |  |

| -n = Value at F                           | POR                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                               | '0' = Bit is cleared                   |                   | x = Bit is unknown |              |  |  |

|                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

| bit 15                                    | HLMS: High                                                                                                                                                                                                                                                                                                    | or Low-Level N                                                                                                                                                                                                                                                                                   | lasking Select                                                                                                                                                                                                                                                                | bits                                   |                   |                    |              |  |  |

|                                           | •                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                  | •                                                                                                                                                                                                                                                                             |                                        | erted ('0') compa | rator signal from  | m propagatin |  |  |

|                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        | erted ('1') compa |                    |              |  |  |

| bit 14                                    | Unimplemen                                                                                                                                                                                                                                                                                                    | ted: Read as                                                                                                                                                                                                                                                                                     | 0'                                                                                                                                                                                                                                                                            |                                        |                   |                    |              |  |  |

| bit 13                                    | OCEN: OR G                                                                                                                                                                                                                                                                                                    | Sate C Input Er                                                                                                                                                                                                                                                                                  | able bit                                                                                                                                                                                                                                                                      |                                        |                   |                    |              |  |  |

|                                           | 1 = MCI is co                                                                                                                                                                                                                                                                                                 | = MCI is connected to OR gate                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|                                           | 0 = MCI is no                                                                                                                                                                                                                                                                                                 | ot connected to                                                                                                                                                                                                                                                                                  | OR gate                                                                                                                                                                                                                                                                       |                                        |                   |                    |              |  |  |

| bit 12                                    | OCNEN: OR Gate C Input Inverted Enable bit                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|                                           | <ul> <li>1 = Inverted MCI is connected to OR gate</li> <li>0 = Inverted MCI is not connected to OR gate</li> </ul>                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                             | jate                                   |                   |                    |              |  |  |

| bit 11                                    | OBEN: OR Gate B Input Enable bit                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|                                           | <ol> <li>1 = MBI is connected to OR gate</li> <li>0 = MBI is not connected to OR gate</li> </ol>                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

|                                           | OBNEN: OR Gate B Input Inverted Enable bit                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

| bit 10                                    |                                                                                                                                                                                                                                                                                                               | Gate B Input I                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                             | ≏ hit                                  |                   |                    |              |  |  |

| bit 10                                    | OBNEN: OR                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                | nverted Enable                                                                                                                                                                                                                                                                |                                        |                   |                    |              |  |  |

| bit 10                                    | <b>OBNEN:</b> OR<br>1 = Inverted I                                                                                                                                                                                                                                                                            | MBI is connect                                                                                                                                                                                                                                                                                   | nverted Enable<br>ed to OR gate                                                                                                                                                                                                                                               |                                        |                   |                    |              |  |  |

| bit 10<br>bit 9                           | <b>OBNEN:</b> OR<br>1 = Inverted I<br>0 = Inverted I                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                | nverted Enable<br>ed to OR gate<br>nected to OR g                                                                                                                                                                                                                             |                                        |                   |                    |              |  |  |

|                                           | <b>OBNEN:</b> OR<br>1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G                                                                                                                                                                                                                                     | MBI is connect<br>MBI is not conr                                                                                                                                                                                                                                                                | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit                                                                                                                                                                                                                |                                        |                   |                    |              |  |  |

|                                           | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is co                                                                                                                                                                                                                                  | MBI is connect<br>MBI is not conr<br>Gate A Input Er                                                                                                                                                                                                                                             | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>gate                                                                                                                                                                                                        |                                        |                   |                    |              |  |  |

|                                           | <b>OBNEN:</b> OR<br>1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G<br>1 = MAI is co<br>0 = MAI is no<br><b>OANEN:</b> OR                                                                                                                                                                               | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>it connected to<br>Gate A Input I                                                                                                                                                                                       | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>gate<br>OR gate<br>nverted Enable                                                                                                                                                                           | jate<br>e bit                          |                   |                    |              |  |  |

| bit 9                                     | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is co<br>0 = MAI is no<br>OANEN: OR<br>1 = Inverted I                                                                                                                                                                                  | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>it connected to<br>Gate A Input I<br>MAI is connect                                                                                                                                                                     | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>OR gate<br>Nverted Enable<br>ed to OR gate                                                                                                                                                                  | jate<br>e bit                          |                   |                    |              |  |  |

| bit 9<br>bit 8                            | <b>OBNEN:</b> OR<br>1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G<br>1 = MAI is co<br>0 = MAI is no<br><b>OANEN:</b> OR<br>1 = Inverted I<br>0 = Inverted I                                                                                                                                           | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>t connected to<br>Gate A Input I<br>MAI is connect<br>MAI is not conr                                                                                                                                                   | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>gate<br>OR gate<br>nverted Enable<br>ed to OR gate<br>nected to OR g                                                                                                                                        | gate<br>e bit<br>gate                  |                   |                    |              |  |  |

| bit 9                                     | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is co<br>0 = MAI is no<br>OANEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>NAGS: AND                                                                                                                                                   | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>t connected to<br>Gate A Input I<br>MAI is connect<br>MAI is not conr<br>Gate Output Ir                                                                                                                                 | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>gate<br>OR gate<br>nverted Enable<br>nected to OR gate<br>nected to OR g                                                                                                                                    | gate<br>e bit<br>gate<br>e bit         |                   |                    |              |  |  |

| bit 9<br>bit 8                            | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is co<br>0 = MAI is no<br>OANEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>NAGS: AND<br>1 = Inverted I                                                                                                                                 | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>t connected to<br>Gate A Input I<br>MAI is connect<br>MAI is not conr<br>Gate Output Ir<br>ANDI is connect                                                                                                              | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>gate<br>OR gate<br>nverted Enable<br>nected to OR gate<br>nected to OR gate                                                                                                                                 | gate<br>e bit<br>gate<br>e bit<br>e    |                   |                    |              |  |  |

| bit 9<br>bit 8<br>bit 7                   | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is no<br>OANEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>NAGS: AND<br>1 = Inverted I<br>0 = Inverted I                                                                                                                                | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>t connected to<br>Gate A Input I<br>MAI is connect<br>MAI is not conr<br>Gate Output Ir<br>ANDI is connect<br>ANDI is not con                                                                                           | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>OR gate<br>nverted Enable<br>nverted Enable<br>nverted Enable<br>nverted Enable<br>the to OR gate                                                                                                           | gate<br>e bit<br>gate<br>e bit<br>e    |                   |                    |              |  |  |

| bit 9<br>bit 8<br>bit 7                   | OBNEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>OAEN: OR G<br>1 = MAI is no<br>OANEN: OR<br>1 = Inverted I<br>0 = Inverted I<br>NAGS: AND<br>1 = Inverted A<br>0 = Inverted A                                                                                                                                | MBI is connect<br>MBI is not conr<br>Gate A Input Er<br>nnected to OR<br>t connected to<br>Gate A Input I<br>MAI is connect<br>MAI is not conr<br>Gate Output Ir<br>ANDI is connect                                                                                                              | nverted Enable<br>ed to OR gate<br>nected to OR g<br>nable bit<br>OR gate<br>nverted Enable<br>ed to OR gate<br>nected to OR g<br>nverted Enable<br>cted to OR gat<br>nnected to OR gat<br>nnected to OR gat                                                                  | gate<br>e bit<br>gate<br>e bit<br>e    |                   |                    |              |  |  |