Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

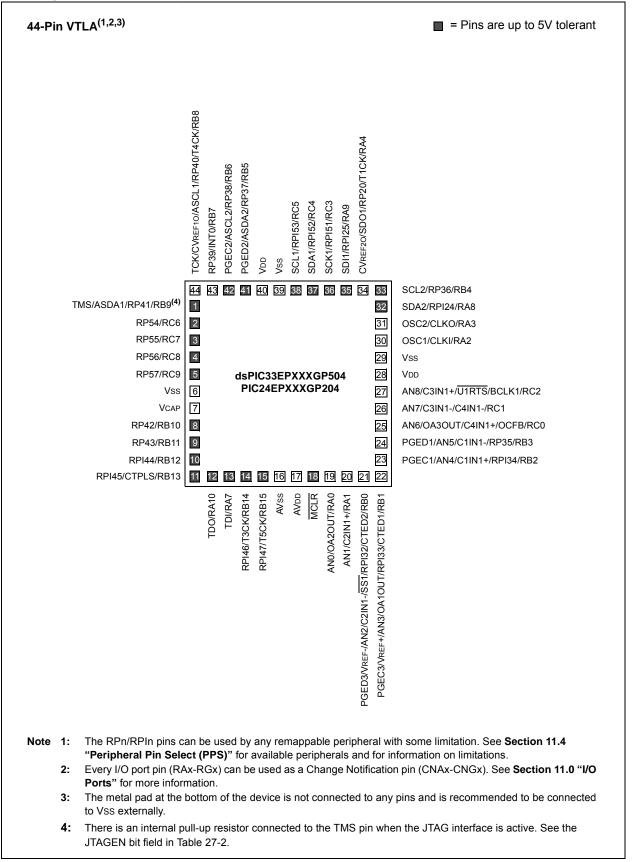

#### **Pin Diagrams (Continued)**

| TABLE        | 4-2:  | CPU C             | CORE RE   | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|-------------------|-----------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15            | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |                   | W0 (WREG) |         |         |         |        |       |          |          |        |       | xxxx      |          |       |       |       |               |

| W1           | 0002  |                   | W1 :      |         |         |         |        |       |          |          |        |       | xxxx      |          |       |       |       |               |

| W2           | 0004  |                   |           |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |                   |           |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |                   |           |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |                   |           |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |                   |           |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |                   |           |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |                   |           |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |                   |           |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |                   |           |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |                   |           |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |                   |           |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |                   |           |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |                   |           |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |                   |           |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |                   |           |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |                   |           |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —                 | -         | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —                 | -         | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _                 |           |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |                   |           |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _                 |           |         |         | —       |        | _     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR               | _         | -       | -       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _                 | _         |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _                 | _         | -       | -       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  | MSTRPR<15:0> 0000 |           |         |         |         |        |       |          |          | 0000   |       |           |          |       |       |       |               |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: ADC1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8        | Bit 7    | Bit 6    | Bit 5    | Bit 4     | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|-----------------------|--------|---------|--------|-----------|---------|--------------|----------|----------|----------|-----------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 0  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 1  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 2  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 3  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308  |        | ADC1 Data Buffer 4 x2 |        |         |        |           |         |              |          |          | xxxx     |           |        |          |         |         |               |

| ADC1BUF5  | 030A  |        | ADC1 Data Buffer 5 x2 |        |         |        |           |         |              |          | xxxx     |          |           |        |          |         |         |               |

| ADC1BUF6  | 030C  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 6  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 7  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |                       |        |         |        |           |         | ADC1 Data B  | uffer 8  |          |          |           |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312  |        | ADC1 Data Buffer 9 x  |        |         |        |           |         |              |          | xxxx     |          |           |        |          |         |         |               |

| ADC1BUFA  | 0314  |        |                       |        |         |        |           |         | ADC1 Data Bu | Iffer 10 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |                       |        |         |        |           |         | ADC1 Data Bu | uffer 11 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |                       |        |         |        |           |         | ADC1 Data Bu | Iffer 12 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |                       |        |         |        |           |         | ADC1 Data Bu | Iffer 13 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |                       |        |         |        |           |         | ADC1 Data Bu | Iffer 14 |          |          |           |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |                       |        |         |        |           |         | ADC1 Data Bu | iffer 15 |          |          |           |        |          |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | _                     | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>       | Ş        | SRC<2:0> | <b>`</b> | SSRCG     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  | ١      | VCFG<2:0>             | >      | _       | _      | CSCNA     | CHP     | S<1:0>       | BUFS     |          |          | SMPI<4:0> | >      |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _                     | _      |         |        | SAMC<4:03 | >       |              |          |          |          | ADCS      | <7:0>  |          |         |         | 0000          |

| AD1CHS123 | 0326  | _      | _                     | _      | _       | _      | CH123N    | NB<1:0> | CH123SB      | —        | _        | —        | _         | _      | CH123N   | A<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | _                     | _      |         |        | CH0SB<4:0 | >       |              | CH0NA    | _        | —        |           | С      | H0SA<4:0 | >       |         | 0000          |

| AD1CSSH   | 032E  | CSS31  | CSS30                 | _      | _       |        | CSS26     | CSS25   | CSS24        | _        |          | _        | —         | —      | —        | —       | —       | 0000          |

| AD1CSSL   | 0330  | CSS15  | CSS14                 | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8         | CSS7     | CSS6     | CSS5     | CSS4      | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

| AD1CON4   | 0332  |        | _                     | _      | _       |        | _         | _       | ADDMAEN      | -        |          |          |           | _      | D        | MABL<2: | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

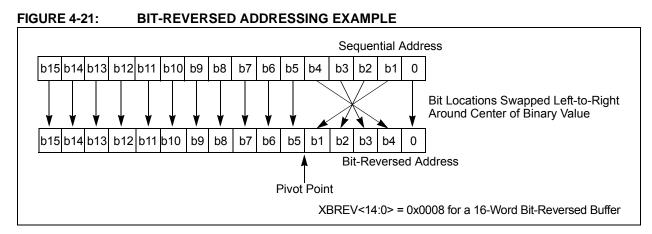

### TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |  |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|--|--|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| R/W-0                  | R/W-0                                                                                                                              | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | R/W-0                |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------|--------------------------------------|-----------------------|----------------------|----------------------|--|

| NSTDIS                 | OVAERR <sup>(1)</sup>                                                                                                              | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup>            | COVBERR <sup>(1)</sup>               | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |  |

| pit 15                 |                                                                                                                                    |                       |                                   |                                      |                       |                      | bit 8                |  |

|                        |                                                                                                                                    |                       |                                   |                                      |                       |                      |                      |  |

| R/W-0                  | R/W-0                                                                                                                              | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | U-0                  |  |

| SFTACERR <sup>(1</sup> | ) DIV0ERR                                                                                                                          | DMACERR               | MATHERR                           | ADDRERR                              | STKERR                | OSCFAIL              | —                    |  |

| pit 7                  |                                                                                                                                    |                       |                                   |                                      |                       |                      | bit 0                |  |

|                        |                                                                                                                                    |                       |                                   |                                      |                       |                      |                      |  |

| _egend:                |                                                                                                                                    |                       |                                   |                                      |                       |                      |                      |  |

| R = Readable           |                                                                                                                                    | W = Writable          |                                   | U = Unimpleme                        |                       |                      |                      |  |

| n = Value at           | POR                                                                                                                                | '1' = Bit is set      |                                   | '0' = Bit is clear                   | ed                    | x = Bit is unk       | nown                 |  |

| bit 15                 | NSTDIS: Inte                                                                                                                       | errupt Nesting        | Disable hit                       |                                      |                       |                      |                      |  |

|                        |                                                                                                                                    | nesting is disa       |                                   |                                      |                       |                      |                      |  |

|                        | •                                                                                                                                  | nesting is ena        |                                   |                                      |                       |                      |                      |  |

| pit 14                 | -                                                                                                                                  | -                     | Overflow Trap F                   | lag bit <sup>(1)</sup>               |                       |                      |                      |  |

|                        |                                                                                                                                    |                       | erflow of Accur                   |                                      |                       |                      |                      |  |

|                        | =                                                                                                                                  |                       | overflow of A                     |                                      |                       |                      |                      |  |

| pit 13                 |                                                                                                                                    |                       | Overflow Trap F                   | •                                    |                       |                      |                      |  |

|                        | <ul> <li>1 = Trap was caused by overflow of Accumulator B</li> <li>0 = Trap was not caused by overflow of Accumulator B</li> </ul> |                       |                                   |                                      |                       |                      |                      |  |

| pit 12                 | -                                                                                                                                  |                       |                                   | Overflow Trap Fla                    | ag bit <sup>(1)</sup> |                      |                      |  |

|                        | 1 = Trap was                                                                                                                       | caused by ca          | tastrophic over                   | flow of Accumula                     | ator A                |                      |                      |  |

| pit 11                 |                                                                                                                                    |                       |                                   | Overflow Trap Fla                    |                       |                      |                      |  |

|                        |                                                                                                                                    |                       | •                                 | flow of Accumula                     | •                     |                      |                      |  |

|                        | =                                                                                                                                  |                       | -                                 | overflow of Accur                    | nulator B             |                      |                      |  |

| pit 10                 |                                                                                                                                    |                       | erflow Trap Ena                   | able bit <sup>(1)</sup>              |                       |                      |                      |  |

|                        | 1 = Trap ove<br>0 = Trap is d                                                                                                      | rflow of Accum        | ulator A                          |                                      |                       |                      |                      |  |

| pit 9                  | OVBTE: Acc                                                                                                                         | umulator B Ov         | erflow Trap En                    | able bit <sup>(1)</sup>              |                       |                      |                      |  |

|                        | 1 = Trap ove<br>0 = Trap is d                                                                                                      | rflow of Accum        | ulator B                          |                                      |                       |                      |                      |  |

| oit 8                  | COVTE: Cat                                                                                                                         | astrophic Over        | flow Trap Enat                    | ole bit <sup>(1)</sup>               |                       |                      |                      |  |

|                        | 1 = Trap on o<br>0 = Trap is d                                                                                                     |                       | erflow of Accu                    | mulator A or B is                    | enabled               |                      |                      |  |

| oit 7                  | SFTACERR:                                                                                                                          | Shift Accumul         | ator Error Statu                  | us bit <sup>(1)</sup>                |                       |                      |                      |  |

|                        |                                                                                                                                    | •                     | •                                 | alid accumulator<br>invalid accumula |                       |                      |                      |  |

| oit 6                  | DIV0ERR: D                                                                                                                         | ivide-by-Zero I       | Error Status bit                  |                                      |                       |                      |                      |  |

|                        |                                                                                                                                    |                       | used by a divide<br>caused by a d |                                      |                       |                      |                      |  |

|                        | DMACERR:                                                                                                                           |                       |                                   | -                                    |                       |                      |                      |  |

| oit 5                  |                                                                                                                                    |                       |                                   |                                      |                       |                      |                      |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                                                                                                                              | R-0                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|--|

| _              | COSC2                                                                                                                                                                            | COSC1                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |  |

| bit 15         |                                                                                                                                                                                  |                                      |                                    |                                    |                                    |                      | bit 8                |  |  |  |  |

| R/W-0          | R/W-0                                                                                                                                                                            | R-0                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |  |

| CLKLOC         | CK IOLOCK                                                                                                                                                                        | LOCK                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |  |

| bit 7          |                                                                                                                                                                                  |                                      |                                    |                                    |                                    |                      | bit (                |  |  |  |  |

| Legend:        |                                                                                                                                                                                  | y = Value set                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |  |

| R = Reada      | able bit                                                                                                                                                                         | W = Writable                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |  |

| -n = Value     | at POR                                                                                                                                                                           | '1' = Bit is se                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |  |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                                                                                                                                                       | ted. Dood oo                         | 0'                                 |                                    |                                    |                      |                      |  |  |  |  |

| bit 15         | -                                                                                                                                                                                | ted: Read as                         |                                    |                                    |                                    |                      |                      |  |  |  |  |

| bit 14-12      |                                                                                                                                                                                  | Current Oscill                       |                                    |                                    | /)                                 |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | C Oscillator (F<br>C Oscillator (F   |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | ower RC Oscil                        |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | 100 = Reserved                       |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | y Oscillator (X                      |                                    | h PLL                              |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | y Oscillator (X                      |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | C Oscillator (F<br>C Oscillator (F   |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |

| bit 11         |                                                                                                                                                                                  | ted: Read as                         | ,                                  |                                    |                                    |                      |                      |  |  |  |  |

| bit 10-8       | NOSC<2:0>:                                                                                                                                                                       | New Oscillato                        | r Selection bits                   | <sub>S</sub> (2)                   |                                    |                      |                      |  |  |  |  |

|                | 111 = Fast R                                                                                                                                                                     | C Oscillator (F                      | RC) with Divid                     | le-by-n                            |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | C Oscillator (F                      |                                    | le-by-16                           |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | ower RC Oscil                        | ator (LPRC)                        |                                    |                                    |                      |                      |  |  |  |  |

|                | 100 = Reserv                                                                                                                                                                     | /ed<br>y Oscillator (X               |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | y Oscillator (X                      |                                    | IFLL                               |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | C Oscillator (F                      |                                    | le-by-N and Pl                     | LL (FRCPLL)                        |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | C Oscillator (F                      |                                    | ,                                  | ,                                  |                      |                      |  |  |  |  |

| bit 7          |                                                                                                                                                                                  | Clock Lock Ena                       |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  |                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |  |

|                |                                                                                                                                                                                  | figurations may<br>d PLL selectio    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |  |

| bit 6          |                                                                                                                                                                                  | Lock Enable b                        |                                    | -                                  | -                                  |                      |                      |  |  |  |  |

|                | 1 = I/O lock is                                                                                                                                                                  | s active                             |                                    |                                    |                                    |                      |                      |  |  |  |  |

|                | 0 = I/O lock is                                                                                                                                                                  | s not active                         |                                    |                                    |                                    |                      |                      |  |  |  |  |

| bit 5          | LOCK: PLL L                                                                                                                                                                      | ock Status bit                       | (read-only)                        |                                    |                                    |                      |                      |  |  |  |  |

|                |                                                                                                                                                                                  | s that PLL is in<br>s that PLL is ou |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |  |

| Note 1:        | Writes to this regis                                                                                                                                                             |                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |  |

| 2:             | Direct clock switch<br>This applies to clo                                                                                                                                       | es between ar<br>ck switches in      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |  |

| 0              | mode as a transitional clock source between the two PLL modes. 3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an |                                      |                                    |                                    |                                    |                      |                      |  |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

NOTES:

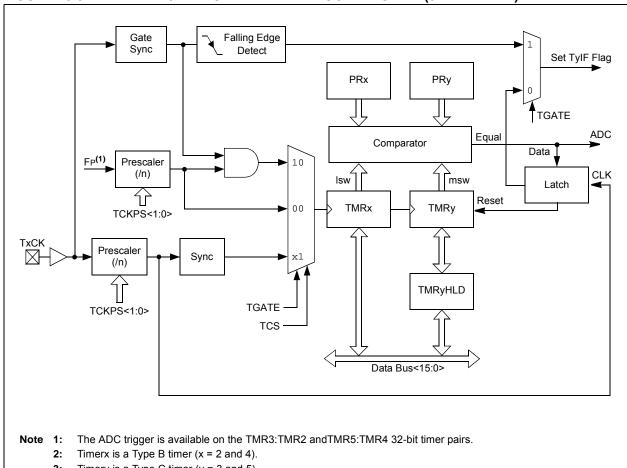

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ble bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

### REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

| U-0                                 | U-0                                                                                                    | U-0                                                                                                                                   | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|--|--|--|

| —                                   | —                                                                                                      | _                                                                                                                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15                              |                                                                                                        |                                                                                                                                       |                      |                                        |                      |                      | bit                  |  |  |  |

| <b>D M M A</b>                      | <b>D</b> 444 0                                                                                         | DAMA                                                                                                                                  | <b>D M ( 0</b>       | <b>D</b> 444 0                         | Dates                | Dates                | <b>D</b> 444 0       |  |  |  |

| R/W-0                               | R/W-0                                                                                                  | R/W-0                                                                                                                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup>                 | CKP                                                                                                    | MSTEN                                                                                                                                 | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3</sup>  |  |  |  |

| bit 7                               |                                                                                                        |                                                                                                                                       |                      |                                        |                      |                      | bit                  |  |  |  |

| Legend:                             |                                                                                                        |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

| R = Readabl                         | e bit                                                                                                  | W = Writable                                                                                                                          | bit                  | U = Unimpler                           | mented bit, read     | l as '0'             |                      |  |  |  |

| -n = Value at                       | POR                                                                                                    | '1' = Bit is se                                                                                                                       | t                    | '0' = Bit is cle                       |                      | x = Bit is unkr      | nown                 |  |  |  |

|                                     |                                                                                                        |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

| bit 15-13                           | Unimplemen                                                                                             | ted: Read as                                                                                                                          | 0'                   |                                        |                      |                      |                      |  |  |  |

| bit 12                              | DISSCK: Disa                                                                                           | able SCKx Pin                                                                                                                         | bit (SPIx Mas        | ter modes only                         | /)                   |                      |                      |  |  |  |

|                                     | 1 = Internal S                                                                                         | Plx clock is di                                                                                                                       | sabled, pin fun      | -                                      |                      |                      |                      |  |  |  |

|                                     | 0 = Internal S                                                                                         | PIx clock is er                                                                                                                       | abled                |                                        |                      |                      |                      |  |  |  |

| bit 11 DISSDO: Disable SDOx Pin bit |                                                                                                        |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 1 = SDOx pin is not used by the module; pin functions as I/O                                           |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 0 = SDOx pin is controlled by the module                                                               |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

| bit 10                              | MODE16: Word/Byte Communication Select bit                                                             |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 1 = Communication is word-wide (16 bits)<br>0 = Communication is byte-wide (8 bits)                    |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

| bit 9                               |                                                                                                        | •                                                                                                                                     | . ,                  |                                        |                      |                      |                      |  |  |  |

| bit 5                               | SMP: SPIx Data Input Sample Phase bit<br>Master mode:                                                  |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     |                                                                                                        | <u>.</u><br>a is sampled at                                                                                                           | end of data o        | utput time                             |                      |                      |                      |  |  |  |

|                                     |                                                                                                        | a is sampled at                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | Slave mode:                                                                                            |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     |                                                                                                        |                                                                                                                                       |                      | n Slave mode.                          |                      |                      |                      |  |  |  |

| bit 8                               |                                                                                                        | lock Edge Sele                                                                                                                        |                      |                                        |                      |                      |                      |  |  |  |

|                                     |                                                                                                        |                                                                                                                                       |                      |                                        | clock state to Id    |                      |                      |  |  |  |

| bit 7                               |                                                                                                        |                                                                                                                                       |                      |                                        | ock state to activ   |                      |                      |  |  |  |

|                                     | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     |                                                                                                        |                                                                                                                                       |                      | is controlled b                        | ov port function     |                      |                      |  |  |  |

| bit 6                               |                                                                                                        | <ul> <li>0 = SSx pin is not used by the module; pin is controlled by port function</li> <li>CKP: Clock Polarity Select bit</li> </ul> |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 1 = Idle state                                                                                         | for clock is a h                                                                                                                      | nigh level; activ    | ve state is a lov<br>e state is a higl |                      |                      |                      |  |  |  |

| bit 5                               | 0 = Idle state for clock is a low level; active state is a high level<br>MSTEN: Master Mode Enable bit |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 1 = Master m                                                                                           |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

|                                     | 0 = Slave mo                                                                                           | de                                                                                                                                    |                      |                                        |                      |                      |                      |  |  |  |

| <b>Note 1:</b> ⊺h                   | he CKE bit is not                                                                                      | used in Frame                                                                                                                         | d SPI modes I        | Program this hi                        | it to '0' for Fram   | ed SPI modes (       | FRMEN = <sup>-</sup> |  |  |  |

|                                     | his bit must be cl                                                                                     |                                                                                                                                       |                      |                                        |                      |                      |                      |  |  |  |

| <b>2</b> . 11                       |                                                                                                        |                                                                                                                                       | · · ·                |                                        |                      |                      |                      |  |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                             | R/W-0    | R/W-0            | U-0             | R/W-0, HC                          | R/W-0                | R-0             | R-1   |

|-----------------------------------|----------|------------------|-----------------|------------------------------------|----------------------|-----------------|-------|

| UTXISEL1                          | UTXINV   | UTXISEL0         | —               | UTXBRK                             | UTXEN <sup>(1)</sup> | UTXBF           | TRMT  |

| bit 15                            |          |                  |                 |                                    |                      |                 | bit 8 |

|                                   |          |                  |                 |                                    |                      |                 |       |

| R/W-0                             | R/W-0    | R/W-0            | R-1             | R-0                                | R-0                  | R/C-0           | R-0   |

| URXISEL1                          | URXISEL0 | ADDEN            | RIDLE           | PERR                               | FERR                 | OERR            | URXDA |

| bit 7                             |          |                  |                 |                                    |                      |                 | bit C |

|                                   |          |                  |                 |                                    |                      |                 |       |

| Legend:                           |          | HC = Hardward    | e Clearable bit | C = Clearable                      | e bit                |                 |       |

| R = Readable bit W = Writable bit |          |                  | bit             | U = Unimplemented bit, read as '0' |                      |                 |       |

| -n = Value at POR '1' = Bit i     |          | '1' = Bit is set |                 | '0' = Bit is cleared               |                      | x = Bit is unkr | nown  |

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed