Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Dectano                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504t-e-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

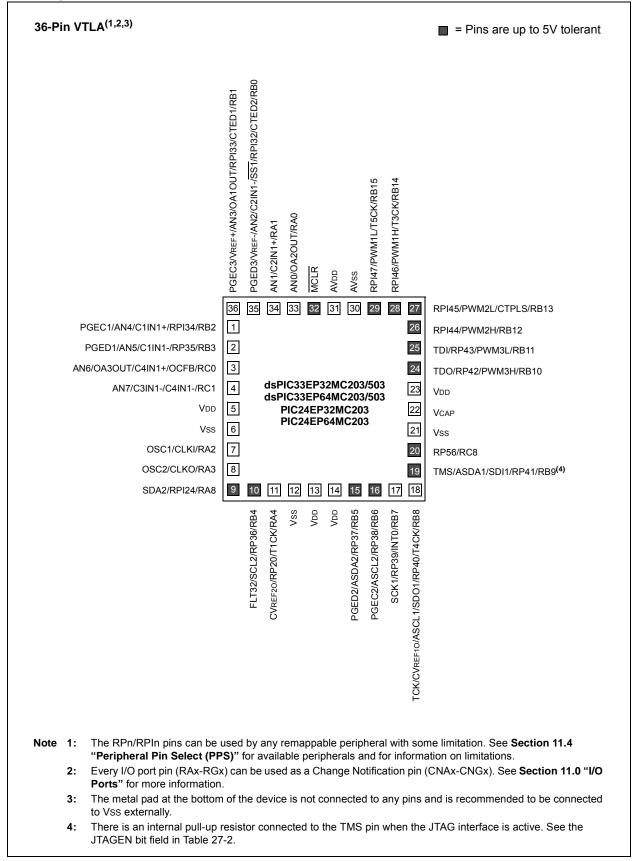

# Pin Diagrams (Continued)

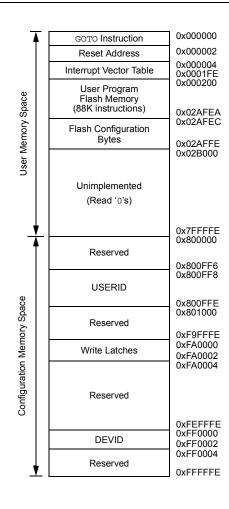

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

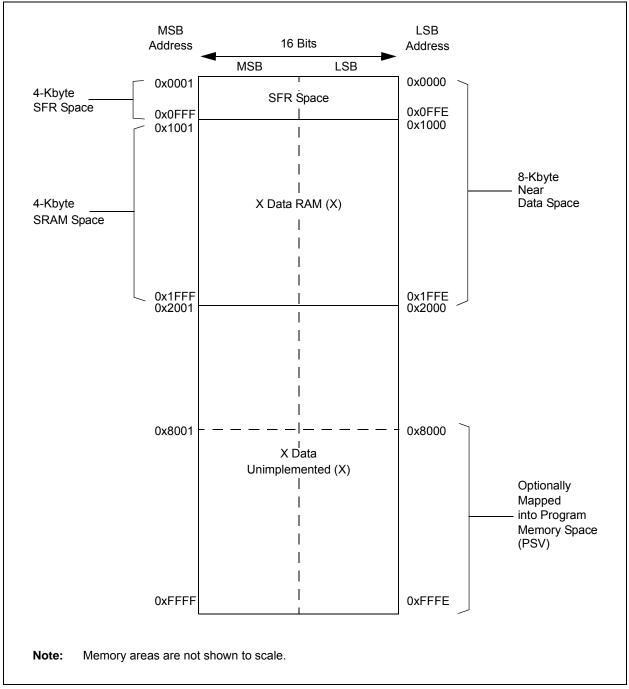

Note: Memory areas are not shown to scale.

| TABLE 4   | 4-9:  | INPUT  |                                                        | JRE 1 T | HROUG  | H INPU                                   | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |          |       |       |          |          |       |               |

|-----------|-------|--------|--------------------------------------------------------|---------|--------|------------------------------------------|--------|-------|--------------|--------------|----------|----------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                 | Bit 13  | Bit 12 | Bit 11                                   | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —                                                      | ICSIDL  | 10     | ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> |        |       |              |              |          | ICM<2:0> |       | 0000  |          |          |       |               |

| IC1CON2   | 0142  | _      | _                                                      |         | _      |                                          | —      | —     | IC32         | ICTRIG       | TRIGSTAT |          |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |                                                        |         |        |                                          |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |          |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        | Input Capture 1 Timer 0000                             |         |        |                                          |        |       |              |              |          |          |       |       |          |          |       |               |

| IC2CON1   | 0148  |        | - ICSIDL ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> 0000 |         |        |                                          |        |       |              |              |          | 0000     |       |       |          |          |       |               |

| IC2CON2   | 014A  |        | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> 00                 |         |        |                                          |        |       |              |              | 000D     |          |       |       |          |          |       |               |

| IC2BUF    | 014C  |        |                                                        |         |        |                                          |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |          |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |                                                        |         |        |                                          |        |       | Input Capt   | ture 2 Time  | r        |          |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _                                                      | ICSIDL  | 10     | CTSEL<2:0                                | >      | —     | _            |              | ICI<1    | :0>      | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _                                                      |         |        |                                          | —      | —     | IC32         | ICTRIG       | TRIGSTAT |          |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |                                                        |         |        |                                          |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |          |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |                                                        |         |        |                                          |        |       | Input Capt   | ture 3 Time  | r        |          |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _                                                      | ICSIDL  | 10     | CTSEL<2:0                                | >      | —     | _            |              | ICI<1    | :0>      | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> 000D               |         |        |                                          |        |       |              |              | 000D     |          |       |       |          |          |       |               |

| IC4BUF    | 015C  |        | Input Capture 4 Buffer Register xxx                    |         |        |                                          |        |       |              |              |          | xxxx     |       |       |          |          |       |               |

| IC4TMR    | 015E  |        | Input Capture 4 Timer 0000                             |         |        |                                          |        |       |              |              |          |          |       |       |          |          |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6      | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|------------|------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |        | RP35R<5:0> |        |        |       | _     | —          | RP20R<5:0> |            |       |       |        |       | 0000  |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       | _     | _          |            |            | RP36F | <5:0> |        |       | 0000  |               |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        | _     | _     | RP38R<5:0> |            |            |       |       | 0000   |       |       |               |

| RPOR3        | 0686  | _      | _      |        |            | RP41   | R<5:0> |       |       | _          | _          | RP40R<5:0> |       |       |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        |            | RP43   | R<5:0> |       |       | _          | _          | RP42R<5:0> |       |       |        |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0> |        |        |       | _     | —          | RP54R<5:0> |            |       |       |        | 0000  |       |               |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       |       | _          | —          |            |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|------------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0>  |        |        |       | _     | _     | RP20R<5:0> |            |       |        |        | •     | 0000  |               |

| RPOR1        | 0682  | _      |        |        | RP37R<5:0>  |        |        |       | _     | _     |            | RP36R<5:0> |       |        |        |       | 0000  |               |

| RPOR2        | 0684  | _      | —      |        | RP39R<5:0>  |        |        |       | _     | _     | RP38R<5:0> |            |       |        |        | 0000  |       |               |

| RPOR3        | 0686  | _      | —      |        | RP41R<5:0>  |        |        |       | _     | _     |            |            | RP40  | R<5:0> |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | २<5:0> |       |       | —     | _          |            |       | RP42   | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | २<5:0> |       |       | —     | _          | RP54R<5:0> |       |        |        |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |             | RP57F  | २<5:0> |       |       | —     | _          |            |       | RP56   | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        | —     | _     | _     | _          | _          | _     | _      | _      | 0000  |       |               |

| RPOR8        | 0690  |        | _      |        | RP118R<5:0> |        |        | _     | _     | —     | _          | —          | _     | —      | _      | 0000  |       |               |

| RPOR9        | 0692  | —      | _      | _      | _           | _      | _      | _     | _     | _     |            |            |       |        |        | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:      |         |                                                                                       |                                    |                    |  |  |  |  |

|--------------|---------|---------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readat   | ole bit | W = Writable bit                                                                      | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value a | at POR  | '1' = Bit is set                                                                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15 1     | Unimplo | mented: Read as '0'                                                                   |                                    |                    |  |  |  |  |

| •            |         | DMA Channel 3 Ping-Pong I                                                             | Modo Status Elag bit               |                    |  |  |  |  |

| bit 5        | 1 = DMA | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit              |                    |  |  |  |  |

| bit 2        | 1 = DMA | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit               |                    |  |  |  |  |

| bit 1        | PPST1:  | DMA Channel 1 Ping-Pong I                                                             | Mode Status Flag bit               |                    |  |  |  |  |

|              |         | CTD1 register is calested                                                             |                                    |                    |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

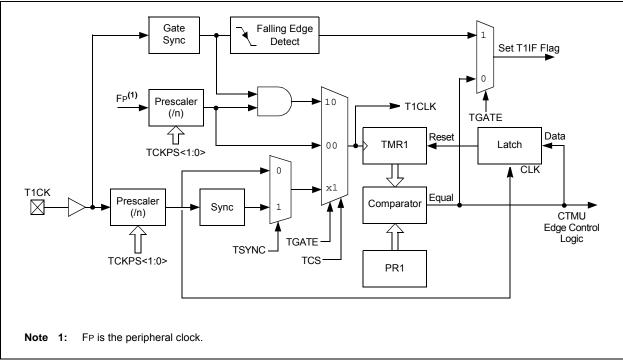

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### TABLE 12-1: TIMER MODE SETTINGS

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

# 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

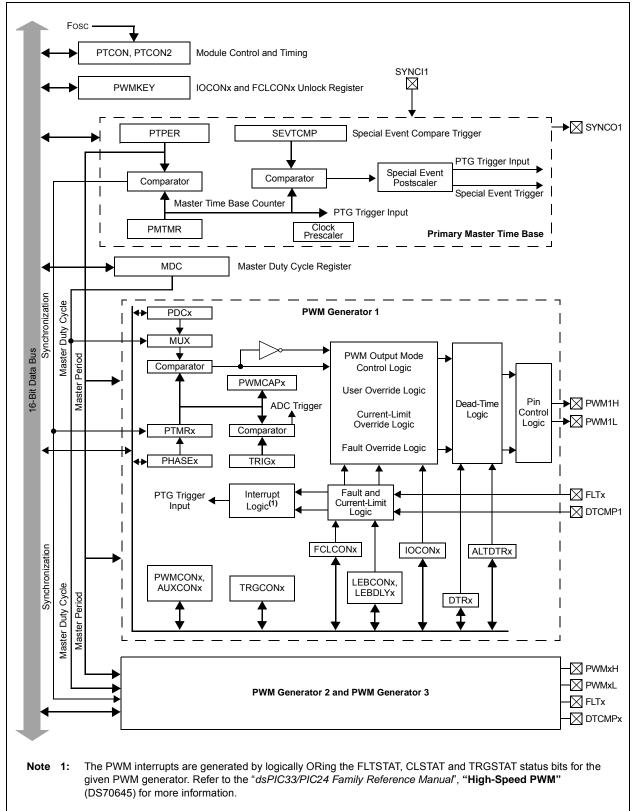

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

# 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x                              | R/W-x | R/W-x | R/W-x |  |  |  |  |  |

|---------------|---------------------------|-------------------|---------------|------------------------------------|-------|-------|-------|--|--|--|--|--|

|               | —                         | _                 | SID10         | SID9                               | SID8  | SID7  | SID6  |  |  |  |  |  |

| bit 15        |                           |                   |               |                                    |       |       | bit 8 |  |  |  |  |  |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x                              | R/W-x | R/W-x | R/W-x |  |  |  |  |  |

| SID5          | SID4                      | SID3              | SID2          | SID1                               | SID0  | SRR   | IDE   |  |  |  |  |  |

| bit 7         |                           |                   |               |                                    | •     |       | bit 0 |  |  |  |  |  |

| Legend:       |                           |                   |               |                                    |       |       |       |  |  |  |  |  |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |  |  |

| -n = Value at | POR                       | '1' = Bit is set  |               | '0' = Bit is cle                   | nown  |       |       |  |  |  |  |  |

|               |                           |                   |               |                                    |       |       |       |  |  |  |  |  |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                                    |       |       |       |  |  |  |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                                    |       |       |       |  |  |  |  |  |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                                    |       |       |       |  |  |  |  |  |

|               | When IDE =                | 0:                |               |                                    |       |       |       |  |  |  |  |  |

|               | 1 = Message               | will request rer  | note transmis | ssion                              |       |       |       |  |  |  |  |  |

|               | 0 = Normal m              | nessage           |               |                                    |       |       |       |  |  |  |  |  |

|               | When IDE = 1              | <u>1:</u>         |               |                                    |       |       |       |  |  |  |  |  |

|               | The SRR bit r             | must be set to '  | 1'.           |                                    |       |       |       |  |  |  |  |  |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                                    |       |       |       |  |  |  |  |  |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier                              |       |       |       |  |  |  |  |  |

|               | 0 = Message               | will transmit St  | andard Identi | fier                               |       |       |       |  |  |  |  |  |

|               |                           |                   |               |                                    |       |       |       |  |  |  |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                                | U-0   | U-0            | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|--|

| —                                  | —     | —              |       | EID17                                   | EID16 | EID15 | EID14 |  |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |  |

|                                    |       |                |       |                                         |       |       |       |  |  |

| R/W-x                              | R/W-x | R/W-x          | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| EID13                              | EID12 | EID11          | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |  |

| bit 7                              |       |                |       |                                         |       |       | bit 0 |  |  |

|                                    |       |                |       |                                         |       |       |       |  |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |  |

| R = Readable                       | bit   | W = Writable I | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

| L                                  |       |                |       |                                         |       |       |       |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

# 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | -0.3V to +3.6V       |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                      |

| Maximum current sunk/sourced by any 4x I/O pin                                    | 15 mA                |

| Maximum current sunk/sourced by any 8x I/O pin                                    | 25 mA                |

| Maximum current sunk by all ports <sup>(2,4)</sup>                                | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: dsPIC33EPXXXGP502, dsPIC33EPXXXMC202/502 and PIC24EPXXXGP/MC202 devices, which have a maximum sink/source capability of 130 mA.

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                                                        |  |

|--------------------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                                                              | Тур. | Max. | Units | Conditions                                                                                                                                                             |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                   |      | 0.4  | V     | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                 |      | 0.4  | V     |                                                                                                                                                                        |  |

| DO20 V             | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                               |      | _    | V     | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                               | _    | —    | V     | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

| DO20A              | Von1   |                                                             | 1.5(1)                                                                                                                                                                                                                                                                            | _    |      | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                | _    | —    |       | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                            |      | —    |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                    |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                | —    | —    | V     | $IOH \geq -22  mA,  VDD = 3.3  V$                                                                                                                                      |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                | —    | —    |       | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                          |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                            | —    | —    | 1     | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                          |  |

# TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

## TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                        |

|--------------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                             | Min. <sup>(2)</sup>                                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                                                                                                                                                                                                                                                          | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

3: The VBOR specification is relative to VDD.

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                                                                                                                                   |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended<br>Operating voltage VDD range as described in <b>Section 30.1 "DC</b> |  |  |  |  |  |

|                    | Characteristics".                                                                                                                                                                                       |  |  |  |  |  |

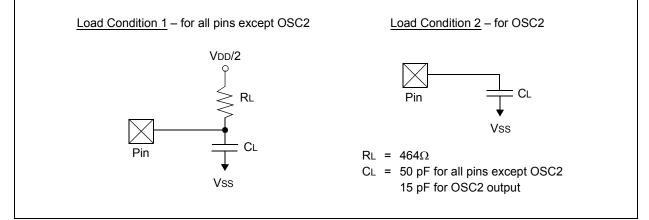

## FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | _    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

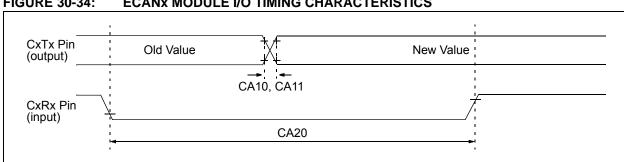

#### FIGURE 30-34: ECANx MODULE I/O TIMING CHARACTERISTICS

#### TABLE 30-51: ECANx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       | $\leq$ +85°C for Industrial |

|--------------------|--------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                  |

| CA10               | TIOF   | Port Output Fall Time                        | —                                                     | _                   |      | ns    | See Parameter DO32          |

| CA11               | TioR   | Port Output Rise Time                        | —                                                     | —                   | _    | ns    | See Parameter DO31          |

| CA20               | TCWF   | Pulse Width to Trigger<br>CAN Wake-up Filter | 120                                                   |                     | _    | ns    |                             |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

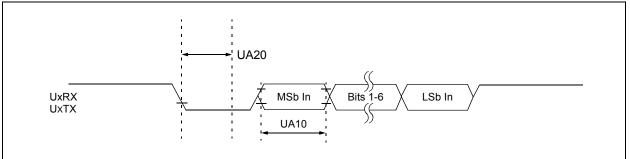

#### **FIGURE 30-35: UARTX MODULE I/O TIMING CHARACTERISTICS**

#### TABLE 30-52: UARTX MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS                                |         |                                                   |       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature -40°C $\leq$ TA $\leq$ +125°C |      |       |            |  |

|---------------------------------------------------|---------|---------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param<br>No. Symbol Characteristic <sup>(1)</sup> |         |                                                   | Min.  | Тур. <sup>(2)</sup>                                                                                                          | Max. | Units | Conditions |  |

| UA10                                              | TUABAUD | UARTx Baud Time                                   | 66.67 |                                                                                                                              | _    | ns    |            |  |

| UA11                                              | FBAUD   | UARTx Baud Frequency                              | —     |                                                                                                                              | 15   | Mbps  |            |  |

| UA20                                              | TCWF    | Start Bit Pulse Width to Trigger<br>UARTx Wake-up | 500   | _                                                                                                                            |      | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |                |           |      |  |

|--------------------------|-------------|----------------|-----------|------|--|

| D                        | MIN         | NOM            | MAX       |      |  |

| Number of Leads          | N           |                | 64        |      |  |

| Lead Pitch               | е           |                | 0.50 BSC  |      |  |

| Overall Height           | А           | -              | -         | 1.20 |  |

| Molded Package Thickness | A2          | 0.95           | 1.00      | 1.05 |  |

| Standoff                 | A1          | 0.05           | -         | 0.15 |  |

| Foot Length              | L           | 0.45           | 0.60      | 0.75 |  |

| Footprint                | L1          | 1.00 REF       |           |      |  |

| Foot Angle               | φ           | 0° 3.5° 7°     |           |      |  |

| Overall Width            | E           |                | 12.00 BSC |      |  |

| Overall Length           | D           |                | 12.00 BSC |      |  |

| Molded Package Width     | E1          |                | 10.00 BSC |      |  |

| Molded Package Length    | D1          |                | 10.00 BSC |      |  |

| Lead Thickness           | С           | 0.09 – 0.20    |           |      |  |

| Lead Width               | b           | 0.17 0.22 0.27 |           |      |  |

| Mold Draft Angle Top     | α           | 11° 12° 13°    |           |      |  |

| Mold Draft Angle Bottom  | β           | 11°            | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B