Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504t-e-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

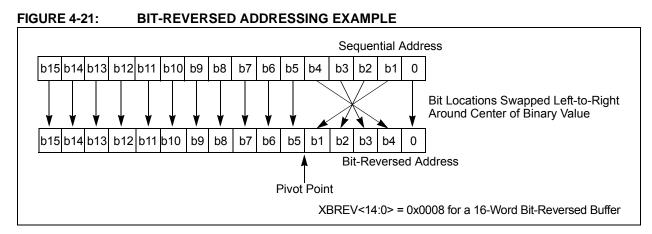

# TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |

| R/W-0         | R/W-0                                  | U-0                                                                                                                                                                       | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |  |  |  |  |  |

|---------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|--|--|--|--|--|

| TRAPF         | R IOPUWR                               | —                                                                                                                                                                         | _             | VREGSF                | —                 | CM               | VREGS         |  |  |  |  |  |

| bit 15        |                                        |                                                                                                                                                                           |               |                       |                   |                  | bit 8         |  |  |  |  |  |

| <b>D</b> 4440 |                                        | DANIO                                                                                                                                                                     | DAA/ O        | DAMA                  | DAMO              |                  |               |  |  |  |  |  |

| R/W-0         |                                        | R/W-0                                                                                                                                                                     | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |  |

| EXTR<br>bit 7 | SWR                                    | SWDTEN <sup>(2)</sup>                                                                                                                                                     | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |  |  |  |  |  |

|               |                                        |                                                                                                                                                                           |               |                       |                   |                  | bit (         |  |  |  |  |  |

| Legend:       |                                        |                                                                                                                                                                           |               |                       |                   |                  |               |  |  |  |  |  |

| R = Reada     | able bit                               | W = Writable I                                                                                                                                                            | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |  |  |  |  |  |

| -n = Value    | at POR                                 | '1' = Bit is set                                                                                                                                                          |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |  |  |  |  |  |

|               |                                        |                                                                                                                                                                           |               |                       |                   |                  |               |  |  |  |  |  |

| bit 15        | •                                      | TRAPR: Trap Reset Flag bit                                                                                                                                                |               |                       |                   |                  |               |  |  |  |  |  |

|               |                                        | <ul> <li>1 = A Trap Conflict Reset has occurred</li> <li>0 = A Trap Conflict Reset has not occurred</li> </ul>                                                            |               |                       |                   |                  |               |  |  |  |  |  |

| bit 14        | •                                      |                                                                                                                                                                           |               |                       | et Flag bit       |                  |               |  |  |  |  |  |

|               |                                        | <b>IOPUWR:</b> Illegal Opcode or Uninitialized W Access Reset Flag bit<br>1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as an |               |                       |                   |                  |               |  |  |  |  |  |

|               |                                        | Pointer caused                                                                                                                                                            |               |                       |                   |                  |               |  |  |  |  |  |

|               | -                                      | l opcode or Uni                                                                                                                                                           |               | egister Reset h       | as not occurred   | d                |               |  |  |  |  |  |

| bit 13-12     | -                                      | ted: Read as '                                                                                                                                                            |               |                       | . 1.9             |                  |               |  |  |  |  |  |

| bit 11        |                                        | ash Voltage Reg                                                                                                                                                           |               |                       | p bit             |                  |               |  |  |  |  |  |

|               |                                        | <ul> <li>1 = Flash voltage regulator is active during Sleep</li> <li>0 = Flash voltage regulator goes into Standby mode during Sleep</li> </ul>                           |               |                       |                   |                  |               |  |  |  |  |  |

| bit 10        |                                        | ted: Read as '                                                                                                                                                            | -             | ,,                    | 5                 |                  |               |  |  |  |  |  |

| bit 9         | CM: Configur                           | ation Mismatch                                                                                                                                                            | Flag bit      |                       |                   |                  |               |  |  |  |  |  |

|               | 1 = A Configu                          | uration Mismatc<br>uration Mismatc                                                                                                                                        | h Reset has   |                       |                   |                  |               |  |  |  |  |  |

| bit 8         | VREGS: Volta                           | VREGS: Voltage Regulator Standby During Sleep bit                                                                                                                         |               |                       |                   |                  |               |  |  |  |  |  |

|               | •                                      | egulator is active<br>egulator goes in                                                                                                                                    | •             | •                     | еер               |                  |               |  |  |  |  |  |

| bit 7         | EXTR: Extern                           | EXTR: External Reset (MCLR) Pin bit                                                                                                                                       |               |                       |                   |                  |               |  |  |  |  |  |

|               |                                        | 1 = A Master Clear (pin) Reset has occurred<br>0 = A Master Clear (pin) Reset has not occurred                                                                            |               |                       |                   |                  |               |  |  |  |  |  |

| bit 6         | SWR: Softwa                            | re RESET (Instr                                                                                                                                                           | uction) Flag  | bit                   |                   |                  |               |  |  |  |  |  |

|               |                                        | instruction has instruction has                                                                                                                                           |               |                       |                   |                  |               |  |  |  |  |  |

| bit 5         | SWDTEN: So                             | oftware Enable/                                                                                                                                                           | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |  |  |  |  |  |

|               | 1 = WDT is e<br>0 = WDT is di          |                                                                                                                                                                           |               |                       |                   |                  |               |  |  |  |  |  |

| bit 4         | WDTO: Watc                             | hdog Timer Tim                                                                                                                                                            | e-out Flag bi | it                    |                   |                  |               |  |  |  |  |  |

|               |                                        | e-out has occur<br>e-out has not oc                                                                                                                                       |               |                       |                   |                  |               |  |  |  |  |  |

| Note 1:       | All of the Reset sta cause a device Re |                                                                                                                                                                           | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |  |  |  |  |  |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir  | onfiguration bit i                                                                                                                                                        | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |  |  |  |  |  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                   | R/W-0    | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------------------------------------------------------------------|----------|-------|------------------------------------|--------|-------|-------|-------|--|--|--|--|

|                                                                         |          |       | PAD                                | <15:8> |       |       |       |  |  |  |  |

| bit 15                                                                  |          |       |                                    |        |       |       | bit 8 |  |  |  |  |

|                                                                         |          |       |                                    |        |       |       |       |  |  |  |  |

| R/W-0                                                                   | R/W-0    | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|                                                                         | PAD<7:0> |       |                                    |        |       |       |       |  |  |  |  |

| bit 7                                                                   |          |       |                                    |        |       |       | bit 0 |  |  |  |  |

|                                                                         |          |       |                                    |        |       |       |       |  |  |  |  |

| Legend:                                                                 |          |       |                                    |        |       |       |       |  |  |  |  |

| R = Readable bit W = Writable bit                                       |          |       | U = Unimplemented bit, read as '0' |        |       |       |       |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |          |       |                                    | nown   |       |       |       |  |  |  |  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0               | U-0   | R/W-0            | R/W-0                                | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|--------------------------------------|-------------------|------------------|--------------------|-------|--|

| —                 |       |                  |                                      | CNT<              | 13:8> <b>(2)</b> |                    |       |  |

| bit 15            |       |                  |                                      |                   |                  |                    | bit 8 |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0                                | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|                   |       |                  | CNT<                                 | <7:0> <b>(2)</b>  |                  |                    |       |  |

| bit 7             |       |                  |                                      |                   |                  |                    | bit 0 |  |

| Legend:           |       |                  |                                      |                   |                  |                    |       |  |

| -                 |       | W = Writable b   | = Writable bit U = Unimplemented bit |                   |                  | id as '0'          |       |  |

| -n = Value at POR |       | '1' = Bit is set |                                      | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

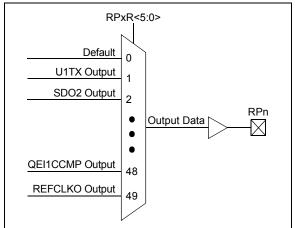

## 11.4.4.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

## 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

#### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                                                          | RPxR<5:0> | Output Name                                   |

|-------------------------------------------------------------------|-----------|-----------------------------------------------|

| Default PORT                                                      | 000000    | RPn tied to Default Pin                       |

| U1TX                                                              | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                                                              | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                                                              | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                                                              | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                                                               | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>                                               | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                                                               | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                                                               | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                                                               | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                                                               | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                                                             | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                                                             | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                                                             | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>                                             | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup>                                           | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO         110001         RPn tied to Reference Clock Output |           | RPn tied to Reference Clock Output            |

| C4OUT                                                             | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

# REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                       | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|--------------|--------------|-------------------------------------------------------------|---------------|----------------------|-----------------|-----------------|--------|--|--|--|--|

| _            |              |                                                             |               | HOME1R<6:0           | >               |                 |        |  |  |  |  |

| bit 15       |              |                                                             |               |                      |                 |                 | bit 8  |  |  |  |  |

|              |              | <b>D</b> # 4 4 0                                            | 54446         | 5444.0               | 5444.0          |                 | 5444.6 |  |  |  |  |

| U-0          | R/W-0        | R/W-0                                                       | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|              |              |                                                             |               | INDX1R<6:0>          | >               |                 |        |  |  |  |  |

| bit 7        |              |                                                             |               |                      |                 |                 | bit C  |  |  |  |  |

| Legend:      |              |                                                             |               |                      |                 |                 |        |  |  |  |  |

| R = Readab   | le bit       | W = Writable                                                | bit           | U = Unimplen         | nented bit, rea | ad as '0'       |        |  |  |  |  |

| -n = Value a | t POR        | '1' = Bit is set                                            |               | '0' = Bit is cleared |                 | x = Bit is unkr | nown   |  |  |  |  |

|              |              | nput tied to RPI                                            |               |                      |                 |                 |        |  |  |  |  |

|              |              | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss |               |                      |                 |                 |        |  |  |  |  |

| bit 7        |              | nted: Read as '                                             |               |                      |                 |                 |        |  |  |  |  |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI      | selection nun | ,                    | responding RI   | Pn Pin bits     |        |  |  |  |  |

|              |              | nput tied to CM                                             |               |                      |                 |                 |        |  |  |  |  |

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                                                                                     | R/W-0                                  | R/W-0             | R/W-0             | R/W-0                  | U-0             | R/W-0         |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|-------------------|------------------------|-----------------|---------------|--|--|

|               | 0-0                                                                                                                                                                     | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0                |                 | ENFLTB        |  |  |

| <br>bit 15    |                                                                                                                                                                         | COOIDE                                 |                   | OUTOLLI           | OUTOLLU                |                 | bit 8         |  |  |

| Sit 10        |                                                                                                                                                                         |                                        |                   |                   |                        |                 | bit 0         |  |  |

| R/W-0         | U-0                                                                                                                                                                     | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0           | R/W-0         |  |  |

| ENFLT         |                                                                                                                                                                         | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2                   | OCM1            | OCM0          |  |  |

| bit 7         |                                                                                                                                                                         |                                        |                   |                   |                        |                 | bit 0         |  |  |

|               |                                                                                                                                                                         |                                        |                   |                   |                        |                 |               |  |  |

| Legend:       |                                                                                                                                                                         | HSC = Hardw                            | are Settable/Cl   | earable bit       |                        |                 |               |  |  |

| R = Read      | able bit                                                                                                                                                                | W = Writable I                         | oit               | U = Unimplem      | nented bit, read       | as '0'          |               |  |  |

| -n = Value    | e at POR                                                                                                                                                                | '1' = Bit is set                       |                   | '0' = Bit is clea | ared                   | x = Bit is unkn | own           |  |  |

|               |                                                                                                                                                                         |                                        |                   |                   |                        |                 |               |  |  |

| bit 15-14     | Unimplemen                                                                                                                                                              | ted: Read as 'o                        | )'                |                   |                        |                 |               |  |  |

| bit 13        | OCSIDL: Out                                                                                                                                                             | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                        |                 |               |  |  |

|               |                                                                                                                                                                         | ompare x Halts                         |                   |                   |                        |                 |               |  |  |

|               | •                                                                                                                                                                       | compare x conti                        | •                 |                   | ode                    |                 |               |  |  |

| bit 12-10     |                                                                                                                                                                         | )>: Output Com                         | pare x Clock S    | elect bits        |                        |                 |               |  |  |

|               | 111 = Periph<br>110 = Reserv                                                                                                                                            | eral clock (FP)                        |                   |                   |                        |                 |               |  |  |

|               | 101 = PTGO                                                                                                                                                              |                                        |                   |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | is the clock so                        |                   |                   | hronous clock          | is supported)   |               |  |  |

|               |                                                                                                                                                                         | is the clock so                        |                   |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | ( is the clock so<br>( is the clock so |                   |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | is the clock so                        |                   |                   |                        |                 |               |  |  |

| bit 9         | Unimplemen                                                                                                                                                              | ted: Read as '0                        | )'                |                   |                        |                 |               |  |  |

| bit 8         | ENFLTB: Fau                                                                                                                                                             | ult B Input Enab                       | le bit            |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | compare Fault B<br>compare Fault B     |                   |                   |                        |                 |               |  |  |

| bit 7         | -                                                                                                                                                                       | ult A Input Enab                       |                   |                   |                        |                 |               |  |  |

|               | 1 = Output C                                                                                                                                                            | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                        |                 |               |  |  |

| bit 6         | •                                                                                                                                                                       | ted: Read as '0                        | • • •             |                   |                        |                 |               |  |  |

| bit 5         | OCFLTB: PW                                                                                                                                                              | M Fault B Con                          | dition Status bit |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | ult B condition of Fault B condition   |                   |                   |                        |                 |               |  |  |

| bit 4         |                                                                                                                                                                         | FLTA: PWM Fault A Condition Status bit |                   |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         | ult A condition o                      |                   |                   |                        |                 |               |  |  |

| Note 1:       | OCxR and OCxF                                                                                                                                                           | 29 are double h                        | uffered in D\\//  | / mode only       |                        |                 |               |  |  |

| Note 1.<br>2: |                                                                                                                                                                         |                                        |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin  | heral Trigger |  |  |

| 2.            | <ol> <li>Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger<br/>Generator (PTG) Module" for more information.</li> </ol> |                                        |                   |                   |                        |                 |               |  |  |

|               | PTGO4 = OC1                                                                                                                                                             | -                                      |                   |                   |                        |                 |               |  |  |

|               | PTG05 = 0C2                                                                                                                                                             |                                        |                   |                   |                        |                 |               |  |  |

|               | PTGO6 = OC3<br>PTGO7 = OC4                                                                                                                                              |                                        |                   |                   |                        |                 |               |  |  |

|               |                                                                                                                                                                         |                                        |                   |                   |                        |                 |               |  |  |

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | ; FLT32 pin must be pulled low externally in order to clear and disable the fault<br>; Writing to FCLCON1 register requires unlock sequence                                                                                                                                                       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |  |  |  |  |  |  |  |  |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |  |  |  |  |  |  |  |  |

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0                                | U-0   | R/W-0 | R/W-0 | R/W-0                                   | R/W-0  | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|--------|-------|-------|--|--|

| —                                  | —     |       |       | DTR)                                    | <13:8> |       |       |  |  |

| bit 15                             |       |       |       |                                         |        |       | bit 8 |  |  |

|                                    |       |       |       |                                         |        |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0  | R/W-0 | R/W-0 |  |  |

|                                    |       |       | DTR   | x<7:0>                                  |        |       |       |  |  |

| bit 7                              |       |       |       |                                         |        |       | bit 0 |  |  |

|                                    |       |       |       |                                         |        |       |       |  |  |

| Legend:                            |       |       |       |                                         |        |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |        |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |        |       |       |  |  |

# REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                                                                  | U-0   | R/W-0            | R/W-0         | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|----------------------------------------------------------------------|-------|------------------|---------------|-------------------|-------|-----------------|-------|--|--|--|--|

| _                                                                    | _     |                  | ALTDTRx<13:8> |                   |       |                 |       |  |  |  |  |

| bit 15 b                                                             |       |                  |               |                   |       |                 |       |  |  |  |  |

|                                                                      |       |                  |               |                   |       |                 |       |  |  |  |  |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0         | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|                                                                      |       |                  | ALTDT         | Rx<7:0>           |       |                 |       |  |  |  |  |

| bit 7                                                                |       |                  |               |                   |       |                 | bit 0 |  |  |  |  |

|                                                                      |       |                  |               |                   |       |                 |       |  |  |  |  |

| Legend:                                                              |       |                  |               |                   |       |                 |       |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |               |                   |       |                 |       |  |  |  |  |

| -n = Value at F                                                      | POR   | '1' = Bit is set |               | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INDXF | ILD<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

# REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

# REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                              | R/W-0          | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |

|------------------------------------|----------------|----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|                                    |                | QEIIC                            | <31:24>                                 |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                    |                |                                  |                                         |                                                                                       |                                                                                                                                                            | bit 8                                                                                         |

|                                    |                |                                  |                                         |                                                                                       |                                                                                                                                                            |                                                                                               |

| R/W-0                              | R/W-0          | R/W-0                            | R/W-0                                   | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |

|                                    |                | QEIIC                            | <23:16>                                 |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                    |                |                                  |                                         |                                                                                       |                                                                                                                                                            | bit 0                                                                                         |

|                                    |                |                                  |                                         |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                    |                |                                  |                                         |                                                                                       |                                                                                                                                                            |                                                                                               |

| it                                 | W = Writable b | bit                              | U = Unimplemented bit, read as '0'      |                                                                                       |                                                                                                                                                            |                                                                                               |

| -n = Value at POR '1' = Bit is set |                |                                  | '0' = Bit is cleared x = Bit is unknown |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                    | R/W-0          | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC     | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplem | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>            it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | QEII  | C<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | QEI   | C<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit C |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

# 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                                        | R/W-0                                                 | R/W-0                                                              | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------------------|-----------------|--------|

| —               | —                                                                                                                          | CSIDL                                                 | ABAT                                                               | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit 8  |

| R-1             | R-0                                                                                                                        | R-0                                                   | U-0                                                                | R/W-0                          | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1                                                                                                                    | OPMODE0                                               | _                                                                  | CANCAP                         |                  |                 | WIN    |

| bit 7           |                                                                                                                            |                                                       |                                                                    |                                |                  |                 | bit (  |

| Legend:         |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |

| R = Readable    | bit                                                                                                                        | W = Writable I                                        | bit                                                                | U = Unimpler                   | mented bit, read | l as '0'        |        |

| -n = Value at F | POR                                                                                                                        | '1' = Bit is set                                      |                                                                    | '0' = Bit is cle               | ared             | x = Bit is unkr | nown   |

|                 |                                                                                                                            |                                                       |                                                                    |                                |                  |                 |        |