Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

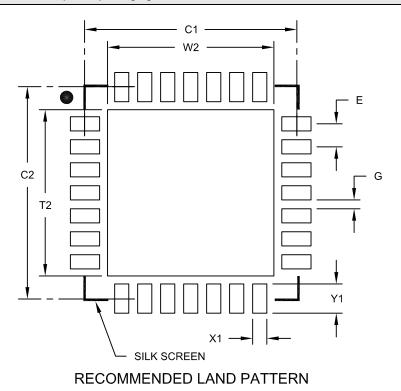

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp504t-i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

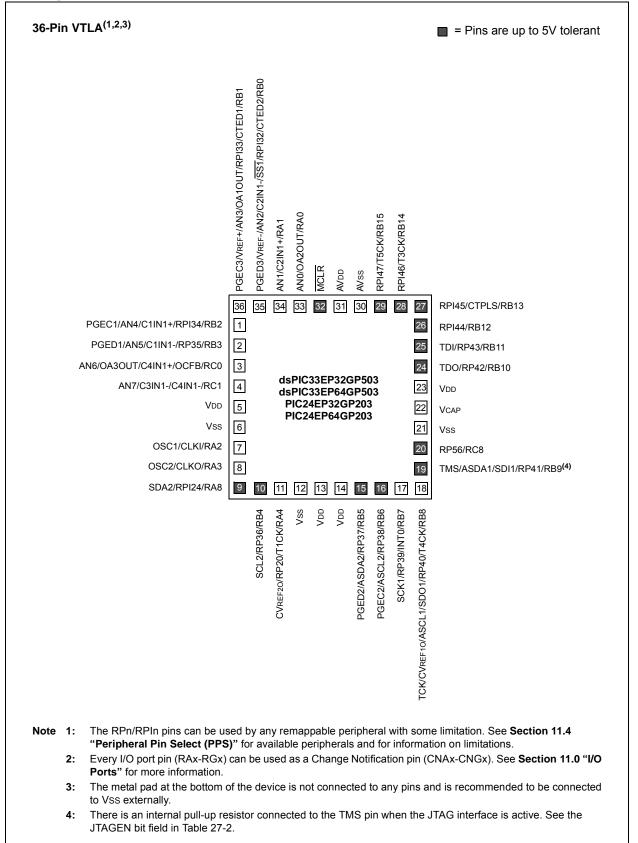

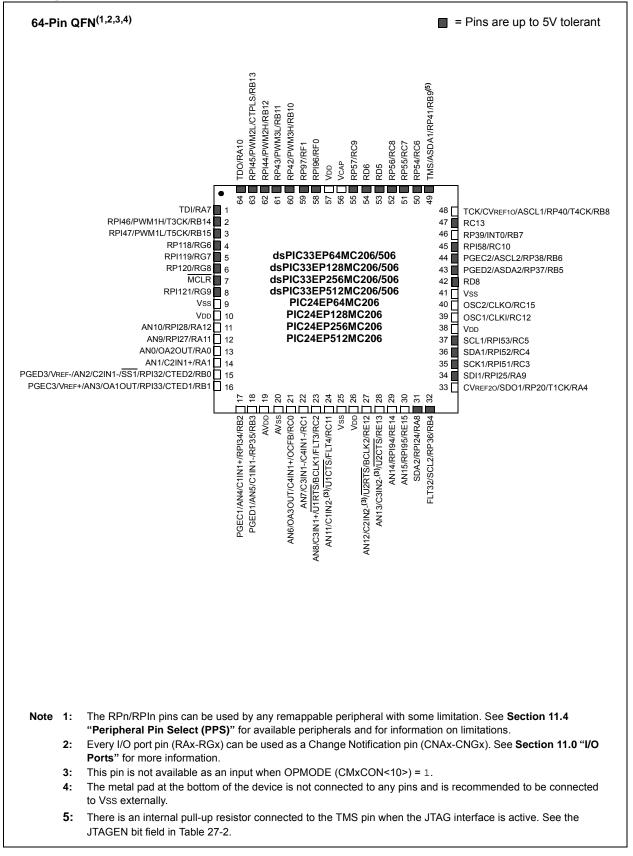

#### **Pin Diagrams (Continued)**

### Pin Diagrams (Continued)

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

| R/W-0           | R/W-0                                                                                                                                                 | R/W-1                        | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                                                                  | DOZE1 <sup>(1)</sup>         | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |  |  |  |

| bit 15          |                                                                                                                                                       |                              | •                    |                        |                    |                 | bit 8     |  |  |  |  |  |  |

|                 |                                                                                                                                                       |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

| R/W-0           | R/W-1                                                                                                                                                 | U-0                          | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                                                                              | —                            | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |  |  |  |

| bit 7           |                                                                                                                                                       |                              |                      |                        |                    |                 | bit (     |  |  |  |  |  |  |

|                 |                                                                                                                                                       |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

| Legend:         |                                                                                                                                                       |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

| R = Readable    |                                                                                                                                                       | W = Writable                 |                      | -                      | nented bit, read   |                 |           |  |  |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                   | '1' = Bit is set             |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |  |  |  |

| h:+ 45          |                                                                                                                                                       | on Interview h               |                      |                        |                    |                 |           |  |  |  |  |  |  |

| bit 15          | ROI: Recover on Interrupt bit                                                                                                                         |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | <ol> <li>I = Interrupts will clear the DOZEN bit</li> <li>Interrupts have no effect on the DOZEN bit</li> </ol>                                       |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

| bit 14-12       | •                                                                                                                                                     |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | DOZE<2:0>: Processor Clock Reduction Select bits <sup>(1)</sup><br>111 = Fcy divided by 128                                                           |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 110 = Fcy divided by 64                                                                                                                               |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 101 = FCY divided by 32                                                                                                                               |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 100 = Fcy divided by 16<br>011 = Fcy divided by 8 (default)                                                                                           |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 010 = FcY divided by 4                                                                                                                                |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 001 = Fcy divided by 2                                                                                                                                |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 000 = Fcy div                                                                                                                                         | •                            |                      |                        |                    |                 |           |  |  |  |  |  |  |

| bit 11          | <b>DOZEN:</b> Doze Mode Enable bit <sup>(2,3)</sup><br>1 = DOZE<2:0> field specifies the ratio between the peripheral clocks and the processor clocks |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 |                                                                                                                                                       |                              |                      |                        |                    | nd the process  | or clocks |  |  |  |  |  |  |

|                 |                                                                                                                                                       | -                            | -                    | ratio is forced to     |                    |                 |           |  |  |  |  |  |  |

| bit 10-8        |                                                                                                                                                       |                              | RC Oscillator        | r Postscaler bit       | S                  |                 |           |  |  |  |  |  |  |

|                 | 111 = FRC divided by 256<br>110 = FRC divided by 64                                                                                                   |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 101 = FRC divided by 64                                                                                                                               |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 100 = FRC divided by 16                                                                                                                               |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 011 = FRC divided by 8                                                                                                                                |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 010 = FRC divided by 4<br>001 = FRC divided by 2                                                                                                      |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 |                                                                                                                                                       | vided by 2<br>vided by 1 (de | fault)               |                        |                    |                 |           |  |  |  |  |  |  |

| bit 7-6         |                                                                                                                                                       |                              | -                    | r Select bits (al      | so denoted as      | 'N2', PLL posts | caler)    |  |  |  |  |  |  |

|                 | PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)<br>11 = Output divided by 8                                   |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | 10 = Reserved                                                                                                                                         |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 |                                                                                                                                                       | livided by 4 (de             | efault)              |                        |                    |                 |           |  |  |  |  |  |  |

| bit 5           | 00 = Output d                                                                                                                                         | ted: Read as '               | o'                   |                        |                    |                 |           |  |  |  |  |  |  |

|                 | •                                                                                                                                                     |                              |                      |                        |                    |                 |           |  |  |  |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                                                                       |                              | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                                                                      | when the ROI I               | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |  |  |  |

|                 | DOJENUS                                                                                                                                               |                              |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |  |  |  |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

|                                    |     |                |                   |              | UNIRUL RE          |          |       |

|------------------------------------|-----|----------------|-------------------|--------------|--------------------|----------|-------|

| U-0                                | U-0 | U-0            | U-0               | U-0          | R/W-0              | U-0      | U-0   |

| —                                  | _   | —              | —                 | —            | CMPMD              | —        | —     |

| bit 15                             |     |                |                   |              |                    |          | bit 8 |

|                                    |     |                |                   |              |                    |          |       |

| R/W-0                              | U-0 | U-0            | U-0               | U-0          | U-0                | R/W-0    | U-0   |

| CRCMD                              | —   | —              | _                 | —            | —                  | I2C2MD   | —     |

| bit 7                              |     |                |                   |              |                    |          | bit C |

|                                    |     |                |                   |              |                    |          |       |

| Legend:                            |     |                |                   |              |                    |          |       |

| R = Readable                       | bit | W = Writable I | bit               | U = Unimplem | ented bit, read    | l as '0' |       |

| -n = Value at POR '1' = Bit is set |     |                | '0' = Bit is clea | ared         | x = Bit is unknown |          |       |

#### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     | —      | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |

| bit 15-5<br>bit 4                            | DMA0MD: DN<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DN<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DN<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DN<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |

| bit 3                                        |                                                                                                                                                                              | Module Disat<br>ule is disabled<br>ule is enabled                                                                                                                                                                            | ole bit                                                                                                                          |                                   |                          |                             |      |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   |       |       | RP42  | R<5:0> |       |       |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | W = Writable bit U = Unimplemented bit, read as '0'            |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ( | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit             | e bit U = Unimplemented bit, read as '0'                       |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0                               | U-0                       | U-0               | R/W-x                              | R/W-x            | R/W-x                        | R/W-x | R/W-x      |  |

|-----------------------------------|---------------------------|-------------------|------------------------------------|------------------|------------------------------|-------|------------|--|

|                                   | —                         | _                 | SID10                              | SID9             | SID8                         | SID7  | SID6       |  |

| bit 15                            |                           |                   |                                    |                  |                              |       | bit 8      |  |

| R/W-x                             | R/W-x                     | R/W-x             | R/W-x                              | R/W-x            | R/W-x                        | R/W-x | R/W-x      |  |

| SID5                              | SID4                      | SID3              | SID2                               | SID1             | SID0                         | SRR   | IDE        |  |

| bit 7                             |                           |                   |                                    |                  |                              |       | bit 0      |  |

| Legend:                           |                           |                   |                                    |                  |                              |       |            |  |

| R = Readable bit W = Writable bit |                           |                   | U = Unimplemented bit, read as '0' |                  |                              |       |            |  |

| -n = Value at                     | POR                       | '1' = Bit is set  |                                    | '0' = Bit is cle | '0' = Bit is cleared x = Bit |       | is unknown |  |

|                                   |                           |                   |                                    |                  |                              |       |            |  |

| bit 15-13                         | Unimplemen                | ted: Read as '    | כי                                 |                  |                              |       |            |  |

| bit 12-2                          | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits                           |                  |                              |       |            |  |

| bit 1                             | SRR: Substitu             | ute Remote Re     | quest bit                          |                  |                              |       |            |  |

|                                   | When IDE =                | 0:                |                                    |                  |                              |       |            |  |

|                                   | 1 = Message               | will request rer  | note transmis                      | ssion            |                              |       |            |  |

|                                   | 0 = Normal m              | nessage           |                                    |                  |                              |       |            |  |

|                                   | When IDE = 1              | <u>1:</u>         |                                    |                  |                              |       |            |  |

|                                   | The SRR bit r             | must be set to '  | 1'.                                |                  |                              |       |            |  |

| bit 0                             | IDE: Extende              | d Identifier bit  |                                    |                  |                              |       |            |  |

|                                   | 1 = Message               | will transmit Ex  | tended Ident                       | ifier            |                              |       |            |  |

|                                   | 0 = Message               | will transmit St  | andard Identi                      | fier             |                              |       |            |  |

|                                   |                           |                   |                                    |                  |                              |       |            |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                               | U-0   | U-0              | U-0                                | R/W-x            | R/W-x                | R/W-x | R/W-x              |  |

|-----------------------------------|-------|------------------|------------------------------------|------------------|----------------------|-------|--------------------|--|

| —                                 | —     | —                |                                    | EID17            | EID16                | EID15 | EID14              |  |

| bit 15                            |       |                  |                                    |                  |                      |       | bit 8              |  |

|                                   |       |                  |                                    |                  |                      |       |                    |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x            | R/W-x                | R/W-x | R/W-x              |  |

| EID13                             | EID12 | EID11            | EID10                              | EID9             | EID8                 | EID7  | EID6               |  |

| bit 7                             |       |                  |                                    |                  |                      |       | bit 0              |  |

|                                   |       |                  |                                    |                  |                      |       |                    |  |

| Legend:                           |       |                  |                                    |                  |                      |       |                    |  |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                  |                      |       |                    |  |

| -n = Value at POR '1' = Bi        |       | '1' = Bit is set |                                    | '0' = Bit is cle | '0' = Bit is cleared |       | x = Bit is unknown |  |

| L                                 |       |                  |                                    |                  |                      |       |                    |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                           | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|---------------------------------|------------------------------------|-----------------|-------|-------|

|                                    |       |       | PTGT0                           | _IM<15:8>                          |                 |       |       |

| bit 15                             |       |       |                                 |                                    |                 |       | bit 8 |

|                                    |       |       |                                 |                                    |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                           | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | PTGT0                           | LIM<7:0>                           |                 |       |       |

| bit 7                              |       |       |                                 |                                    |                 |       | bit 0 |

|                                    |       |       |                                 |                                    |                 |       |       |

| Legend:                            |       |       |                                 |                                    |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | bit                             | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR (1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is |                                    | x = Bit is unkr | nown  |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |

| bit 15 bit 8   |       |       |       |       |       |       |       |  |

|                |       |       |       |       |       |       |       |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| PTGT1LIM<7:0> |       |       |       |       |       |       |       |

| bit 7         |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

|                                  | U-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                      | R-0                                                                                                                | R-0                                                                     | R-0                                                | R-0             | R-0            |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|--|--|

| CRCEN                            | —                                                                                                                                                                                                                                                            | CSIDL                                                                                                                                                                                                                                                      | VWORD4                                                                                                             | VWORD3                                                                  | VWORD2                                             | VWORD1          | VWORD0         |  |  |

| bit 15                           | •                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                          |                                                                                                                    |                                                                         |                                                    |                 | bit 8          |  |  |

| R-0                              | R-1                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                                                                                              | R/W-0                                                                   | U-0                                                | U-0             | U-0            |  |  |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                       | CRCISEL                                                                                                                                                                                                                                                    | CRCGO                                                                                                              | LENDIAN                                                                 | _                                                  | _               | —              |  |  |

| bit 7                            |                                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                          |                                                                                                                    |                                                                         |                                                    |                 | bit (          |  |  |

| Legend:                          |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                            |                                                                                                                    |                                                                         |                                                    |                 |                |  |  |

| R = Readable                     | e bit                                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                               | bit                                                                                                                | U = Unimplen                                                            | nented bit, read                                   | 1 as '0'        |                |  |  |

| -n = Value at                    | POR                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                           |                                                                                                                    | '0' = Bit is cle                                                        | ared                                               | x = Bit is unkr | nown           |  |  |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                   | dule is enabled                                                                                                                                                                                                                                            |                                                                                                                    | chines, pointer                                                         | s and CRCWD                                        | AT/CRCDAT a     | re reset, othe |  |  |